Lecture-4-Modular Combinational Logic.ppt

Transcript of Lecture-4-Modular Combinational Logic.ppt

1

The University of Texas at Arlington

More Complex Combinational Circuits

CSE 2340/2140 – Introduction to Digital LogicDr. Gergely Záruba

DECODERS

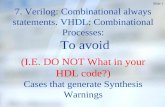

2

2

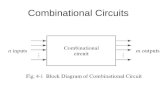

More Complex Combinational Devices

• Last lecture we have briefly seen a list of available combinational devices for circuit design engineers, many of which were not simple gates.

• By now, we know how we can use gates to create switching logic for switching functions; we can use several such functions for devices with more outputs.

• There is a natural question of what functions, i.e., what devices, could prove useful and thus could warrant single chip implementations. We can use such devices then as building blocks in our designs.

• We know from previous classes that ALUs in computers perform the arithmetic operations (i.e., combinational logic operations). What could be components of ALUs?

• We will look at:• Decoders (binary)

• Encoders

• Multiplexers

• Demultiplexers (really, decoders)

• Adders, subtractors

• Comparators

Decoders

• An n-to-2n decoder is a multiple-output combinational logic network with n input lines and 2n output signals,

• For each possible input condition, one and only one output signal will be ‘high’. Therefore, a decoder can be considered a minterm generator with each output corresponding to exactly one minterm.

LSB x0

x1

y0

y1

MSB

Decodern-to-2n

xn-1

y2n-1

3

m0

LSB A

MSB Bm0

LSB A

MSB B

Decoder Realization

m1

m2

m3

(a) (b)

m1

m2

m3

(c)

m1

m0

m2

m3

LSB A

MSB B

3-bit Parallel Decoder

4

3-bit Tree-Type Decoder

4-bit Dual Tre Decoder

5

“Enable” Control Inputs

• Decoders and other functional modules often include one or more enable inputs, which can be used to either inhibit (disable) the designated function or allow (enable) it to be performed Thedesignated function or allow (enable) it to be performed. The decoding function is inhibited by E=0 forcing all its outputs to the inactive ‘0’ state. Setting E=1 “turns on” the decoder, (an output of 1 indicates the presence of corresponding minterm).

x0

x1

y0

x0y0

(a) (b)

y1

y2

y3

x1

y2

E

Ey3

y1

Cascading Decoders

I0 x0y0 O0

I1

I2

0

x1

E

y2

y1

y3

O2

O3

O1

Use of 2-to-4 decoder modules to realize a 3-8 decoder

y0

y1

y3

y2

x0

x1

E

O4

O5

O6

O7

6

Cascading Decoders (cont’d)

I0 x0 y0

y

O0

O

Use of 2-to-4 decoder modules to realize a 4-16

I1

I2

I3

1

x0

x

x0

x1

x1

x1

E

E

E

y0

y0

y1

y1

y1

y2

y2

y2

y3

y3

y3

O4

O2

O

O5

O1

O3

O6

O7

decoder

x0

x0

x1

x1

E

E

y0

y0

y1

y1

y2

y2

y3

y3

O8

O12

O13

O9

O15

O10

O14

O11

Decoders and SOP Switching Functions

• Decoders (and an additional gate) may be used to realize switching functionsto realize switching functions.

• For minterms and active high outputs (on the dfecoder) use an additional OR gate. For minterms and active low outputs use an additional NAND gate.

• For maxterms and active high outputs use an• For maxterms and active high outputs use an additional NOR gate. For maxterms and active low outputs use an additional AND gate.

12

7

f(P, Q, X) = m0 + m1 + m4 + m6 + m7

PA

0

1P

A

0

1X

Q

(a) (b)

B

C f(Q, X, P)

2

3

4

5

6

7

X

QB

C f(Q, X, P)

2

3

4

5

6

7

0 0

13

(c) (d)

f(Q, X, P)

A

B

C f(Q, X, P)

1

2

3

4

5

6

7

P

X

Q

A

B

C

1

2

3

4

5

6

7

P

X

Q

Decoders for Device Addresses

• The use of decoders as address decoders in computer memory is an important application. p pp• In this application, each of the 2n devices (memory cells or I/O ports)

is assigned a unique n-bit binary number, or address. The decoder then decodes the address by activating one of 2n select lines to access one of the devices.

S Device 0

n-Bit address

S Device 1

S Device 2n - 1

A0

A1

x0

x1

An - 1xn - 1

E

Device accesscontrol signal

y0

y1

y2n - 1

S = select device

8

Standard 74138 Decoder Module

G1(6)

G2A(4) Enable Select

OutputsInputs

G2A

G2B(5)

A (1)

B

C

(2)

(3)

(15)

(14)

(13)

(12)

(11)

Y0

Y1

Y2

Y3

Y4

HHHHHHH

LLLLLLL

LLLLHHH

LLHHLLH

LHLHLHL

LHHHHHH

HLHHHHH

HHLHHHH

HHHLHHH

HHHHLHH

HHHHHLH

HHHHHHL

HHHH

HH

Enable Select

G1 G2* ABC Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

H

(10)

(9)

(7)

Y5

Y6

Y7

HL

LH x

H

H

H

HHH

HHH

HHH

HHH

HHH

HHH

HHH

LHH

(c)

G2* = G2A + G2B

Standard 74154 Decoder Module

G1

G20

1

3

2

4

5

6

7

8

A

B

12

9

10

11

13

15

14

C

D

A A B B C C D D

9

More Decoders

• There are other decoders than binary

• E.g., BCD decoder (similar),

• E.g., 7-segment display decodera

b

fDecimal

BCD codeDCBA Decimal digits0000000100100011

0123

D

0

1

2

3

17

c

d

e

g

BCDinput

Decimal

outputs

(a) (b)

0011010001010110011110001001

3456789

C

B

A

3

4

5

6

78

9

ENCODERS

18

10

Encoders

• An encoder is a combinational logic module that assigns a unique output code for each input signal.a unique output code for each input signal.

• If an encoder has n inputs, the number of outputs s must satisfy the expression s >= log2n

• If the inputs are mutually exclusive then this is trivial.

• If not there are choices: if input is invalid, set output to zero, signal that it is invalid, or pick the smallest or largest of the inputs (priority encoder) to be encoded orlargest of the inputs (priority encoder) to be encoded, or just do something unpredictable (easiest, as some minterms become don’t cares).

19

Simple 4-to-2 Encoder

X3 X2 X1 X0 A1 A0

0 0 0 0 d d

A1

0 4 12 8

1 5 13 9

x3

11 ddX0

A0000000011

0000111100

0011001100

0101010101

d00d1ddd1d

d01d0ddd1d

A0

0 4 12 8

X3

1 5 13 9

3 7 15 11

2 6 14 10

x2

x0

x1

0

0

d d

d d

d d

d

d dd

A1 = X2 + X3

4-to-2Encoder

(a)

X1

X2

X3

A0

A1

4-to-2Encoder

Functional Diagram

20(b)

111111

001111

110011

010101

dddddd

dddddd

0 4 12 8

1 5 13 9

3 7 15 11

2 6 14 10

X2

X0

X1

(c)

1

10

0

d d

d d

d d

d

d

d d

d

d

A0 = X1 + X3

(d)

X1

X3

X2

X3

A0

A1

Truth tablesK-maps

Logic Diagram

11

Priority Encoders

• Pick highest value input line.• EO =1 indicates no input line is active; GS =1 indicates one or more inputs are activep ; p

X3 X2 X1 X0 A1 A0

000000

000011

001100

010101

000011

001100

GS EO

011111

100000

OutputsInputs A1

0 4 12 8

1 5 13 9

3 7 15 11

2 6 14 10

x2

x0

x3

x1

11

1 1

1 1

1

1

1

1 11

A1 = X2 + X3

4-to-2Priorityencoder

x0

x1

x2

x3

A0

A1

GSEO

4-to-2priorityencoder

0011111111

1100001111

1100110011

0101010101

1111111111

0011111111

1111111111

0000000000

A0

00 01 11 100 4 12 8

1 5 13 9

3 7 15 11

2 6 14 10

00

01

11

10

x2

x0

x3

x1

1

1

1 1

1 1

1

1

1 1

1 2 3

A0 = X3 + X1X2

x0

x1

x2

x3A0

GS

EO

A1

x2

74147 Standard MSI Encoders

• 74147 10-to-4 active-low priority encoder1

4

5

A

B

2

3

22

6

7

8

9

C

D

12

74148 Standard MSI Encoders

• 74148 8-to-3 active-low priority encoder0

EO

4

A0

A1

1

2

3

GS

23

5

6

7

El

A2

MULTIPLEXERS (DATA SELECTORS)

24

13

Multiplexers/Data Selectors

• A multiplexer, also called a data selector, is a modular device that selects one of many input lines to appear ondevice that selects one of many input lines to appear on a single output line.

• In a n-to-1 line multiplexer, one of the n input data lines (Dn-1, Dn-2,……..D0) is designated for connection to the single output line (Y) by a selection code.

4-to-1 Multiplexer

Y4-to-1

Multiplexer

D0

D1

B A YYMultiplexer

B A

D2

D3

Selection code

0011

0101

D0

D1

D2

D3

D0D0

Truth tableFunctional diagram

26

0 1 2 3

2-to-4Decoder

D1

D2

D3

B A

Y Y

(d)

D1

D2

D3

B ALogic diagram

Equivalent two-level circuit

14

Tree Type 16-to-1 Multiplexer

Y

I0

I1

I

D0

D1

D

Inputlines

Firstlevel

B A

I2

I3

D2

D3

Y

B A

I4

I5

I6

I7

Y

I8

I9

I

Y

B A

Output line

Secondlevel

S S

Z

D0

D1

D2

D3

D1

D0

D2

D3

D0

D1

D2

27

B A

I10

I11

Y

B A

I12

I13

I14

I15

S3 S2

Selection code(higher-order bits)

S1 S0

Selection code(lower-order bits)

2

D3

D0

D1

D2

D3

74151A 8-to-1 Multiplexer with Strobe

GStrobe

Output Y

Output W

Genable

D0

D1

D2

D3

D4

D5

Strobe

Inputs OutputsSelect

C GAB

LL

LH

HLL

LD0D1

Y W

HD0D1

xLL

xx'151A

0

28

CA BA B C

D6

D7

(c)

A

B

C

HHLLHH

LHLHLH

LLLLLL

D2D3D4D5D6D7

D2D3D4D5D6D7

LLHHHH

(b) (d)

1

2

3

4

5

6

7

G

ABC

Y

W

Generic Logic SymbolTruth TableLogic Diagram

15

74150 16-to-1 Multiplexer G1Strobe

enable

E0

E1

Output

W

E2

E3

E4

E5

E6

E7

E8

E9

E10

29

(c)D

C

B

A

AA B C

0

E11

E12

E13

E14

E15

D B

C D

74157 Quadruple 2-to-1 Multiplexer

1A

Inputs Output

DataStrobe Select1Y

2Y

3Y

1B

2A

2B

3A

3B

G S

HLLLL

LLHH

LH

LH

LLHLH

A B Y

(b)

'157

1A

1B

2A

2B

(2)

(3)

(5)

(6)

(11)

(4)

(7)

1Y

2Y

(15)

(1)A/B

EN

MUX

G1

1

1

G

Vcc Strobe 4ZA 4BOutput

4Y 3A 3B

16 15 14 13 12 11 10 9

InputsInputsOutput

3Y

30

Strobe G

Select S

4Y

4A

4B

3A

3B

4A

4B

(11)

(10)

(14)

(13)

(9)

(12)

3Y

4Y

1ASelect 1B 2A1COutput

2B

7654321

2YOutput

8

GND

Inputs Inputs

G 4A 4B 4Y 3A 3B

3Y

1A 1B 1Y 2A 2B 2Y

S

(a)

16

Using Multiple 74157-s

Source X

D7-D0Source W

D7 D0D7-D0 D7-D0

0

D7-D4D3-D0

4Y-1Y

S l t

4

4A-1A 4B-1BG

S74157

4A-1A 4B-1BG

S74157

444

0

88 D3-D0

D7-D4

44

4Y-1Y

31

Select0 = X1 = W

D7-D0

Destination

8D7-D4 D3-D0

8-bit two-input multiplexer 4-bit four-input multiplexer

Multiplexers for Switching Function Implementation

• The multiplexers presented so far can be used to implement switching functions. The idea is to use the selection code to generate the minterms of th f ti d t th d t li D t bl th i t t ithe function, and to use the data lines Di to enable the minterms present in a specific case.

• E.g., f(x1, x2, x3) = ∑m(0, 2, 3, 5)

C AB Y

fx1 x3x2

01

00

00

01

10

D0 = 1D1 = 0

iVCC

74151A

D0

D1

D2

234567

0001111

0110011

010101

0110100

1 0D2 = 1D3 = 1D4 = 0D5 = 1D6 = 0D7 = 0

x1x3x2

C B A

YW

f(x1, x2, x3)D3

D4

D5D6

D7G

Selection code

17

DEMULTIPLEXERS (DATA DISTRIBUTORS)

33

Demultiplexers

• A demultiplexer (Data Distributor) connects a single input line to one of n output lines, the specific output lineline to one of n output lines, the specific output line being determined by an s-bit selection code where 2s >= n.

Y0

Y11-to-nDemultiplexerInput Outputs

Y0

Y1

Y2

D

E

Input

Enable

Yn -1

1 2 S

Selectioncode

Y3

m0m1

m2 m3

AB

Selectioncode

2-to-4Decoder

1-to-4 Demux

18

Multiplexer-Demultiplexer System

E0

E

x0

x01

12

7415474150

x0x

87

Single datachannel (Q)

19

18

10Y

G1

G2

E1E2E3E4E5E6E7E8E9E10E11E12E

x1

x2x3

x4x5x6

x7x8x9

x10x11x12

123456789

101112

34567891011131415

Decoder/demultiplexerMultiplexer

7415474150x1x2x3

x4x5x6x7x8x9

x10x11x12x

7654321232221201918

35

16 lines

5 lines

23222120

D C AB

E13E14E15G

C3C2

C1

C0

12

x13x14

x15

12131415

151617

x13x14x15

D C AB

15141311

817169

ADDERS

36

19

Adding Binary (encoded) Numbers

• Addition can be performed with the same old algorithm we learned in elementary schools Goalgorithm we learned in elementary schools. Go from LSB to MSB and keep track of the carry.

• If we need to add more than two numbers we can divide that up into adding two and then adding the third to the sum of the two, etc.

• If we are adding two binary numbers then the• If we are adding two binary numbers, then the carry can only be 0 or 1.

37

Binary Half-adder

• When adding the LSBs, no carry is taken as input The circuit realizing this is a half adderinput. The circuit realizing this is a half-adder.

xi yi ci si

0011

0101

0001

0110

yi

xi

si

38

(b)

1 1 1 0

(c)

ci

Half adder propagation delays I nthe above configuration are not uniform

tadd = 3 tgate

tcarry = 2 tgate

20

Full-Adder

• In the next bits, we need to have a third input: the carry-in.in.

• From the truth table (shown in fig. 4.35e) we can show that si = xi yi ci-1

ci = xiyi + xici-1 + yici-1

xi yi ci-1

00

00

01

00

01

ci sisi

ci-1

yi

xi

(e)

0001111

0110011

1010101

0010111

1101001

(f)

ci

(g)ci-1

yi

xi

si

Ripple Carry Adder

• Here is our “algorithm”:y x y c x yx yn-1 c1

x1 y1 c0 x0 y0

z1 z0

cn-1

zn 1

FA HA

cn-2

xn-1

FA

40

z1 z0n-1

(end carry)zn

Half adder propagation delays Full adder propagation delaystadd = 3 tgate tadd = 3 tgate

tcarry = 2 tgate tcarry = 2 tgate

Ripple-Carry Adder (n-bits)tadd = (n - 1)2 tgate + 3 tgate = (2n + 1) tgate

21

Parallel Adders and Fast-Carry

• If we are not using our modular algorithm, faster adders can be created (parallel adders). The fastest adder design would be strictly parallel. That i ll th i t ld b li d i lt l d t th his, all the inputs would be applied simultaneously and propagate through two levels of logic to obtain the result. However, this approach is unrealistic for large number of bits because of the fan-in requirements.

• A Fast-carry (carry look-ahead) adder (74283)The image cannot be displayed. Your computer may not have enough memory to open the image, or the image may have been corrupted. Restart your computer, and then open the file again. If the red x still appears, you may have to delete the image and then insert it again.

41

Carry look-ahead

generator

Subtraction

• Recall: If we encode negative numbers in th i ht ( i th fl fthe right way (using the overflow of adders) then subtraction becomes the addition of a number and a negative number.

• Two-s complement is the solution. Two-sTwo s complement is the solution. Two s complement can be easily generated by flipping each bit and adding one to the result.

42

22

4-bit Adder/Subtractor Circuit

43

COMPARATORS

44

23

Comparators

• In general, a comparator can perform a magnitude comparison of two words A and B in either straightcomparison of two words A and B in either straight binary or BCD codes

• Thus, a comparator will generate three output signals:• f1 = 1 if A < B

• f 2 = 1 if A = B

• f3 =1 if A > B

• Therefore a comparator is a 2n-input 3-output• Therefore, a comparator is a 2n-input, 3-output combinational logic module.

Designing a 2-bit Comparator

A2 f1, A < B

0 4 12 8

f1, A < B A1

0 4 12 8

f2, A = B A1

A

B

Magnitudecomparator f2, A = B

f3, A > B2

i A1 A0

0123

0000

0000

0011

0101

0111

1000

0000

B1 B0 f1 f2 f3

1 5 13 9

3 7 15 11

2 6 14 10

1

1 1 1

1 1

B1

A0

B0

1 5 13 9

3 7 15 11

2 6 14 10B1

A0

B0

f3, A > BA1

1

1

1

1

46

3456789

101112131415

0000011111111

0111100001111

1001100110011

1010101010101

1001100010000

0010000100001

0100011001110

0 4 12 8

1 5 13 9

3 7 15 11

2 6 14 10

1

B1

A0

B0

11

1 1

1

24

Realizing a 2-bit Comparator

A1

B1

A0

f1

f3

47

B0

f2

7485 MSI Comparator

• The 7485 module is a 4-bit magnitude comparator (can be used to cascade higher order, e.g., 16-bit magnitude comparators)

Data inputs0 1 0

Vcc

16 15 14 13 12 11 10

7654321

9

8

GND

A3 B2 A2 B1A1 B0

B3

A0

A < BIn

A = BIn

A > BIn

A < BOut

A = BOut

A > BOut

Cascade inputs Cascade outputs

A < BIn

A = BIn

A > BIn

A < BOut

A = BOut

A > BOut

A3 B2 A2 B1A1 A0

B3 B0

Datainput

Comparingi

Cascadingi O

f2 f1f3

7485

Cascaded inputs

c2 c1c3

B1

B0

B2

B3

A1

A0

A2

A3

f2 f1f3

c2 c1c3

B5

B4

B6

B7

A5

A4

A6

A7

7485

C d d i t

48

A > B A < B A = B

inputs inputs Outputs

A3, B3 A2, B2 A1, B1 A0, B0

A2 > B2A2 < B2A2 = B2A2 = B2A2 = B2A2 = B2A2 = B2A2 = B2A2 = B2A2 = B2A2 = B2A2 = B2

A3 > B3A3 < B3A3 = B3A3 = B3A3 = B3A3 = B3A3 = B3A3 = B3A3 = B3A3 = B3A3 = B3A3 = B3A3 = B3A3 = B3

A1 > B1A1 < B1A1 = B1A1 = B1A1 = B1A1 = B1A1 = B1A1 = B1A1 = B1A1 = B1

A0 > B0A0 < B0A0 = B0A0 = B0A0 = B0A0 = B0A0 = B0A0 = B0

HLLHL

LHLHL

LLHLL

HLHLHLHLHLLLLH

LHLHLHLHLHLLLH

LLLLLLLLLLHHLL

A > B A < B A = B

A < B

A = B

A > B

Circuitoutputs

f2 f1f3

c2c1c3

B9

B8

B10

B11

A9

A8

A10

A11

7485

f2

f1

f3

c2c1c3

B13

B12

B14

B15

A13

A12

A14

A15

7485

Cascaded inputs

Cascaded inputs

25

ARITHMETIC LOGIC UNITS

49

ALUs

• An Arithmetic Logic Unit is used in most t t l i dprocessors to carry out logic and

arithmetic operations on two numbers.The image cannot be displayed. Your computer may not have enough memory to open the image, or the image may have been corrupted. Restart your computer, and then open the file again. If the red x still appears, you may have to delete the image and then insert it again.

50

26

Building a 32-bit ALU

• Let us design a simple, modular 32-bit ALU with four logic and four arithmetic operators Thus wefour logic and four arithmetic operators. Thus we need 3 bits for operation selection.

The image cannot be displayed. Your computer may not have enough memory to open the image, or the image may have been corrupted. Restart your computer, and then open the file again. If the red x still appears, you may have to delete the image and then insert it again.

51

Building a 32-bit ALU

• We can make this ALU modular in several L t k it d l b f iways. Let us make it modular by focusing

on the ith digit in the operand and make a module for that (then copy this 32 times).

52

27

Inside the 1-bit ALU

• Let us divide up the operations into a logic unit (LU) and into an arithmetic unit (AU).into an arithmetic unit (AU).

53

Inside the 1-bit LU

54

28

Inside the 1-bit AU

• Recall our discussion on subtraction

55

The Complete 1-bit ALU

56