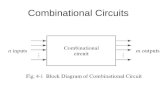

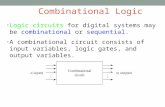

Digital Design - Combinational Logic Design Chapter 2 - Combinational Logic Design.

Combinational#Circuits##3# - California State …vvakilian/CourseECE322/LectureNotes/... ·...

Transcript of Combinational#Circuits##3# - California State …vvakilian/CourseECE322/LectureNotes/... ·...

California State University

Combinational Circuit Building Blocks

n Commonly used combinational building blocks in design of larger circuits: Ø Multiplexers Ø DemultiplexersØ DecodersØ Encoders Ø Priority EncodersØ ComparatorsØ Arithmetic Circuits

California State University

Decoders

n Decodern binary inputs2n binary outputsFunction: decode encoded information

If enable=1, one output is asserted high, the other outputs are asserted lowIf enable=0, all outputs asserted low

Often, enable pin is not needed (i.e. the decoder is always enabled)Called n-to-2n decoder

Can consider n binary inputs as a single n-bit inputCan consider 2n binary outputs as a single 2n-bit output

Decoders are often used for RAM/ROM addressing

n-1

w 0

ninputs

EnEnable

2 n

outputs

y 0

w y 2 n 1 –

California State University

2-to-4 Decoder

0 0 1 1

1 0 1

y 3 w 1

0

w 0

(c) Logic circuit

w 1

w 0

- -

1 1

0

1 1

En

0 0 1

0

0

y 2

0 1 0

0

0

y 1

1 0 0

0

0

y 0

0 0 0

1

0

y 0

y 1

y 2

y 3

En

(a) Truth table (b) Graphical symbol

w 0

En

y 0 w 1 y 1

y 2 y 3

California State University

4-to-1 Multiplexer Built Using a Decoder

w 1

w 0

w 0

En

y 0 w 1 y 1

y 2 y 3

w 2

w 3

f s 0 s 1

1

4-to-1 Multiplexer

California State University

4-to-1 Multiplexer Built Using a Decoder & Tri-State Buffers

4-to-1 Multiplexer

w1

w0

w0

En

y0w1 y1

y2y3

f

s0s1

1 w2

w3

California State University

VHDL Code for 2-to-4 Decoder

library ieee ;use ieee.std_logic_1164.all;

entity dec2to4 isport(w : in std_logic_vector(1 downto 0);

En: in std_logic;y : out std_logic_vector(0 to 3));

end dec2to4;

architecture behavior of dec2to4 issignal Enw: std_logic_vector(2 downto 0);

BeginEnw <= En & w;with Enw select

y <= “1000” when “100”,“0100” when “101”,“0010” when “110”,“0001” when “111”,“0000” when others;

end behavior;

California State University

Encoders

2 n

inputs

w 0 y 0

y n 1 –

n outputs

n EncoderØ 2n binary inputsØ n binary outputsØ Function: encodes information into an n-bit code Called 2n-to-n encoder

Ø Can consider 2n binary inputs as a single 2n-bit inputØ Can consider n binary output as a single n-bit output

n Encoders only work when exactly one binary input is equal to 1

w 2 n 1 –

California State University

4-to-2 Encoder

0 0 1 1

1 0 1

w 3 y 1

0

y 0

(b) Circuit

w 1

w 0

0 0 1

0

w 2

0 1 0

0

w 1

1 0 0

0

w 0

0 0 0

1

y 0

w 2

w 3 y 1

(a) Truth table

California State University

VHDL Code for 4-to-2 Encoder

library ieee ;use ieee.std_logic_1164.all;

entity enc4to2 isport(w : in std_logic_vector(3 downto 0);

y : in std_logic_vector(1 downto 0));end enc4to2;

architecture behavior of enc4to2 isbegin

with w selecty <= “00” when “0001”,

“01” when “0010”,“10” when “0100”,“11” when others;

end behavior;

California State University

Priority Encoders

2 n

inputs

w 0

w 2 n 1 –

y 0

y n 1 –

n outputs

n Priority Encoder2n binary inputsn binary outputs1 binary "valid" outputFunction: encodes information into an n-bit code based on priority of inputsCalled 2n-to-n priority encoder

n Priority encoder allows for multiple inputs to have a value of '1', as it encodes the input with the highest priority (MSB = highest priority, LSB = lowest priority)

"valid" output indicates when priority encoder output is validPriority encoder is more common than an encoder

z "valid" output

California State University

4-to-2 Priority Encoder

-001

010

w0 y1

-

y0

1 1

01

1

11

z

1--

0

-

w1

01-

0

-

w2

001

0

-

w3

000

0

1

Truth table for a 4-to-2 priority encoder

California State University

library ieee;use ieee.std_logic_1164.all;

entity priority isport ( w : in std_logic_vector(3 downto 0);

y : out std_logic_vector(1 downto 0);z : out std_logic );

end priority;

architecture behavior of priority isbegin

y <= "11" when w(3) = '1' else"10" when w(2) = '1' else "01" when w(1) = '1' else"00" ;

z <= '0' when w = "0000" else '1';end behavior;

VHDL Code for Priority Encoder

California State University

(b) Equivalent circuit

(c) Truth table

x f

e

(a) A tri-state buffer

0 0 1 1

0 1 0 1

Z Z 0 1

f e x

x f

e = 0

e = 1x f

Tri-state Buffer

California State University

library ieee;use ieee.std_logic_1164.all;

entity tri_state isport (ena : in std_logic;

input : in std_logic;output: out std_logic);

end tri_state;

architecture behavior of tri_state isbegin

output <= input when (ena = ‘1’) else ‘z’;end behavior;

VHDL Code for Tri-state Buffer