Digital Microelectronic Circuits · 2017-09-28 · Sequential logic The VLSI Systems Center - BGU...

Transcript of Digital Microelectronic Circuits · 2017-09-28 · Sequential logic The VLSI Systems Center - BGU...

Sequential logic The VLSI Systems Center - BGU 1

Digital Microelectronic

Circuits

(361-1-3021 )

Sequential LogicCircuits and Memories

Presented by: Adam Teman

Lecture 12:

Sequential logic The VLSI Systems Center - BGU

Last Lecture

Dynamic Logic

» Features and Problems

» Domino Logic

2

Sequential logic The VLSI Systems Center - BGU

This Lecture

An introduction to sequential circuits and

semiconductor memory, focusing on the

circuit level implementation of basic gates

and cells.

A much more in-depth study of these circuits

will be given in Introduction to VLSI.

3

Sequential logic The VLSI Systems Center - BGU

What will we learn today?

4

11.1 The Latch

11.2 The Flip Flop

11.3 Read Only Memory

11.4 SRAM

11.5 DRAM

Sequential logic The VLSI Systems Center - BGU 5

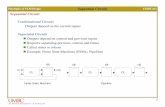

Sequential Logic

COMBINATIONALLOGIC

Registers

Outputs

Next state

CLK

Q D

Current State

Inputs

Sequential logic The VLSI Systems Center - BGU

Memory Hierarchy

6

Sequential logic The VLSI Systems Center - BGU

LATCH

The basic sequential timing element is the

7

11.111.1 The Latch

11.2 The Flip Flop

11.3 Read Only Memory

11.4 SRAM

11.5 DRAM

Sequential logic The VLSI Systems Center - BGU

Latch

8

Clk D Q

0 0 Hold

0 1 Hold

1 0 0

1 1 1

Sequential logic The VLSI Systems Center - BGU

Basic Static Latch

9

Clk D Q

0 0 Hold

0 1 Hold

1 0 0

1 1 1

Sequential logic The VLSI Systems Center - BGU

Feedback Mux Latch

10

Clk D Q

0 0 Hold

0 1 Hold

1 0 0

1 1 1

Sequential logic The VLSI Systems Center - BGU

Simple Dynamic Latch

11

Sequential logic The VLSI Systems Center - BGU

C2MOS

12

Sequential logic The VLSI Systems Center - BGU

TSPC

13

Sequential logic The VLSI Systems Center - BGU

FLIP FLOP

The most important timing element in synchronous systems is the

14

11.211.1 The Latch

11.2 The Flip Flop

11.3 Read Only Memory

11.4 SRAM

11.5 DRAM

Sequential logic The VLSI Systems Center - BGU

Flip Flop = Register

15

Clk D Q

01 0 0

01 1 1

0 X Hold

1 X Hold

Sequential logic The VLSI Systems Center - BGU 16

Master-Slave (Edge-Triggered) Register

Two opposite latches trigger on edge

Also called master-slave latch pair

Sequential logic The VLSI Systems Center - BGU 17

Master-Slave Register

Multiplexer-based latch pair

Clock load – 8 transistors

QM

Q

D

CLK

T 2I2

T 1I1

I3 T 4I5

T 3I4

I6

Sequential logic The VLSI Systems Center - BGU

C2MOS Register

18

Sequential logic The VLSI Systems Center - BGU

Pulse Triggered Register

19

Sequential logic The VLSI Systems Center - BGU

READ ONLY MEMORY

Now we are ready to look at the basic memory array:

20

11.311.1 The Latch

11.2 The Flip Flop

11.3 Read Only Memory

11.4 SRAM

11.5 DRAM

Sequential logic The VLSI Systems Center - BGU

Memory Architecture

21

Sequential logic The VLSI Systems Center - BGU 22

Read-Only Memory Cells

1

0

WL

BL

WL

BL

Diode ROM

WL

BL

WL

BL

VDD

MOS ROM 1

WL

BL

WL

BL

GND

MOS ROM 2

Sequential logic The VLSI Systems Center - BGU

MOS NOR ROM

23

Sequential logic The VLSI Systems Center - BGU 24

Precharged MOS NOR ROM

Sequential logic The VLSI Systems Center - BGU 25

MOS NAND ROM

All word lines high by default with exception of selected row

Sequential logic The VLSI Systems Center - BGU

STATIC RANDOM ACCESS MEMORY

Most embedded memories are implemented with

26

11.411.1 The Latch

11.2 The Flip Flop

11.3 Read Only Memory

11.4 SRAM

11.5 DRAM

Sequential logic The VLSI Systems Center - BGU

Random Access Memories

27

Sequential logic The VLSI Systems Center - BGU

Basic Static Memory Element

28

Sequential logic The VLSI Systems Center - BGU

Positive Feedback: Bi-Stability

29

Sequential logic The VLSI Systems Center - BGU

Memory Cell

30

Sequential logic The VLSI Systems Center - BGU 31

6-transistor CMOS SRAM Cell

WL

BL

VDD

M5M6

M4

M1

M2

M3

BL

Sequential logic The VLSI Systems Center - BGU

SRAM Operation - Read

32

Sequential logic The VLSI Systems Center - BGU

SRAM Operation - Write

33

Sequential logic The VLSI Systems Center - BGU

DYNAMIC RANDOM ACCESS MEMORY

How about reducing the number of transistors to achieve high

density…

34

11.511.1 The Latch

11.2 The Flip Flop

11.3 Read Only Memory

11.4 SRAM

11.5 DRAM

Sequential logic The VLSI Systems Center - BGU

3-Transistor DRAM Cell

35

Sequential logic The VLSI Systems Center - BGU

1-Transistor DRAM Cell

36

Sequential logic The VLSI Systems Center - BGU

1-Transistor DRAM Cell

37

prechargeinitial BL S SQ V C V C

prechargefor 2 :DDV V

finalfinal BL SQ V C C

DD

final

0.5'1'

T S DD BL

BL S

V V C V CV

C C

final '0 '2

DD BL

BL S

V CV

C C