Combinational Logic Circuitscslee/digital_logic/chap2b.pdf · 2011-06-20 · 1 Chap 2....

Transcript of Combinational Logic Circuitscslee/digital_logic/chap2b.pdf · 2011-06-20 · 1 Chap 2....

1

Chap 2. Chap 2. Combinational Logic CircuitsCombinational Logic Circuits

Spring 2004

Chap.2 2OverviewOverview

Part 1 – Gate Circuits and Boolean EquationsBinary Logic and GatesBoolean AlgebraStandard Forms

Part 2 – Circuit OptimizationTwo-Level OptimizationMap ManipulationMulti-Level Circuit Optimization

Part 3 – Additional Gates and CircuitsOther Gate TypesExclusive-OR Operator and GatesHigh-Impedance Outputs

Chap.2 3OverviewOverview

Part 1 – Gate Circuits and Boolean Equations

Binary Logic and GatesBoolean AlgebraStandard Forms

Part 2 – Circuit OptimizationTwo-Level OptimizationMap ManipulationMulti-Level Circuit Optimization

Part 3 – Additional Gates and CircuitsOther Gate TypesExclusive-OR Operator and GatesHigh-Impedance Outputs

Chap.2 42.1 Binary Logic and Gates2.1 Binary Logic and Gates

Digital circuitshardware components that manipulate binary informationimplemented using transistors and interconnections in ICeach basic circuit is called logic gate

performs a specific logical operation

Boolean Algebramathematical notation to specify the operation of each gateused to analyze and design circuits

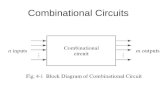

Chap.2 5Combinational LogicCombinational Logic

특징

logic gate 들로 구성and, or, not, nand, nor, xor, xnor등

한개 이상의 입력, logic gate, 한 개 이상의 출력으로 구성입력과 출력과의 관계가진리표

gate 들을 여러 가지로 조합시켜서 사용입력 n 개 이면 2n 개의조합을 고려

출력신호가 입력 신호에의해서만 결정

입력된 정보에 대하여동시에 이진수의 출력정보를 제공

메모리(state) 기능이없다.

종류

adder, subtracter, multiplier, comparator, code converter, encoder, decoder, multiplexer, demultiplexer

Chap.2 62.1 Binary Logic and Gates2.1 Binary Logic and Gates

Binary Logictake on two discrete values &

with the operations of mathematical logic

three logical operations

1) AND Z = X • Y (Z is equal to X and Y)

2) OR Z = X + Y (Z is equal to X or Y)

3) NOT Z = X' (Z is equal to NOT X)

-- complement operation (0 => 1 & 1 => 0)

AND/OR is similar to multiplication/addition

2

Chap.2 72.1 Binary Logic and Gates2.1 Binary Logic and Gates

logical OR logical AND logical NOT0 + 0 = 0 0 • 0 = 0 0' = 10 + 1 = 1 0 • 1 = 0 1' = 01 + 0 = 1 0 • 1 = 01 + 1 = 1 1 • 1 = 1

Chap.2 82.1 Binary Logic and Gates2.1 Binary Logic and Gates

Logic Gateselectronic circuits that operate on one or more input signals to produce an output signalvoltage operated circuits: logic 0 & logic 1 intermediate region is crossed during state transition

Chap.2 9

MultiMulti--input Gatesinput Gates

Chap.2 102.2 Boolean Algebra2.2 Boolean Algebra

Boolean function deals with binary variables and logic operation symbolswith three basic logic operations AND, OR, NOTexpress logical relationship between binary variables

Consider F = X + Y' Z represented in a truth tabletransformed from an algebraic expression into a circuit diagram composed of logic gates (Fig 2.3)

F = X + Y' Z

Chap.2 112.2 Boolean Algebra2.2 Boolean Algebra

Basic Identities of Boolean Algebramost basic identities of Boolean algebradual - obtained by interchanging OR and AND,

and replacing 1's by 0's and 0's by 1's

Table 2-3. Basic Identities of Boolean Algebra

Chap.2 122.2 Boolean Algebra2.2 Boolean Algebra

AB + C + 1 = 1 (by identity 3)commutative laws -- the order doesn't affect the result

X + Y = Y + X, X Y = Y X

associative laws -- parentheses can be removed altogetherX + (Y + Z) = (X + Y) + Z = X + Y + ZX (Y Z) = (X Y) Z = X Y Z

distributive laws (dual)X + Y Z = (X + Y) (X + Z)(A + B) (A + CD) = ?

DeMorgan's theorem -- obtain complement of an expression(X + Y)' = X' Y' (X Y)' = X' + Y ‘ (Table 2.4)can be extended to three or more variables(A + B + C + ... )' = A' B' C' ...

3

Chap.2 132.2 Boolean Algebra2.2 Boolean Algebra

Algebraic Manipulation

Boolean algebra is a useful tool for simplifying digital circuits

F = X'YZ + X'YZ' + XZ= X'Y (Z+Z') + XZ= X'Y 1 + XZ= X'Y + XZ

compare two implementations in Fig 2.4

Chap.2 142.2 Boolean Algebra2.2 Boolean Algebra

use truth table to verify two expressions (Table 2.5)manipulate Boolean algebra lower terms, literals obtain a simpler circuitpopular tools

1. X + XY = X (1 + Y) = X2. XY + XY' = X (Y + Y') = X3. X + X'Y = (X + X') (X + Y) = X + Y4. X (X + Y) = X + X Y = X (1 + Y) = X5. (X + Y)(X + Y') = X + YY' = X6. X (X' + Y) = XX' + XY = XY

consensus theoremXY + X'Z + YZ = XY + X'Z (prove it!)dual (X+Y)(X'+Z)(Y+Z) = (X+Y)(X'+Z)

(Ex) (A+B)(A'+C) = AA' + AC + A'B + BC = AC + A'B + BC = AC + A'B

Chap.2 152.2 Boolean Algebra2.2 Boolean Algebra

Complement of a Functionobtained from an interchange of 1's to 0's and 0's to 1's derived algebraically by applying DeMorgan's theorem

(Ex 2.1) Find the complement of F1 = X'YZ' + X'Y'ZF1' = (X'YZ' + X'Y'Z)'

= (X'YZ')' (X'Y'Z)'= (X + Y' + Z) (X + Y + Z')

(Ex 2.2) Find the complement of F1 = X'YZ' + X'Y'Zby taking dual and complementing each literal

dual of F1 (X' + Y + Z') (X' + Y' + Z)comp of each literal (X + Y' + Z) (X + Y + Z')

Chap.2 162.3 Standard Forms2.3 Standard Forms

facilitate the simplification procedures for Boolean expression contain product terms (XY'Z) and sum terms (X+Y+Z')

Minterms & Maxtermsminterm (a product term) & maxterm (a sum term)all the variables appear exactly onceshow exactly one combination of the binary variables in a truth table2n distinct terms for n variables

(Ex) 4 minterms for 2 variables X & YX'Y', X'Y, XY', & XY

Chap.2 172.3 Standard Forms2.3 Standard Forms

Table 2-6. Minterms for 3 Variables

Table 2-7. Maxterms for 3 Variables

Chap.2 182.3 Standard Forms2.3 Standard Forms

mj (minterm) -- complemented if the bit is 0uncomplemented if the bit is 1

Mj (maxterm) -- complemented if the bit is 1uncomplemented if the bit is 0

j denotes the binary number of the term

minterm: having the minimum No of 1's in its truth tablemaxterm: having the maximum No of 1's in its truth table

a minterm and maxterm with the same subscript are complements of each other (Mj = mj')

(Ex) (m3)' = ( X' Y Z )' = X + Y' + Z' = M3

4

Chap.2 192.3 Standard Forms2.3 Standard Forms

a Boolean function can be expressed by a sum of minterms

(Ex) Table 2-8(a)F = X'Y'Z'+X'YZ'+XY'Z+XYZ = m0+m2+m5+m7

F(X,Y,Z) = Σ m(0,2,5,7) (Σ = logical sum, Boolean OR)F' = X'Y'Z+X'YZ+XY'Z'+XYZ' = m1+m3+m4+m6

F(X,Y,Z)' = Σ m(1,3,4,6)

F = (m1+m3+m4+m6)' = m1’ • m3' • m4' • m6' = M1 • M3 • M4 • M6= (X+Y+Z') • (X+Y'+Z') • (X'+Y+Z) • (X'+Y'+Z)

F(X,Y,Z) = Π M(1,3,4,6) (Π: logical product, Boolean AND)

summary of minterms (p44)

a function can be converted to the sum of minterms form by means of a truth table

Chap.2 202. 3 Standard Forms2. 3 Standard Forms

(Ex) E = Y' + X'Z’

from the truth table, E(X,Y,Z) = Σ m(0,1,2,4,5) E(X,Y,Z)' = Σ m(3,6,7)

(the total number of mintermsin E and E' is 8)

G(X,Y) = Σm(0,1,2,3) = 1

X Y Z F0 0 0 10 0 1 10 1 0 10 1 1 01 0 0 11 0 1 11 1 0 01 1 1 0

Chap.2 212.3 Standard Forms2.3 Standard Forms

Sum of Productsa standard algebraic expressionobtained directly from a truth table (sum of minterms)

& simplify the expression to sum-of-products form

(Ex) F = Y' + X'YZ' + XYthree product terms -- two AND gates, one OR gatetwo-level implementation

Chap.2 222.3 Standard Forms2.3 Standard Forms

(Ex) F = AB + C(D+E) (three-level)=> AB + CD + DE (two-level)

two-level implementation is preferred for its delay time

Chap.2 232.3 Standard Forms2.3 Standard Forms

Product of Sumsanother standard algebraic expressionobtained by forming a logical product of sum terms

(Ex) F = X(Y'+Z)(X+Y+Z')needs 2 OR gates and one AND gates

Overview

Part 1 – Gate Circuits and Boolean Equations• Binary Logic and Gates• Boolean Algebra• Standard Forms

Part 2 – Circuit Optimization• Two-Level Optimization• Map Manipulation• Multi-Level Circuit Optimization

Part 3 – Additional Gates and Circuits• Other Gate Types• Exclusive-OR Operator and Gates• High-Impedance Outputs

5

Circuit Optimization

Goal: To obtain the simplest implementation for a given functionOptimization is a more formal approach to simplification that is performed using a specific procedure or algorithmOptimization requires a cost criterion to measure the simplicity of a circuitTwo distinct cost criteria we will use:• Literal cost (L)• Gate input cost (G)• Gate input cost with NOTs (GN)

D

Literal – a variable or it complementLiteral cost – the number of literal appearances in a Boolean expression corresponding to the logic circuit diagramExamples:• F = BD + A C + A L = 8• F = BD + A C + A + AB L = • F = (A + B)(A + D)(B + C + )( + + D) L =• Which solution is best?

Literal Cost

DB CB B D C

B C

Gate Input CostGate input costs - the number of inputs to the gates in the implementation corresponding exactly to the given equation or equations. (G - inverters not counted, GN - inverters counted)

For SOP and POS equations, it can be found from the equation(s) by finding the sum of:• all literal appearances• the number of terms excluding terms consisting only of a single

literal,(G) and• optionally, the number of distinct complemented single literals (GN).

Example:• F = BD + A C + A G = 8, GN = 11• F = BD + A C + A + AB G = , GN = • F = (A + )(A + D)(B + C + )( + + D) G = , GN =• Which solution is best?

DB CB B D C

B D B C

Example 1:

F = A + B C +

Cost Criteria (continued)

A

BC

F

B C L = 5

L (literal count) counts the AND inputs and the singleliteral OR input.

G = L + 2 = 7

G (gate input count) adds the remaining OR gate inputs

GN = G + 2 = 9

GN(gate input count with NOTs) adds the inverter inputs

Example 2:

F = A B C +L = 6 G = 8 GN = 11F = (A + )( + C)( + B)L = 6 G = 9 GN = 12Same function and sameliteral costBut first circuit has bettergate input count and bettergate input count with NOTsSelect it!

Cost Criteria (continued)

BC

A

ABC

F

C B

F

ABC

A

Chap.2 302.4 22.4 2--level Circuit Optimizationlevel Circuit Optimization

Karnaugh map (K-map)to simplify Boolean functions of up to 4 variables(5 or 6 variables can be drawn, but cumbersome to use)a diagram of squares, each representing one mintermsimplified expressions are in sum-of-products or product-of-sums

two-level implementationsExample

2-level POS2-level SOP

6

Chap.2 312.4 Map Simplification2.4 Map Simplification

Two-Variable Mapfour minterms for a Boolean function with 2 variables

(Ex)

m1+m2+m3 = X'Y+XY'+XY = X+Y

(by algebra) => X'Y+X(Y'+Y) = X'Y+X = X+Y

Chap.2 322.4 Map Simplification2.4 Map Simplification

Three-variable Map8 minterms for 3 variables

Ex2.3 F(X,Y,Z) = Σ m(2,3,4,5)

(from K-map) F = X'Y + XY'

Chap.2 332.4 Map Simplification2.4 Map Simplification

(Ex)

(Ex) (Ex)

m0+m2+m4+m6 = Z' m0+m1+m2+m3+m6+m7 = X' + Y

Chap.2 342.4 Map Simplification2.4 Map Simplification

Ex2.4 F1(X,Y,Z) = Σ m(3,4,6,7) F2(X,Y,Z) = Σ m(0,2,4,5,6)

(Ex)

F2(X,Y,Z) = Σ m(1,3,4,5,6)= X'Z + XZ' + XY'

or = X'Z + XZ' + Y'Z

Chap.2 352.4 Map Simplification2.4 Map Simplification

Four-variable Map16 mintermsfor 4 variables

Chap.2 362.4 Map Simplification2.4 Map Simplification

Ex2.5 F(W,X,Y,Z) = Σ m(0,1,2,4,5,6,8,9,12,13,14)

F = Y' + W'Z' + XZ'

Ex2.6 F = A'B'C' + B'CD' + A'BCD' + AB'C'

F = B'D' + B'C' + A'CD'

7

Chap.2 372.5 Map Manipulation2.5 Map Manipulation

Combining squaresensure that all minterms of the functions are includednecessary to minimize the number of terms

Essential Prime Implicantsimplicant

A product term is an implicant of a function Fif that product term=1, then the function F=1if the function has the value 1 for all minterms of the product term

Chap.2 38ImplicantImplicant

Ex) F=AB+BC+AB’C 의 implicant를 모두 찾으시오.AB, BC, AB’C are implicants of FABC, ABC’, A’BC (minterms) are also implicants of FAC (product term, nonminterm) is also implicant of F

해석 1: product term AC=1 인 경우 (A,B,C)가 (1,0,1) 또는 (1,1,1) 이고 이때 각각 F=1 을 만족한다. 즉, F(1,0,1)=1, F(1,1,1)=1. 따라서 AC도 implicant 이다.

해석 2: product term AC 의 minterm은 ABC 와 AB’C 이고 이때 모든두 minterm에 대하여 F=1 이다. 따라서 AC도 implicant 이다.

Therefore, the total numer of implicants of F are 7.

Chap.2 39Prime implicantPrime implicant

prime implicantif the removal of any literal from an implicant results in a product term that is not an implicant of Fa product term obtained by combining the maximum possible number of adjacent squares in the mapEx) F=AB+BC+AB’C 의 prime implicant를 모두찾으시오.

AB, BC, AB’C, A’BC, ABC’, ABC, AC are implicantsAB is prime implicant of F

delete B A minterm of A=(1,0,0) But, F(1,0,0)=0 A is not an implicant of F. Thus AB is prime implicant of F.

AB’C is not prime implicant of Fdelete B’ AC AC=1 이면 F=1, AC=implicant

AC is prime implicant of Fdelete A C (0,0,1) But, F(0,0,1)=0

How about BC, A’BC, ABC’, ABC?

Chap.2 40Essential prime implicantEssential prime implicant

prime implicant는 2m (m=0,1,2,….,n) 개씩 조합하여 구할수 있다

essential prime implicantIf a minterm of a function F is included in only one prime implicant,that prime implicant is said to be essential prime implicant.

Ex) F=AB+BC+AB’C 의 essential prime implicant를 모두 찾으시오.

Chap.2 41Prime Implicant Groups(1)Prime Implicant Groups(1)

0010

1000

0010

0100

1001

0010

1110

0101

(a) (b)

Prime Implicant Groups that involve (a) one, (b) two

Chap.2 42Prime Implicant Groups(2)Prime Implicant Groups(2)

1101

1110

0110

1101

1111

0011

0011

1111

(c) (d)

Prime Implicant Groups that involve (c) four, (d) eight

8

Chap.2 43ExampleExample

F2(X,Y,Z) = Σ m(1,3,4,5,6)

= X'Z + XZ' + XY'

or = X'Z + XZ' + Y'Z

Chap.2 44Essential Prime ImplicantsEssential Prime Implicants

1100

1111

0010

0110

1100

1111

0010

0110

(a) (b)

(a) Prime Implicant Groups, (b) Essential Prime Implicant Groups

Chap.2 45Essential Prime ImplicantsEssential Prime Implicants

1100

1111

0010

0110

1100

1111

0010

0110

(a) (b)

(a) Prime Implicant Groups, (b) Essential Prime Implicant Groups

Chap.2 462.5 Map Manipulation2.5 Map Manipulation

To find the simplified expression from the map,1) first determine all prime implicant2) simplified expression

all the essential prime implicant + other prime implicant

(Ex) Fig 2.21

A'D and BD': essential prime implicants

A'B: not essential

Chap.2 47

Chap.2 482.5 Map Manipulation2.5 Map Manipulation

(Ex) Fig 2.22

A'B'C'D', BC'D, ABC', AB'C: essential prime implicantsACD or ABD: not essential

F = A'B'C'D' + BC'D + ABC' + AB'C + ACD or ABD

9

Chap.2 49

Chap.2 502.5 Map Manipulation2.5 Map Manipulation

Nonessential Prime ImplicantSelection Rule

minimize the overlap among prime implicant as much as possible

Ex2.7 F(A,B,C,D) = Σ m(0,1,2,4,5,10,11,13,15)

F' = A'C' + ABD + AB'C + A'B'D'

Chap.2 512.5 Map Manipulation2.5 Map Manipulation

Product-of-Sums Simplificationfrom sum-of-products to product-of-sumscomplement the function (taking a dual)

1) Combine the squares marked with 0's2) change the function,

which is expressed in product of sums to sum of products

Ex2.8 F(A,B,C,D) = Σ m(0,1,2,5,8,9,10)

F' = AB + CD + BD'F = (A'+B')(C'+D')(B'+D)

Chap.2 52Ex 2Ex 2--99

F(A,B,C,D)=∑m(0,1,2,4,5,10,11,13,15)

Chap.2 53Ex 2Ex 2--1010

F(A,B,C,D)=∑m(0,1,2,5,8,9,10)

i) combining the 1’s results in SOP form.

ii) combining the 0’s and complementing it gives POS form.

F’ (SOP) F (POS)

Chap.2 542.5 Map Manipulation2.5 Map Manipulation

Ex) F = (A'+B'+C) (B + D)1) plot the map by taking its complement

F' = ABC' + B'D'2) marking 0's in the squares to represent F'

remaining squares are marked with 1's3) combine the 1’s (SOP) or 4) combine the 0's and then complement the function (POS)

Ex) F=(A’+B’+D’)(A+B’+C’)(A’+B+D’)(B+C’+D’)1) SOP

a) F’b) marking 0’s with product terms, others are 1’s.c) combine 1’s to get F directly

2) POScombine 0’s and complement F’ to get F

10

Chap.2 552.5 Map Manipulation2.5 Map Manipulation

Don't Care Conditionsunspecified minterms of a functionex) 4-bit binary code for the decimal digitsmarked with cross (X)provide the further simplification of the function

Chap.2 562.5 Map Manipulation2.5 Map Manipulation

Ex) F(A,B,C,D) = Σ m(1,3,7,11,15) d(A,B,C,D) = Σ m(0,2,5)

obtain a simplified product-of-sums

F = CD + A'B' = CD + A'D

F' = Z' + WY'F = Z(W' + Y)

2-6 Multiple-Level Optimization

Multiple-level circuits - circuits that are not two-level (with or without input and/or output inverters)Multiple-level circuits can have reduced gate input cost compared to two-level (SOP and POS) circuitsMultiple-level optimization is performed by applying transformations to circuits represented by equations while evaluating cost

Multiple-Level Circuit Example

Transformations

Factoring - finding a factored form from SOP or POS expression• Algebraic - No use of axioms specific to

Boolean algebra such as complements or idempotence

• Boolean - Uses axioms unique to Boolean algebra

Decomposition - expression of a function as a set of new functions

Transformations (continued)

Substitution of G into F - expression function F as a function of G and some or all of its original variablesElimination - Inverse of substitutionExtraction - decomposition applied to multiple functions simultaneously

11

Transformation Examples

Algebraic FactoringF = + B + ABC + AC G = 16• Factoring:

F = ( + B ) + A (BC + C ) G = 16• Factoring again:

F = ( B + ) + AC (B + ) G = 12• Factoring again:

F = ( + AC) (B + ) G = 10

DCAA

A

A

C

C

D

CC D

D

D

A C D D

Transformation Examples

Decomposition• The terms B + and + AC can be defined

as new functions E and H respectively, decomposing F:

F = E H, E = B + , and H = + AC G = 10This series of transformations has reduced G from 16 to 10, a substantial savings. The resulting circuit has three levels plus input inverters.

ACD

D AC

Transformation Examples

Substitution of E into F• Returning to F just before the final factoring step:

F = ( B + ) + AC (B + ) G = 12• Defining E = B + , and substituting in F:

F = E + ACE G = 10• This substitution has resulted in the same cost as the

decomposition

A C DD

A CD

Transformation Examples

Elimination• Beginning with a new set of functions:

X = B + CY = A + BZ = X + C Y G = 10 • Eliminating X and Y from Z:

Z = (B + C) + C (A + B) G = 10• “Flattening” (Converting to SOP expression):

Z = B + C + AC + BC G = 12• This has increased the cost, but has provided an new

SOP expression for two-level optimization.

A

A

A

A

Transformation Examples

Two-level Optimization• The result of 2-level optimization is:

Z = B + C G = 4This example illustrates that:• Optimization can begin with any set of equations,

not just with minterms or a truth table• Increasing gate input count G temporarily during a

series of transformations can result in a final solution with a smaller G

A

Transformation ExamplesExtraction• Beginning with two functions:

E = + BD H = C + BCD G = 16 • Finding a common factor and defining it as a

function:

F = + BD• We perform extraction by expressing E and H as

the three functions:

F = + BD, E = F, H = CF G = 10• The reduced cost G results from the sharing of logic

between the two output functions

BA A

A

B

B

DD

D

BD

12

Overview

Part 1 – Gate Circuits and Boolean Equations• Binary Logic and Gates• Boolean Algebra• Standard Forms

Part 2 – Circuit Optimization• Two-Level Optimization• Map Manipulation• Multi-Level Circuit Optimization

Part 3 – Additional Gates and Circuits• Other Gate Types• Exclusive-OR Operator and Gates• High-Impedance Outputs

Chap.2 682.7 NAND and NOR Gates2.7 NAND and NOR Gates

Boolean functions are expressed in terms of

AND, OR, NOTstraight forward to implement the function with these gatesOther useful logic gates

Chap.2 692.6 NAND and NOR Gates2.6 NAND and NOR Gates

NAND gatea universal gate

because any digital system can be implemented with it

Implementation of NOT (inverter), AND, OR

2 graphic symbols: AND-invert & invert-OR

Chap.2 702.6 NAND and NOR Gates2.6 NAND and NOR Gates

Two-Level Implementationeasy to implement with NAND gates, if the function is in sum ofproducts form

(Ex) F = AB + CD

F = ( (AB)' (CD)' )' = AB + CD

Chap.2 712.6 NAND and NOR Gates2.6 NAND and NOR Gates

Ex2.9) F(X,Y,Z) = Σ m(1,2,3,4,5,7)

Chap.2 722.6 NAND and NOR Gates2.6 NAND and NOR Gates

Multilevel NAND Circuitswith three or more levels1) convert all AND gates to NAND gates w/ AND-invert2) convert all OR gates to NAND gates w/ invert-OR3) convert rest small circles to inverters

Ex) F = A (CD + B) + BC'

13

Chap.2 73

Chap.2 742.6 NAND and NOR Gates2.6 NAND and NOR Gates

NOR gatedual of the NAND operationanother universal gateimplementation of NOT (inverter), AND, OR

two graphic symbol for NOR gate

Chap.2 752.6 NAND and NOR Gates2.6 NAND and NOR Gates

Two-Level Implementationeasy to implement with NOR gates,

if the function is in product of sums form(Ex) F = (A + B) (C + D) E

(Ex) F = (AB' + A'B) E (C + D')

Chap.2 762.7 Exclusive2.7 Exclusive--OR GateOR Gate

exclusive-OR (XOR) gateX ⊕ Y = X Y' + X' Y1 if only one variable is equal to 1, but not both

exclusive-NOR gate( X ⊕ Y )' = X Y + X' Y'1 if both are equal to 1 or both are equal to 0

they are to be the complement of each other

Chap.2 772.7 Exclusive2.7 Exclusive--OR GateOR Gate

propertiesX ⊕ 0 = X X ⊕ 1 = X'X ⊕ X = 0 X ⊕ X' = 1X ⊕ Y' = (X ⊕ Y)' X' ⊕ Y = (X ⊕ Y)'

A ⊕ B = B ⊕ A(A ⊕ B) ⊕ C = A ⊕ (B ⊕ C) = A ⊕ B ⊕ C

implementation with NAND gates

Chap.2 78Odd FunctionOdd Function

F=X ⊕ Y ⊕ Z = (XY’+X’Y)Z’+(XY+X’Y’)Z= XY’Z’+X’YZ’+X’Y’Z+XYZ

14

Chap.2 79Odd FunctionOdd Function Chap.2

80Parity Generation and CheckingParity Generation and Checking

Chap.2 81Parity Generation and CheckingParity Generation and Checking Chap.2

822.8 Integrated Circuits2.8 Integrated Circuits

Integrated Circuits (IC)small silicon semiconductor crystal, called a chipcontains electronic components for the digital gates

Levels of IntegrationSSI (small scale integration), < 10 gatesMSI, 10 ~ 100 gatesLSI, 100 ~ 1000sVLSI, > 1000s

Chap.2 832.8 Integrated Circuits2.8 Integrated Circuits

Digital Logic FamiliesRTL, DTL - earliest logic familiesTTL - widespread, considered as standardECL - high speed operationMOS - high component densityCMOS - low power consumptionBiCMOS - CMOS + TTL, used selectively

Positive and Negative LogicNormal Convention:

Positive Logic/Active HighLow Voltage = 0; High Voltage = 1

Alternative Convention sometimes used: Negative Logic/Active Low

Low Voltage = 1; High Voltage = 0

Chap.2 84DelayDelay

propagation delay(전파지연): tpd

transport delay(TD): 전달지연

-전파지연만큼의지연생김

inertial delay(ID): 관성지연

- rejection time 이하의펄스폭은무시

15

Chap.2 85Transport Delay, Inertial DelayTransport Delay, Inertial Delay Chap.2

86Positive and Negative LogicPositive and Negative Logic

inputs: 0(V), +V(V)

positive logic( Active High Logic)

+V(V): logic 1(True), 0(V): logic 0(False)

negative logic (Active Low Logic)

+V(V): logic 0(False), 0(V): logic 1(True)

Chap.2 872.8 Integrated Circuits2.8 Integrated Circuits

(f) polarity indicator: small triangles in I/O

Chap.2 88Transmission GateTransmission Gate

- Electronic Switch between two points

Chap.2 89XOR gate using Transmission GatesXOR gate using Transmission Gates