CHAPTER 3 Sequential Logic/ Circuits: Shift Register.

36

EKT 124 / 3 DIGITAL ELEKTRONIC 1 CHAPTER 3 Sequential Logic/ Circuits: Shift Register

-

Upload

whitney-morton -

Category

Documents

-

view

265 -

download

1

Transcript of CHAPTER 3 Sequential Logic/ Circuits: Shift Register.

- Slide 1

- CHAPTER 3 Sequential Logic/ Circuits: Shift Register

- Slide 2

- Basic shift register function Serial in/Serial out shift registers (SISO) Serial in/Parallel out shift registers (SIPO) Parallel in/Serial out shift registers (PISO) Parallel in/Parallel out shift registers (PIPO) Bidirectional shift registers Shift register applications Shift Register

- Slide 3

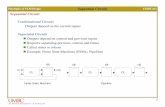

- Sequential Logic Circuits Combinational logic Memory elements Combinational outputs Memory outputs Inputs Sequential circuit = Combinational logic + Memory Elements Current State of A sequential Circuit: Value stored in memory elements (value of state variables). State transition: A change in the stored values in memory elements thus changing the sequential circuit from one state to another state.

- Slide 4

- A register is a memory device that can be used to store more than one-bit information A register is usually realized as several flip-flops with common control signals that control the movement of data to and from the registers . Registers

- Slide 5

- An n-bit register is a collection of n D flip-flops with a common clock used to store n related bits. D 1Q CLR Q Q /1Q 1D D 2Q CLR Q Q /2Q 2D D 3Q CLR Q Q /3Q 3D D 4Q CLR Q Q /4Q 4D CLK /CLR 74LS175 Example: 74LS175 4-bit register CLK CLR 4Q 3Q 2Q 1Q 74LS175 1D 2D 3D 4D

- Slide 6

- Shift Registers Multi-bit register that moves stored data bits left/right ( 1 bit position per clock cycle) 0 1 1 1 LSI Q3 Q2 Q1 Q0 1 1 1 LSI Q3 Q2 Q1 Q0 RSI 0 1 1 1 Q3 Q2 Q1 Q0 RSI 0 1 1 Q3 Q2 Q1 Q0 Shift Right (or Shift Up) is towards MSB Shift Left is towards MSB

- Slide 7

- Basic Shift Register Functions consist of an arrangement of flip-flops important in applications involving storage and transfer of data (data movement) in digital system used for storing and shifting data (1s and 0s) entered into it from an external source and possesses no characteristic internal sequence of states. Generally, D flip-flops are usually used to store and move data

- Slide 8

- The flip-flop as a storage element When a 1 is on D, Q becomes a 1 at triggering edge of CLK or remains a 1 if already in the SET state When a 0 is on D, Q becomes a 0 at triggering edge of CLK or remains a 0 if already in the RESET state

- Slide 9

- Basic data movement in shift registers (Four bits are used for illustration. The bits move in the direction of the arrows.)

- Slide 10

- Types of Shift Registers Serial In / Serial Out Shift Registers (SISO) Serial In /Parallel Out Shift Registers (SIPO) Parallel In / Serial Out Shift Registers (PISO) Parallel In / Parallel Out Shift Registers (PIPO)

- Slide 11

- Serial In, Serial Out Shift Registers (SISO) D Q CLK D Q CLK D Q CLK Serial In Clock Serial Out For a n-bit SRG: Serial Out = Serial In delayed by n clock period 4-bit shift register example: Serial in: 1 0 1 1 0 0 1 1 1 0 Serial out: - - - - 1 0 1 1 0 0 Clock: SRG n > SI SO

- Slide 12

- Serial In, Serial Out Shift Registers (SISO)

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Serial In, Parallel Out Shift registers (SIPO) D Q CLK D Q CLK D Q CLK Serial In Clock nQ 2Q 1Q Serial to Parallel Converter Example: 4-bit shift register serin: 1 0 1 1 0 0 1 1 1 0 1Q: - 1 0 1 1 0 0 1 1 1 2Q: - - 1 0 1 1 0 0 1 1 3Q: - - - 1 0 1 1 0 0 1 4Q: - - - - 1 0 1 1 0 0 clock: SRG n > SI 1Q 2Q nQ SO

- Slide 17

- Serial In, Parallel Out Shift registers (SIPO) Data bits entered serially (right-most bit first) Difference from SISO is the way data bits are taken out of the register in parallel. Output of each stage is available

- Slide 18

- Example: The states of 4-bit register (SRG 4) for the data input and clocks waveforms. Assume the register initially contains all 1s

- Slide 19

- Parallel In, Serial Out Shift Registers (PISO) Serial in CLOCK D Q CLK D Q CLK D Q CLK Serial out LOAD/SHIFT 1D 2D ND S L S L S L 1Q 2Q NQ Parallel to Serial Converter Load/Shift=1 D i Q i Load/Shift=0 Q i Q i +1

- Slide 20

- 4-bit parallel in/serial out shift register (PISO)

- Slide 21

- Parallel In, Parallel Out Shift Register (PIPO) Serial In CLOCK D Q CLK D Q CLK D Q CLK LOAD/SHIFT 1D 2D ND 1Q 2Q NQ S L S L S L General Purpose: Makes any kind of (left) shift register

- Slide 22

- Parallel In, Parallel Out Shift Register (PIPO) Immediately following simultaneous entry of all data bits, it appears on parallel output.

- Slide 23

- 2) SISO - the data is shifted serially "IN" and "OUT" of the register, one bit at a time in either a left or right direction under clock control. 3) PISO - the parallel data is loaded into the register simultaneously and is shifted out of the register serially one bit at a time under clock control. Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: 1) SIPO - the register is loaded with serial data, one bit at a time, with the stored data being available in parallel form. 4) PIPO - the parallel data is loaded simultaneously into the register, and transferred together to their respective outputs by the same clock pulse. Types of Shift Registers

- Slide 24

- Bi-directional Shift Registers Data can be shifted left Data can be shifted right A parallel load maybe possible 74HC194 is an bidirectional universal shift register

- Slide 25

- Bi-directional Universal Shift Registers 4-bit Bi-directional Universal (4-bit) PIPO CLK CLR S1 S0 LIN D QD C QC B QB A QA RIN 11 1 10 9 7 6 4 5 3 2 12 13 14 15 74x194 Modes: Hold Load Shift Right Shift Left R L Mode Next state Function S1 S0 QA* QB* QC* QD* Hold 0 0 QA QB QC QD Shift right/up 0 1 RIN QA QB QC Shift left/down 1 0 QB QC QD LIN Load 1 1 A B C D

- Slide 26

- 4-bit Johnson counters Serial output connected back to serial input The complement of the output (Q) is fedback into 1 st FF.

- Slide 27

- 4-bit Johnson Ring Counter Clock Pulse No FFAFFBFFCFFD 00000 11000 21100 31110 41111 50111 60011 70001 Truth Table for a 4-bit Johnson Ring Counter This inversion of Q before it is fed back to input D causes the counter to "count" in a different way. Instead of counting through a fixed set of patterns like the normal ring counter such as for a 4-bit counter, "0001"(1), "0010"(2), "0100"(4), "1000"(8) and repeat, the Johnson counter counts up and then down as the initial logic "1" passes through it to the right replacing the preceding logic "0". A 4-bit Johnson ring counter passes blocks of four logic "0" and then four logic "1" thereby producing an 8-bit pattern. As the inverted output Q is connected to the input D this 8-bit pattern continually repeats. For example, "1000", "1100", "1110", "1111", "0111", "0011", "0001", "0000

- Slide 28

- Five-bit Johnson counters

- Slide 29

- 10-bit ring counter Assume initial state: (Q0---Q9) =1010000000

- Slide 30

- 4-bit Ring Counter Synchronous Ring Counter is preset so that exactly one data bit in the register is set to logic "1" with all the other bits reset to "0". To achieve this, a "CLEAR" signal is firstly applied to all the flip-flops together in order to "RESET" their outputs to a logic "0" level and then a "PRESET" pulse is applied to the input of the first flip-flop (FFA) before the clock pulses are applied. This then places a single logic "1" value into the circuit of the ring counter. On each successive clock pulse, the counter circulates the same data bit between the four flip-flops over and over again around the "ring" every fourth clock cycle. In order to cycle the data correctly around the counter we must first "load" the counter with a suitable data pattern as all logic "0"'s or all logic "1"'s outputted at each clock cycle would make the ring counter invalid.

- Slide 31

- otational Movement of a Ring Counter ROTATION OF RING COUNTER Since the ring counter has four distinct states, it is also known as a "modulo-4" or "mod- 4" counter with each flip-flop output having a frequency value equal to one-fourth or a quarter (1/4) that of the main clock frequency.

- Slide 32

- Shift Register Applications State Registers Shift registers are often used as the state register in a sequential device. Usually, the next state is determined by shifting right and inserting a primary input or output into the next position (i.e. a finite memory machine) Very effective for sequence detectors Serial Interconnection of Systems keep interconnection cost low with serial interconnect Bit Serial Operations Bit serial operations can be performed quickly through device iteration Iteration (a purely combinational approach) is expensive (in terms of # transistors, chip area, power, etc). A sequential approach allows the reuse of combinational functional units throughout the multi-cycle operation

- Slide 33

- Shift Register Applications Example: Serial Interconnection of Systems Serial DATA Parallel- to-serial converter Parallel Data from A-to-D converter Serial-to- parallel converter Parallel Data to D-to-A converter Control Circuits CLOCK /SYNC Transmitter Control Circuits Receiver n n One bit

- Slide 34

- Shift Register Applications Example: 8-Bit Serial Adder... 7650 > x7x7 x6x6 x5x5 x0x0 7650 > y7y7 y6y6 y5y5 y0y0 7650 > FA Cout S Cin A B D Q CLK CLR CLK CLEAR_C z7z7 z6z6 z5z5 z0z0... CTL Sequential Implementation of: Z[7..0] = X[7..0] + Y[7..0] V

- Slide 35

- Shift Register Applications Example: The shift register as a time-delay device

- Slide 36

- Shift Register Applications Example: Simplified logic diagram of a serial-to-parallel converter