Digital Integrated Circuits 2nd Sequential Circuits Digital Integrated Circuits A Design Perspective...

-

Upload

shonda-spencer -

Category

Documents

-

view

293 -

download

1

description

Transcript of Digital Integrated Circuits 2nd Sequential Circuits Digital Integrated Circuits A Design Perspective...

© Digital Integrated Circuits2nd

Sequential Circuits

Digital Integrated Digital Integrated CircuitsCircuitsA Design PerspectiveA Design Perspective

Designing SequentialDesigning SequentialLogic CircuitsLogic Circuits

Jan M. RabaeyAnantha ChandrakasanBorivoje Nikolic

November 2002

© Digital Integrated Circuits2nd

Sequential Circuits

Sequential LogicSequential Logic

2 storage mechanisms• positive feedback• charge-based

COMBINATIONALLOGIC

Registers

Outputs

Next state

CLK

Q D

Current State

Inputs

© Digital Integrated Circuits2nd

Sequential Circuits

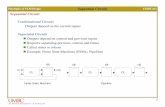

Naming ConventionsNaming Conventions

In our text: a latch is level sensitive a register is edge-triggered

There are many different naming conventions For instance, many books call edge-

triggered elements flip-flops This leads to confusion however

© Digital Integrated Circuits2nd

Sequential Circuits

Latch versus RegisterLatch versus Register Latch

stores data when clock is low

D

Clk

Q D

Clk

Q

Registerstores data when clock rises

Clk Clk

D D

Q Q

© Digital Integrated Circuits2nd

Sequential Circuits

LatchesLatches

In

clk

In

Out

Positive Latch

CLK

DG

Q

Out

Outstable

Outfollows In

In

clk

In

Out

Negative Latch

CLK

DG

Q

Out

Outstable

Outfollows In

© Digital Integrated Circuits2nd

Sequential Circuits

Latch-Based DesignLatch-Based Design

• N latch is transparentwhen = 1

• P latch is transparent when = 0

NLatch Logic

Logic

PLatch

© Digital Integrated Circuits2nd

Sequential Circuits

Timing DefinitionsTiming Definitions

tCLK

tD

tc 2 q

tholdtsu

tQ DATA

STABLE

DATASTABLE

Register

CLK

D Q

© Digital Integrated Circuits2nd

Sequential Circuits

Characterizing TimingCharacterizing Timing

Clk

D Q

tC 2 Q

Clk

D Q

tC 2 Q

tD 2 Q

Register Latch

© Digital Integrated Circuits2nd

Sequential Circuits

Maximum Clock FrequencyMaximum Clock Frequency

FF’s

LOGIC

tp,comb

Also:tcdreg + tcdlogic > thold

tcd: contamination delay = minimum delaytclk-Q + tp,comb + tsetup =

T

© Digital Integrated Circuits2nd

Sequential Circuits

Positive Feedback: Bi-StabilityPositive Feedback: Bi-StabilityVi1 Vo2

Vo2 =Vi1

Vo1 =Vi2

Vi1

A

C

B

Vo2

Vi1=Vo2

Vo1 Vi2

Vi2=Vo1

© Digital Integrated Circuits2nd

Sequential Circuits

Meta-StabilityMeta-Stability

Gain should be larger than 1 in the transition region

A

C

d

B

V i25

V o1

Vi1 5Vo2

A

C

d

B

V i25

V o1

Vi1 5Vo2

© Digital Integrated Circuits2nd

Sequential Circuits

Writing into a Static LatchWriting into a Static Latch

CLK

CLK

CLK

D

Q D

CLK

CLK

D

Converting into a MUXForcing the state(can implement as NMOS-only)

Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states

© Digital Integrated Circuits2nd

Sequential Circuits

Mux-Based LatchesMux-Based LatchesNegative latch(transparent when CLK= 0)Positive latch

(transparent when CLK= 1)

CLK

1

0D

Q 0

CLK

1D

Q

InClkQClkQ InClkQClkQ

© Digital Integrated Circuits2nd

Sequential Circuits

Mux-Based LatchMux-Based Latch

CLK

CLK

CLK

D

Q

© Digital Integrated Circuits2nd

Sequential Circuits

Mux-Based LatchMux-Based Latch

CLK

CLKCLK

CLK

QM

QM

NMOS only Non-overlapping clocks

© Digital Integrated Circuits2nd

Sequential Circuits

Master-Slave (Edge-Triggered) Master-Slave (Edge-Triggered) RegisterRegister

1

0D

CLK

QM

Master

0

1

CLK

Q

Slave

QM

Q

D

Two opposite latches trigger on edgeAlso called master-slave latch pair

© Digital Integrated Circuits2nd

Sequential Circuits

Master-Slave RegisterMaster-Slave Register

QM

Q

D

CLK

T2I2

T1I1

I3 T4I5

T3I4

I6

Multiplexer-based latch pair

© Digital Integrated Circuits2nd

Sequential Circuits

Reduced Clock Load Reduced Clock Load Master-Slave RegisterMaster-Slave Register

D QT1 I1

CLK

CLK

T2

CLK

CLKI2

I3

I4

© Digital Integrated Circuits2nd

Sequential Circuits

Avoiding Clock OverlapAvoiding Clock OverlapCLK

CLK

AB

(a) Schematic diagram

(b) Overlapping clock pairs

X

D

Q

CLK

CLK

CLK

CLK

© Digital Integrated Circuits2nd

Sequential Circuits

Overpowering the Feedback Loop ─Overpowering the Feedback Loop ─Cross-Coupled PairsCross-Coupled Pairs

Forbidden State

S

S

R

Q

QRS Q

Q00 Q

101 0

010 1011 0R Q

NOR-based set-reset

© Digital Integrated Circuits2nd

Sequential Circuits

Storage MechanismsStorage Mechanisms

D

CLK

CLK

Q

Dynamic (charge-based)

CLK

CLK

CLK

D

Q

Static

© Digital Integrated Circuits2nd

Sequential Circuits

Other Latches/Registers: COther Latches/Registers: C22MOSMOS

M1

D Q

M3CLK

M4

M2

CLK

VDD

CL1

X

CL2

Master Stage

M5

M7CLK

CLK M8

M6

VDD

“Keepers” can be added to make circuit pseudo-static

© Digital Integrated Circuits2nd

Sequential Circuits

Insensitive to Clock-OverlapInsensitive to Clock-Overlap

M1

D Q

M4

M2

0 0

VDD

X

M5

M8

M6

VDD

(a) (0-0) overlap

M3

M1

D Q

M2

1

VDD

X

M71

M5

M6

VDD

(b) (1-1) overlap

© Digital Integrated Circuits2nd

Sequential Circuits

PipeliningPipeliningRE

GRE

G

REGlog

a

CLK

CLK

CLK

Out

b

REG

REG

REGlog

a

CLK

CLK

CLK

REG

CLK

REG

CLK

Out

b

Reference Pipelined

© Digital Integrated Circuits2nd

Sequential Circuits

Other Latches/Registers: TSPCOther Latches/Registers: TSPC

CLKIn

VDD

CLK

VDD

In

Out

CLK

VDD

CLK

VDD

Negative latch(transparent when CLK= 0)

Positive latch(transparent when CLK= 1)

© Digital Integrated Circuits2nd

Sequential Circuits

TSPC RegisterTSPC Register

CLK

CLK

D

VDD

M3

M2

M1

CLK

Y

VDD

Q

Q

M9

M8

M7

CLK

X

VDD

M6

M5

M4

© Digital Integrated Circuits2nd

Sequential Circuits

Including Logic in TSPCIncluding Logic in TSPC

CLKIn CLK

VDDVDD

QPUN

PDN

CLK

VDD

Q

CLK

VDD

In1

In1 In2

AND latchExample: logic inside the latch

© Digital Integrated Circuits2nd

Sequential Circuits

Pulse-Triggered LatchesPulse-Triggered LatchesAn Alternative ApproachAn Alternative Approach

Master-Slave Latches

D

Clk

Q D

Clk

Q

Clk

DataD

Clk

Q

Clk

Data

Pulse-Triggered Latch

L1 L2 L

Ways to design an edge-triggered sequential cell:

© Digital Integrated Circuits2nd

Sequential Circuits

Pulsed LatchesPulsed Latches

CLKGD

VDD

M3

M2

M1

CLKG

VDD

M6

Q

M5

M4

CLK

CLKG

VDD

XMP

MN

(a) register (b) glitch generation

© Digital Integrated Circuits2nd

Sequential Circuits

Latch-Based PipelineLatch-Based Pipeline

F G

CLK

CLK

In Out

C1 C2

CLK

C3

CLK

CLK

Compute F compute G

© Digital Integrated Circuits2nd

Sequential Circuits

Non-Bistable Sequential Circuits─Non-Bistable Sequential Circuits─Schmitt TriggerSchmitt Trigger

In Out

Vin

Vout VOH

VOL

VM– VM+

•VTC with hysteresis•Restores signal slopes

© Digital Integrated Circuits2nd

Sequential Circuits

Noise Suppression using Schmitt Noise Suppression using Schmitt TriggerTrigger

Vin

t0

VM

VM

t

Vout

t0 + tp t

© Digital Integrated Circuits2nd

Sequential Circuits

Schmitt Trigger Simulated VTCSchmitt Trigger Simulated VTC

2.5

VM2

VM1

Vin (V)

Voltage-transfer characteristics with hysteresis. The effect of varying the ratio of thePMOS device M4 . The width isk* 0.5 m.m

2.0

1.5

1.0

0.5

0.00.0 0.5 1.0 1.5 2.0 2.5

2.5

k = 2k = 3

k = 4

k = 1

Vin (V)

2.0

1.5

1.0

0.5

0.00.0 0.5 1.0 1.5 2.0 2.5

© Digital Integrated Circuits2nd

Sequential Circuits

CMOS Schmitt Trigger (2)CMOS Schmitt Trigger (2)

VDD

VDD

OutIn

M1

M5

M2

X

M3

M4

M6

© Digital Integrated Circuits2nd

Sequential Circuits

MonostableMonostable

DELAY

td

In

Outtd

© Digital Integrated Circuits2nd

Sequential Circuits

Astable Multivibrators (Oscillators)Astable Multivibrators (Oscillators)

0 1 2 N-1

Ring Oscillator

simulated response of 5-stage oscillator

0.0

0.0

0.5

1.0

1.5

2.0

2.5V1 V3 V5

3.0

20.50.5

time (ns)

Volts

1.0 1.5

© Digital Integrated Circuits2nd

Sequential Circuits

Relaxation OscillatorRelaxation Oscillator

Out2

CR

Out1

Int

I1 I2

T = 2 (log3) RC

© Digital Integrated Circuits2nd

Sequential Circuits

Voltage Controller Oscillator (VCO)Voltage Controller Oscillator (VCO)

In

VDD

M3

M1

M2

M4

M5

VDD

M6

Vcontr Current starved inverter

Iref Iref

Schmitt Triggerrestores signal slopes

0.5 1.5 2.5Vcontr (V)

0.0

2

4

6

t pHL

(nse

c)

propagation delay as a functionof control voltage