The Belle II Silicon Vertex Detector Readout Chain Markus Friedl (HEPHY Vienna) TWEPP2012, 19...

-

Upload

sharon-thomas -

Category

Documents

-

view

225 -

download

31

Transcript of The Belle II Silicon Vertex Detector Readout Chain Markus Friedl (HEPHY Vienna) TWEPP2012, 19...

The Belle II Silicon Vertex Detector Readout Chain

Markus Friedl (HEPHY Vienna)

TWEPP2012, 19 September 2012

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 2

IntroductionFront-EndJunction BoxFADCDAQSummary

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 3

IntroductionFront-EndJunction BoxFADCDAQSummary

KEKB and Belle @ KEK (1999-2010)

Center of mass energy: Y(4S) (10.58 GeV)

High intensity beams (1.6 A & 1.3 A) Integrated luminosity of 1 ab-1

recorded in total Belle mentioned explicitly in 2008

Physics Nobel Prize announcement to Kobayashi and Masukawa

Linac

Belle

KEKB

~1 km in diameter

KEKBBelle

Linac

About 60km northeast of Tokyo

Asymmetric machine:8 GeV e- on 3.5 GeV e+

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 4

µ / KL detection 14/15 lyr. RPC+Fe

CsI(Tl) 16 X0

Si vertex detector 4 layers DSSD

SC solenoid 1.5 T

8 GeV e-

3.5 GeV e+

Aerogel Cherenkov counter n=1.015~1.030

Central Drift Chambersmall cell +He/C2H5

TOF counter

Belle Detector (1999–2010)

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 5

M.Friedl (HEPHY Vienna): Belle II SVD Readout

SuperKEKB/Belle II Upgrade: 2010–2015 Aim: super-high luminosity ~81035 cm-2s-1 11010 BB / year LoI published in 2004; TDR published in 2010 Refurbishment of accelerator and detector required

nano-beams with cross-sections of ~10 µm x 60 nm 10 mm radius beam pipe at interaction region

19 September 2012 6

http://belle2.kek.jp

Previous SVD Layout (until 2010)

4 straight layers of 4" double-sided silicon detectors (DSSDs)

Outer radius of r~8.8 cm Up to three 4” sensors are

daisy-chained and read out by one hybrid located outside of acceptance region (VA1 chip)

0

0

10

12

34

[cm]

layers

[cm]

20

-10-20-30 10 20 30 40

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 7

Belle Silicon Vertex Detector (SVD)

Current SVD is not suitable for Belle II

10%

L1

L2 L3 L4

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 8

10%

Previous SVD limitations were occupancy (~10% in innermost

layer) need faster shaping

dead time (~3%) need faster readout and pipeline

Belle II needs detector with high background tolerance pipelined readout robust tracking low material budget in active

volume

0

0

10

1+23

45

6[cm] layers

[cm]

20

-10-20-30 10 20 30 40

New Layout for Belle II SVD (2015-)

New double-layer pixel detector using DEPFET technology

Four layers with 6” double-sided strip detectors and forward part

Optimized for precision vertex reconstruction of the decays of short-lived B-mesons

Two layers of DEPFET pixels

4 layers of double-sided strip sensors

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 9

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 10

APV25 chips

Cooling pipe

Origami ladder

Sensor underneath flex circuit

Pitch adapter bentaround sensor edge

End ring (support)

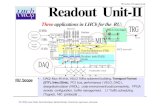

Readout Chain Overview

Analog APV25 readout is through copper cable to FADCs

Junction box provides LV to front-end

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 11

1748APV25chips

Front-endhybrids

Rad-hardDC/DC

converters

Analog level translation,data sparsification andhit time reconstruction

Unified Belle IIDAQ system

~2mcoppercable

Junctionbox

~10mcoppercable

FADCUnified optical

data link (>20m)

Finesse Transmitter Board (FTB)

CO

PPER

Not Entirely New…

2007: plans for an intermediate upgrade of Belle I SVD

Prototype system built and tested thoroughly in several beam tests since then

Now enlarging and improving details, but concept is same

See reports at previous TWEPPs for details & performance

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 12

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 13

IntroductionFront-EndJunction BoxFADCDAQSummary

APV25 Readout Chip

Developed for CMS (LHC) by IC London and RAL (70k chips installed)

0.25 µm CMOS process (>100 MRad tolerant) 40 MHz clock (adjustable), 128 channels 192 cell analog pipeline no dead time 50 ns shaping time low occupancy Noise: 250 e + 36 e/pF must minimize capacitive load!!! Multi-peak mode (read out several samples along shaping curve) Thinning to 100µm successful

Schematics of one channel

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 14

Front-End Hybrids 2 variants

Standard PCBs outside acceptance for the edge sensors

“Origami” chip-on-sensor concept for inner sensors

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 15

See presentation by C. Irmler today at 14:50 Martin Wood Lecture Theater

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 16

IntroductionFront-EndJunction BoxFADCDAQSummary

Junction Box: Mother Board

Junction box board with CERN DC/DC converters to be placed in SVD DOCK boxes

Converter boards now have a commercial chip, to be replaced by the rad-hard AMIS5 chip

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 17

DC/DC Converter: Noise Comparison

Same noise within measurement precision (few %) between conventional and DC/DC powering!

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 18

0 1 2 30

100

200

300

400

500

600 APV25 Noise (old hybrid only) Conven-

tionalDC/DC

APV#

Nois

e [

e]

(known problem)

0 1 2 30

100

200

300

400

500

600 APV25 Noise (new hybrid only)Conventional DC/DC

APV#

Nois

e [

e]

Test hybrid(larger)

Belle II design(smaller)

Junction Box: Draft Design (Top lid not

shown) As in Belle 1

SVD: Located ~2m from front-end (outside acceptance) = radiation zone

Mostly aluminum, only bottom plate copper (to be cooled)

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 19

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 20

IntroductionFront-EndJunction BoxFADCDAQSummary

Readout Electronics: Scheme

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 21

Power Supplies(floating)

FADC

Junction Box

Detector

AP V25

HV LV

No direct connection between power supplies and FADC

Bias currents are measured remotely by FADC

FADC Block Diagram

Analog & digital level translation between bias and GND Digitization, signal conditioning (FIR filter), data processing Central FPGA is an Altera Stratix IV GX 19 September

2012M.Friedl (HEPHY Vienna): Belle II SVD Readout 22

Lev

el T

ran

slat

ion

AD

Cs

Mon

itorin

g

CentralFPGA

VM EFPGA

JitterCleaner

Delay

VM E bus

GbE

FA DC Controller

FTB

Jun

cti

on

Bo

x

Signals

CLK

Contro ls

S lowContro ls

Data

Data

Contro ls

V/I

HV LV

FIR

FADC: Overall Concept

Similar to Belle 1 SVD FADC, but with twice higher density (48 APV25 inputs) and more powerful FPGA

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 23

Ind ica torLED s

H ybridC onnectors

V M EA ltera

S tra tix 4 G Xdaughter board

P 1

P 2

B us

G bE

P 3

A nalogleve ltranslation

FE contro l& m onito ring

D ig ita l(contro ls)leve ltranslation

A D C s

D elay

D elay

Jitte rC leanerC LK

distribu tion

C LKdistribu tion

FADC: Level Translation Daughter Boards Analog board: existing design, but simplified Digital board: completely new design based on

digital isolator ICs (Analog Devices) No floating LV power needed for either board!

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 24

FADC: Level Translation Tests

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 25

Both boards tested thoroughly, working perfectly fine Short (2m) and long (12m) cable to FADC 100V between floating and GND sides No damage with repeated instantaneous shorting of HV

APVDAQ RepeaterAna+Digi daughter boardson adapter board

APV25 Hybrid

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 26

IntroductionFront-EndJunction BoxFADCDAQSummary

Finesse Transmitter Board (FTB)

Sends FADC data through optical link to COPPER Pixel system

(for online data reduction)

Firmware in development

12 November 2011Markus Friedl (HEPHY Vienna): Status of SVD 27

COPPER = Common Readout Platform

Standardized 9U VME crate with CPU and network interface

4 slots for FINESSE daughter boards (ADC, TDC, …) according to subsystem needs In case of SVD: Belle2Link (Optical receiver)

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 28

F IFO

F IFO

F IFO

F IFO

M em ory

C PU

B rid ge

L oca l B u s P C I B us

Det

ecto

r S

ign

als

F IN E SSE

F IN E SSE

F IN E SSE

F IN E SSE

Trigger in pu tTrigger in terrup t

B rid ge

M ezzan ine C a rds

P C I M ezzan in e C ard s

C ontro l B rid ge

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 29

IntroductionFront-EndJunction BoxFADCDAQSummary

Overall Readout System Scheme

DAQ: PC Farm

COPPER: common readout platform

FADC system with optical link to COPPER

DOCK box with DC/DC

Front-End

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 30

FADC_Contro ller

Buffer FADC

JunctionBoard

HV + LVPower

FTB

Hybrid Hybrid

CopperF inesse

CopperF inesse

FTB

FADC

JunctionBoard

Backplane Bus

3 m ore FADC crates

FADCVM E Crate

DO CK B ox

CopperVM E Crate

DA Q

Summary & Outlook Belle I Belle II

Needs completely new vertex detector (pixel + strips)

Readout Chain Based on a 2007 design (for an earlier update

option) “Origami” chip-on-sensor concept for front-end

with APV25 Junction box near front-end with rad-hard DC/DC

converters No noise penalty from switching power

FADC with powerful FPGA for online signal processing Level translation daughter boards – working fine

DAQ link to common readout platform Will report on performance at next TWEPP

19 September 2012

M.Friedl (HEPHY Vienna): Belle II SVD Readout 31