LPDDR3 and Wide I/O DRAM: Interface Changes that give … · Marc Greenberg, Director, Product...

-

Upload

hoangduong -

Category

Documents

-

view

216 -

download

0

Transcript of LPDDR3 and Wide I/O DRAM: Interface Changes that give … · Marc Greenberg, Director, Product...

Marc Greenberg, Director, Product Marketing - Memcon 2012 San Jose Sept 18, 2012

LPDDR3 and Wide I/O DRAM: Interface Changes that give PC-Like Memory Performance to Mobile Devices

2 © 2012 Cadence Design Systems, Inc. All rights reserved.

• What is PC-like Memory Performance? • Common PC memory configurations • Low-power Alternatives • Comparative Metrics • How did LPDDR3 evolve? • How did Wide I/O evolve? • Future low-power memory direction

Agenda

3 © 2012 Cadence Design Systems, Inc. All rights reserved.

Memory implementation by manufacturer* Number of bits in DRAM interface / Interface data rate

Computer Type Price Range

Company 1

Company 2

Company 3

Company 4

Company 5

Tablet / Small $300-$550 64/800** 128/800** 128/1333** 128/800**

Thin & Light $700-$700 64/1600 64/1600 64/1333** 64/1333**

Entry Laptop $450-$500 64/1333** 128/1333 128/1333** 128/1333

Power Laptop $1250-$1500 128/1600** 128/1600 128/1600 128/1333** 128/1600

Entry Desktop $275-$330 64/1600 64/1600 128/1333 64/1333

Power Desktop $1200-$2500 256/1333 256/1600 192/1333 128/1333 128/1600

What is PC-Like Memory Performance?

* Computers selected are the author’s opinion of indicative computers within the price range by a survey of websites of five large computer manufacturers in September 2012 and do not necessarily indicate the best, lowest cost, or most representative computer in the price range from each manufacturer ** Exact specification not available on manufacturer website; this number is estimated

4 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Company 1 Company 2 Company 3 Company 4 Company 5

Common PC Memory Configurations

5 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Company 1 Company 2 Company 3 Company 4 Company 5

Common PC Memory Configurations

All the Top PC manufacturers have a machine in the 100Gbit/s range today

6 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Company 1 Company 2 Company 3 Company 4 Company 5

Common PC Memory Configurations

The majority of computing jobs are now in the 150-200Gbit/sec range

7 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Company 1 Company 2 Company 3 Company 4 Company 5

Common PC Memory Configurations

Longer-term, mobile devices are going to be expected to perform like gaming PCs of today

8 © 2012 Cadence Design Systems, Inc. All rights reserved.

• Mobile devices are becoming like our PC devices – 0.9+ Megapixel (approximately 1280*720) or better resolution now

common in high-end smartphones – 300+ pixels per inch

– 3+ Megapixel (approximately 2000*1600) tablets appearing – The 22” LCD monitor on my desk is only 1680*1050

• Consumers beginning to expect mobile entertainment experience to be like their wired entertainment experience

• 4K Video (8+ Megapixels - 3840*2160) and 3D are coming – A small number of 4K TVs already for sale – A 10” tablet with 480 pixels per inch could display 4K video – Approximately 25-50Gbit/s of video traffic to DRAM for video decode – High-end desktop graphics cards capable of 4K operation have

250-300Gbit/s of memory bandwidth

Mobile Devices become like our PCs

9 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Company 1 Company 2 Company 3 Company 4 Company 5

Common PC Memory Configurations

10 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Company 1 Company 2 Company 3 Company 4 Company 5

Common PC Memory Configurations

Current Generation Tablets

Next Generation Smartphone

Current Generation Smartphone

Next Generation Tablets

11 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Low Power Memory - Today

Current Generation Tablets

Next Generation Smartphones

Current Generation Smartphones

Now In design now Shipping 2013-2015

Next Generation Tablets

Concept Phase Shipping 2015+

12 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Current Generation Tablets

Next Generation Smartphones

Current Generation Smartphones

Next Generation Tablets

Low Power Memory - Today

Now In design now Shipping 2013-2015

Concept Phase Shipping 2015+

13 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

0

50

100

150

200

250

300

350

400

450

Current Generation Tablets

Next Generation Smartphones

Current Generation Smartphones

Next Generation Tablets

Current Generation Tablets

Next Generation Smartphones

Current Generation Smartphones

Low Power Memory - Today

Next Generation Tablets

Now In design now Shipping 2013-2015

Concept Phase Shipping 2015+

14 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

0

50

100

150

200

250

300

350

400

450

Current Generation Tablets

Next Generation Smartphones

Current Generation Smartphones

Low Power Memory - Today

Next Generation Tablets

Now In design now Shipping 2013-2015

Concept Phase Shipping 2015+

15 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Current Generation Tablets

Current Generation Smartphones

Low Power Memory - Today

Next Generation Smartphones

32bit LPDDR2-800 32bit LPDDR2-1066 64bit LPDDR2-800

64bit LPDDR2-1066

128bit LPDDR2-800

Now In design now Shipping 2013-2015

Concept Phase Shipping 2015+

Next Generation Tablets

DDR3L now appearing in some tablets

16 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Current Generation Tablets

Current Generation Smartphones

Low Power Memory Future - Parallel

Next Generation Smartphones

32bit LPDDR2-800 32bit LPDDR2-1066 64bit LPDDR2-800

64bit LPDDR2-1066

128bit LPDDR2-800 64bit LPDDR3-1600

Now In design now Shipping 2013-2015

Concept Phase Shipping 2015+

32bit LPDDR3-1600

Next Generation Tablets

64bit DDR-3200 Possible Future

Standard DDR3L now appearing in some tablets

128bit LPDDR3-1600

64-bit Possible LPDDR3 speed extension

17 © 2012 Cadence Design Systems, Inc. All rights reserved.

• Low Voltage • Low I/O Capacitance • Unterminated I/Os • Typically X16 or X32 data width per die • Often contained in multi-die packages • No DLL • Fast low-power entry and exit • Very low standby (self-refresh) power • Temperature Compensated Self-Refresh mode • Deep Power Down mode • Partial Array Self-Refresh

Low Power DRAM – Typical Features

18 © 2012 Cadence Design Systems, Inc. All rights reserved.

• DDR3L is a lower-voltage version of PC DRAM • Appearing in many laptops and some tablets

Low Power LPDDR vs Low Voltage DDR3L

Attribute LPDDR2/LPDDR3 DDR3L Target Market Mobile Devices Laptop, Desktop, Server IO Specification 1.2V HSUL 1.35V SSTL Command/Addressing 10 pin DDR bus ~22 pin SDR bus Target system Point-to-point DIMM Max I/O Capacitance 2.5pF/1.8pF 2.5pF Max Frequency 1066MTs/1600MT/s 1600MT/s Typical Idle Power* 103mW 115mW Typical self-refresh Power* 5mW 16mW

* Comparison of two 2Gbit DDR-800 X16 parts from the same manufacturer

19 © 2012 Cadence Design Systems, Inc. All rights reserved.

• Compared to packaged parts on PCB, PoP can reduce power, area, and volume – Short paths with relatively good signal integrity properties – Saves PCB area by using vertical direction – May lead to thermal issues if die underneath is generating heat

LPDDR2 and LPDDR3 (PoP) Package-on-Package (PoP) offers low power and area

Upper die (for example, DRAM) Flipchip bumps to upper package PCB Upper package PCB Package balls connect upper and lower PCBs Lower die (for example, CPU or app processor) Lower Package PCB with landing pads on top Package balls System PCB

Example cross-section - Not to scale

20 © 2012 Cadence Design Systems, Inc. All rights reserved.

• During the standardization of LPDDR2, the frequency limit of High Speed Unterminated Logic (HSUL) device with no DLL retiming was believed to be 1066MT/s per pin

• Three main innovations allowed the LPDDR3 standard to go to 1600MT/s with a possible extension to 2133MT/s

• I/O Capacitance directly affects the maximum frequency – LPDDR3 I/O Capacitance was reduced compared to LPDDR2

allowing more speed with less power

• Signal Integrity Issues – Addition of (optional) On-Die Termination (ODT) to LPDDR3 allows

more speed but at higher power

• Interface Training – New training modes added

LPDDR2 to LPDDR3 transition

21 © 2012 Cadence Design Systems, Inc. All rights reserved.

LPDDR2 LPDDR3 Specification release 2009 Specification release May 2012 DDR-1066 (533MHz) DDR-1600 (800MHz) – 50%

increase 1.2v HSUL Unterminated I/Os

1.2v HSUL I/O with optional On-Die Termination (ODT)

Read training Read training, Command/Address (CA) training and Write Leveling

I/O Capacitance 2.5pF I/O Capacitance 1.8pF Low Power consumption Expected to be less per bit from

lower I/O capacitance and more advanced process

How to get from LPDDR2 to LPDDR3

22 © 2012 Cadence Design Systems, Inc. All rights reserved.

Understanding LPDDR3 and Wide I/O

Attribute LPDDR3 Wide I/O Specification Release May 2012 December 2011 Bandwidth per die 51.2Gbit/s (X32) 102.4Gbit/s Bandwidth per package 102.4Gbit/s

(64-bit dual-channel) 102.4Gbit/s

Dies per package Up to 4 (in theory) Up to 4 (in theory) System configurations PoP or normal PCB

interconnect Silicon Interposer or direct chip-to-chip

General Improved, Evolutionary Technology

New, Revolutionary Technology

Compatibility Backwards compatible with LPDDR2

May be forwards compatible with future standards

23 © 2012 Cadence Design Systems, Inc. All rights reserved.

Understanding LPDDR3 and Wide I/O

• LPDDR3

• Utilizing existing packaging techniques like Package on Package (PoP) in Smartphones

• Can be used in chip-on-board applications (beginning to appear in some tablets)

Package-on-Package Through-Silicon Via

• Wide I/O

• Use a very large number of slow, lower power pins for high bandwidth

• Utilizing new Through Silicon Via (TSV) wafer processing

24 © 2012 Cadence Design Systems, Inc. All rights reserved.

Wide I/O DRAM

JESD229 Standard 4 128-bit channels Total 512bits to DRAM 200MHz SDR 100Gbit/s bandwidth

Possible Future Standard 4 128-bit channels 256-512bits to DRAM? 266MHz DDR? 266-533Gbit/s bandwidth?

Possible Future non-mobile 4 128-bit channels? Total 512bits to DRAM? 1066MHz DDR (2133MT/s)? 1Tbit/s bandwidth?

Possible Future non-mobile 2Tbit/s bandwidth? Bandwidth

Possible time of introduction

25 © 2012 Cadence Design Systems, Inc. All rights reserved.

Using Through Silicon Vias (TSV) for DRAM

Bump pitches represent minimum practical pitch Refer to JEDEC Standard for Wide-IO diameter and pitch

26 © 2012 Cadence Design Systems, Inc. All rights reserved.

General Benefits of TSVs

Number of connections Capacitance per connection

Average Connection Length

Relative power (proportional to f, c, #

connections)

PCB or PoP

Silicon Interposer

Direct C2C stacking

Impr

oved

~10

X

Impr

oved

~6X

Impr

oved

~20

0X

Impr

oved

~6X

27 © 2012 Cadence Design Systems, Inc. All rights reserved.

Wide-IO DRAM Controller and PHY

Challenges Solutions

Merge existing and new technology

• Start with high performance, low power base architecture

• Re-add SDR support • Add new Wide-IO feature support • Create DFI extensions for Controller-PHY connection

New testing requirements

• Extend BIST engine to test for new classes of error introduced by TSV

Verification • Create memory model of Wide-IO device • Extend verification environment for Wide-IO

PHY • Lightweight PHY, or PHY suitable for characterization? • Next generation: probably needs PHY again

I/Os • Need appropriate IOs • ESD?

28 © 2012 Cadence Design Systems, Inc. All rights reserved.

What are the challenges?

Manufacturing Wide-IO DRAM and assembly: § Test Memory Wafer after production using FC bumps § Thin the wafer to ~50-100um thickness § Form TSVs and fill with metal

§ Requires elevated temperatures – extra anneal step § Apply backside metal and bumps § No opportunity to test here

§ Backside metal bump pitch too fine for most tester heads § Handle dies while avoiding mechanical damage

§ They are now the approximate aspect ratio of a postage stamp § Attach dies (and interposers, if present) together § Does it still work?

29 © 2012 Cadence Design Systems, Inc. All rights reserved.

What are the Wide-IO challenges?

Thermal Issues: • Where does the heat go? • Some new tablets placing LPDDR2 DRAM on opposite

side of board from CPU instead of PoP Ecosystem Issues: • New Technology • How many parties involved in stack production? • How are responsibilities divided? • How are liabilities divided?

30 © 2012 Cadence Design Systems, Inc. All rights reserved.

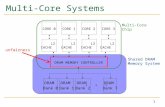

SoC Construction

Channel A Data

Channel A Cmd

Channel A D

ata

LPDDR3: - PoP Ballout dictates SoC Construction - Command and data separated 5-15mm on the SoC? - Extra pipeline flop stages required to transmit data edge to edge; adds latency and power

Channel A Channel B Memory Controller

Channel D Channel C

Wide I/O: - TSV Ballout dictates SoC Construction - Each channel contained within 2.5mm - May be possible to reach all IOs within channel without pipelining

Note: Only one channel shown

CPU

CPU

CPU Memory

Controller

CPU Memory

Controller

Memory Controller

Memory Controller

CPU CPU

CPU

CPU

31 © 2012 Cadence Design Systems, Inc. All rights reserved.

Attribute LPDDR3 2Channel Wide I/O Peak Bandwidth 102Gbit/s 102Gbit/s Core power Predicted to be similar for both technologies I/O Voltage 1.2V 1.2V I/O Capacitance 1.8pF 0.5pF Full-bandwidth, all chip I/O Power (1/2 f c v2)

64*0.5*1600*cv2 = 51200cv2

512*0.5*200*cv2= 51200cv2

First-order approximation: the difference in IO power is proportional to c Powerdown, Self-Refresh and DPD capability

One power state for each channel, one channel per die, 1-2 channels per system

4 channels per die

SoC Power PHY may require DLL/PLL DLL/PLL not required

System Power Comparison

32 © 2012 Cadence Design Systems, Inc. All rights reserved.

• Silicon Interposer dies on stand at DAC in June 2012 • Cadence Wide-IO DRAM Controller

– Includes expanded MBIST tests for Wide-IO – Deployed on two projects – Proven in silicon – First IP solution to market – first deliveries in November 2010

• Cadence Wide-IO PHY – Deployed on one project – first delivery August 2011

• Cadence Wide-IO Memory Models (Verification IP) • Foundry Reference Flows contain Cadence 3D-IC support

Wide-IO Maturity and Ecosystem

33 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Current Generation Tablets

Current Generation Smartphones

Low Power Memory Future – Wide I/O

Next Generation Smartphones

32bit LPDDR2-800 32bit LPDDR2-1066 64bit LPDDR2-800

64bit LPDDR2-1066

128bit LPDDR2-800 64bit LPDDR3-1600

Now In design now Shipping 2013-2015

Concept Phase Shipping 2015+

32bit LPDDR3-1600

Next Generation Tablets

64bit DDR-3200 Possible Future

Standard DDR3L now appearing in some tablets

128bit LPDDR3-1600

64-bit Possible LPDDR3 speed extension

Wide I/O 1 (SDR)

Dual-Die Wide I/O ?

Possible Future Standard

34 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Current Generation Tablets

Current Generation Smartphones

Low Power Memory Future – Wide I/O

Next Generation Smartphones

32bit LPDDR2-800 32bit LPDDR2-1066 64bit LPDDR2-800

64bit LPDDR2-1066

128bit LPDDR2-800 64bit LPDDR3-1600

Now In design now Shipping 2013-2015

Concept Phase Shipping 2015+

Next Generation Tablets

DDR3L now appearing in some tablets

128bit LPDDR3-1600

Wide I/O 1 (SDR)

Dual-Die Wide I/O ?

Possible Future Standard

35 © 2012 Cadence Design Systems, Inc. All rights reserved.

0

50

100

150

200

250

300

350

400

450

Current Generation Tablets

Current Generation Smartphones

Next Generation Smartphones

32bit LPDDR2-800 32bit LPDDR2-1066 64bit LPDDR2-800

64bit LPDDR2-1066

128bit LPDDR2-800 LPDDR3

Now In design now Shipping 2013-2015

Concept Phase Shipping 2015+

32bit LPDDR3-1600

Next Generation Tablets

64bit DDR-3200 Possible Future

Standard DDR3L now appearing in some tablets

128bit LPDDR3-1600

64-bit Possible LPDDR3 speed extension

Wide I/O

Possible Future Standard

Low Power Memory Future – Coexistence

36 © 2012 Cadence Design Systems, Inc. All rights reserved.

• The mobile memory future contains both LPDDR and Wide I/O – LPDDR3: Evolutionary and proven, but more power – Wide I/O: New and exciting, with less power

• Cadence Memory Solutions include: – LPDDR3/LPDDR2/DDR4/DDR3 Controller and PHY – Wide I/O Controller and PHY – Flash Controller and PHY – Memory Models – Verification IP – Signal Integrity Reference Designs – Design, Verification, Physical Verification, and Test tools for

TSV-based chip designs

Conclusion

37 © 2012 Cadence Design Systems, Inc. All rights reserved.