Lecture 9: Photolithography

Transcript of Lecture 9: Photolithography

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

1/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Lecture 9: PhotolithographyChapter 2 Jaeger

2/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Announcements

• Is online now:

• Email [email protected] and

Homework 1/4:

• http://classes.engr.oregonstate.edu/eecs/spring2021/ece4

18-001/homework.html

• Because we are a little behind with the lectures, the homework

deadline has been extended by 2 days.

• Now due Friday 16th April 4:00 pm.

• Will be online after the Lectures on Wednesday 21st April.

Homework 2/4:

1

2

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

3/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Last Time𝑉 ≫ 0

𝑑

ℎ+ ℎ+ ℎ+ ℎ+ ℎ+ ℎ+ ℎ+ℎ+ ℎ+ ℎ+

𝑊

𝐶𝑖𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑁𝐴

−

𝑒− 𝑒−𝑒− 𝑒− 𝑒−𝑒− 𝑒− 𝑒−𝑒− 𝑒−

𝐶

𝑉Accumulation

𝐶𝑖

Depl. Inversion

Low

Freq.

High

Freq.

• We looked at MOS

Capacitors and their CV

characteristics.

4/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Useful Links

Berkley:

• http://www-inst.eecs.berkeley.edu/~ee143/fa10/lectures/Lec_04.pdf

University of Michigan:

• http://web.eecs.umich.edu/~peicheng/teaching/EECS598_06_Winter/Lectu

re%2016%20-%20Mar%2009.pdf

MIT:

• http://www-

mtl.mit.edu/researchgroups/hackman/6152J/SP_2004/lectures/sp_2005_Le

cture09.pdf

KTH:

• https://www.kth.se/social/upload/4f3d0e38f276545a2b000003/Lecture%20

9%20Litho.pdf

This subject is widely taught, and online notes are available from

many sources. Here are some good examples:

3

4

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

5/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Lecture 9• Overview of Photolithography.

• Photoresists.

• Photoresist Deposition.

• Exposure.

• Development.

6/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Overview of

Photolithography

5

6

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

7/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

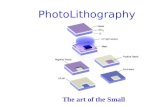

Photolithography• A lot of the processes we will

talk about in this class are

vertical.

• E.g. etching, diffusion,

oxide growth etc.

• However, at some point we will need to define lateral features.

• E.g. we may wish to have an oxide in one position and not

in another.

• Almost ubiquitously,

lateral features are

patterned using the

technique of

photolithography.

Film

Substrate

Resist

SubstrateSubstrate

Film

8/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

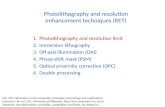

Patterning Wafers• Overall the process of patterning a wafer can be broadly

divided into 3 steps:

Mask Design Wafer ExposureMask Writing

• We are interested in the process of wafer exposure.

• In the lab you would have been using pre-designed masks to

carry out photo-lithography.

7

8

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

9/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

• Process the exposed part of the wafer.

Photolithography in One Slide• Apply photoresist (PR).

DevelopEtchStrip

Expose

Mask

• Expose PR through a patterned mask or reticle.

• Develop PR by immersing it in a solvent which preferentially

dissolves the PR of higher solubility.

• Strip away the remaining photoresist.

• Inspect pattern.

Ap

plyPR

SubstrateFilm

10/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photo room

Photolithography Process Flowchart

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

• A few different process flows exist for photolithography.

• Today we will follow the process describe by Jaeger.

• The lab process at OSU is slightly adjusted from this.

9

10

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

11/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Cleaning• We have covered

cleaning previously

(Lecture 3).

Cleaning

solution

Wafers

• The standard process is

the RCA clean that we

talked about in Lecture 3.

• Most processes are proprietary and depend on the exact

application.

• In our labs sessions you

would have carried out the

AMD Clean:

• Acetone, Methanol (or

isopropanol), DI H2O.

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

12/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

Film Growth• The next stage in the

process is to grow the

“barrier layer”.

• This is the layer we wish

to pattern.

• It could be an insulator

such as SiO2 or Si3N4, or it

could be an metal (e.g. Cu).

• The process depends on

the material (and

application.

• We will discuss these

processes in future lectures.Si

SiO2SiO2

Pre-Deposition

Dopant gas

11

12

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

13/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photoresists

14/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photoresists• Photoresist (PR): An organic compound (often a polymer) with

a photoactive component (PAC) whose solubility changes

upon exposure to radiation (light).

• Positive Photoresist:

• Irradiated regions become more soluble than non-

irradiated regions.

Expose

Mask

DevelopEtchStrip

More soluble

regions

hnN2

R

O

R

CO

+ N2

13

14

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

15/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photoresists• Photoresist (PR): An organic compound (often a polymer) with

a photoactive component (PAC) whose solubility changes

upon exposure to radiation (light).

• Negative Photoresist:

• Irradiated regions become less soluble than non-irradiated

regions.

Expose

Mask

More soluble

regions

DevelopEtchStrip

hnSU8

Cross-linked

polymer

16/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Comparison of Photoresists

Characteristic Positive Negative

Adhesion to Silicon Fair Excellent

Relative Cost More expensive Less expensive

Developer Base Aqueous Organic

Solubility in the

developer

Exposed region is

soluble

Exposed region is

insoluble

Minimum Feature 0.5 µm 2 µm

Step Coverage Better Lower

Wet Chemical

ResistanceFair Excellent

15

16

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

17/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Key Parameters of a Photoresist• Resolution: The smallest opening or island structure that can

be made under a given set of process conditions (related to

contrast).

• Registration: Overlay accuracy from layer to layer.

• Sensitivity: The number of photons it takes to cause the

chemical response in the PR. A resist is more sensitive if it

takes a lower dose to reproduce the mask geometry on the

wafer.

• Shelf life: The time you can reliably store a PR.

• Etch Resistance: The ability of the resist which remains on the

wafer after it is patterned to withstand the process

environment that the exposed wafer is subjected to.

18/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photoresist Deposition

17

18

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

19/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photoresist Deposition• The next stage is to deposit

the photoresist.

• Photoresist (in solution) is

deposited onto center of

wafer.

• Wafer is rotated and material is spread out by centrifugal

force.

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

• Photoresist is normally

deposited by spin-coating.

20/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photoresist Deposition1). Photoresist (in solvent) is

deposited in center of the

wafer. Wafer is held in

place with vacuum chuck.

2). Wafer is rotated slowly

(200 rpm) to distribute

material.

3). Accelerate the wafer to

final speed (~5000 rpm).

Spin the wafer at constant

speed for 30 – 60s. Forms

a uniform film and

evaporates solvent.

19

20

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

21/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photoresist Deposition• Industrially this is done with robotic arms and automated

dispensers:

• Extremely uniform films can be deposited using spin coating

(rms roughness ~ Å’s)

22/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Film Thickness• It can be shown (we won’t) that the final film thickness

depends on the spinning speed via:

𝑡 ∝1

𝜔Film

thickness

Angular

velocity

• Actual thickness will also

depend on:

• Concentration.

• Solvent evaporation

rate

• Viscosity.

• Local temperature.

• Local humidity.

21

22

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

23/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Pre-Bake• After the photoresist is

deposited, it is then

annealed in what is called

either pre-baking or soft-

baking.

• The photoresist is

deposited in solution (i.e. it

is dissolved in a solvent).

• To remove the solvent the

wafer is heated to ~100˚C.

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

• This is done on a standard

or purpose-designed

hotplate.

24/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Exposure

23

24

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

25/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Mask Alignment • To define features on our

wafer we need to develop

the photo-resist in certain

regions and not in others.

• For this to occur we need

to expose only certain

regions of the wafer.

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

• This is done via a mask.

• The mask is basically like a

stencil, that blocks the light

in certain regions and not

others.

• Normally it is a metal

(opaque) on quartz

(transparent).

26/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Mask Alignment • Before exposure we place the mask in front of the wafer.

• However, certain processes require multiple lithography steps.

• For example in your FET processing procedure you would

carry out 4 photolithography steps.

• We need the features of

each step to be correctly

aligned.

• This is a non-trivial

problem, and requires

specialist equipment:

• A mask aligner tool is used.

25

26

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

27/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Mask Alignment • We will not cover mask alignment in depth today because you

will be given more details in your lab documents.

• But in general, you will purposely define features in step 1,

that are used to align the mask in step 2 (for example).

Cross patterned

on mask in Step 1

Box on mask for

Step 2

Need to align

cross in box

28/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Mask Alignment • For the small feature sizes used in industry (<100nm) an

automated mask alignment system is used.

• For the MOSFET part of your project, you would have been

aligning masks using a manual tool.

https://www.youtube.com/watch?v=sl1-5-EviR0

27

28

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

29/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Exposure• After we have aligned

the mask, the sample is

then exposed to light.

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

• UV light is required for

most photoresists.

• Traditionally, mercury vapor lamps were employed for

photolithography.

30/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Modern Light Sources• Nowadays for projection

printing, and excimer laser is

employed:

LaserEmission

Wavelength (nm)Resolution (μm)

Max Energy (mJ /

Pulse)

Repetition Rate

(pulses / second)

KrF 248 0.18 - 0.25 300 – 1500 150

ArF 193 0.10 – 0.13 175 – 300 400

F2 157 < 0.1 6 10

• These are pulsed lasers.

29

30

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

31/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Exposure Techniques• Three approaches are typically taken to exposure:

Mask

Contact

Printing

• Defects

• Bowing of mask

Mask

Proximity

Printing

space

(≈25 mm)

• 2 -4 μm resolution

2-5 X

reduction

Mask

lens

Projection

Printing

1:1 Printing

Printing System Magn. Resolution (μm) Use

Contact 1 0.1 – 1 Research

Proximity 1 2 – 4 Low Cost

Projection 2-5 0.1 - 1 Mainstream VLSI

32/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Diffraction• Modern lithography tools are limited by the spreading of light

(and not their optical elements)

• Light passing through an aperture of similar dimensions to

the wavelength of the incident light (λ~ 100’s nm), will result

in diffraction.

Divergent

light source Collimating

lens

Aperture

Diffraction pattern

(Airy disk)

31

32

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

33/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Diffraction• The type of diffraction observed depends on the mask-wafer

separation.

• Hard-contact: (almost) no diffraction.

• Proximity: Near field (Fresnel) diffraction.

• Projection: Far field or (Fraunhofer) diffraction.

34/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Diffraction• The difference between Fresnel (near field) and Fraunhofer (far

field) is defined by the dimensionless Fresnel number (𝐹):

𝐹 =𝑊2

𝐿𝜆

• Where:

• 𝑊 is size of the aperture.

• 𝐿 is the distance of the screen (wafer) from the aperture.

• 𝜆 is the wavelength of the incident light.

• We define:

• 𝐹 ≫ 1 as Fresnel diffraction.

• 𝐹 ≪ 1 as Fraunhofer diffraction.

33

34

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

35/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Fresnel Diffraction• Fresnel (near field) occurs in proximity printing.

𝐿

• Minimum resolvable feature size is:

𝑊𝑚𝑖𝑛 = 𝑘𝐿𝜆

• Where:

• 𝑘 is an experimental parameter associated with the

process conditions.

36/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Example• Determine the minimum feature size when exposing a wafer

to i-line irradiation, using a mask 25 μm from the surface of

the wafer. Assume for this example 𝑘 = 1.

• From before we know the wavelength of the i-line is 𝜆𝑖 = 365

nm.

𝑊𝑚𝑖𝑛 = 𝑘𝐿𝜆

• Work in microns: 𝜆𝑖 = 0.365 μm.

𝑊𝑚𝑖𝑛 = 1 × 25 × 0.365

𝑊𝑚𝑖𝑛 = 3 μm

35

36

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

37/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Fraunhofer Diffraction• Fraunhofer (far field) occurs in projection printing.

𝑓 = Focal

length

𝑑 = Lens

diameter

38/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Fraunhofer Diffraction• Diffraction pattern from a single circular opening:

𝑓 = Focal

length

𝑑 = Lens

diameter

𝜆 =

Wavelength

of incident

light

37

38

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

39/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Fraunhofer Diffraction• We can think of a mask as a diffraction grating:

Divergent

light source Collimating

lens Mask

(diffraction

grating)

• Each aperture in mask acts as a point source.

40/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Fraunhofer Diffraction• We can think of a mask as a diffraction grating:

Divergent

light source Collimating

lensMask

• Each aperture in mask acts as a point source.

Focusing

lens Photoresist

on wafer

39

40

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

41/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Fraunhofer Diffraction• The resolution in Fraunhofer diffraction is defined by the

Rayleigh criterion.

• Rayleigh Criterion: when the

peak of one projection lands on

the first zero of the other.

42/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Fraunhofer Diffraction• The resolution in Fraunhofer diffraction is defined by the

Rayleigh criterion.

• Rayleigh Criterion: when the peak of one projection lands on

the first zero of the other:

41

42

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

43/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Fraunhofer Diffraction• The resolution in Fraunhofer diffraction is quantified by the

Rayleigh Criterion (𝑅):𝑓 = Focal

length

𝑑 = Lens

diameter𝑅 = 𝑘1𝜆𝑓

𝑑• 𝑘1 is an experimental parameter associated with the system

and resist (0.6 <𝑘1 < 0.8).

• The parameter Τ𝑑 𝑓 is sometimes called 𝑁𝐴 (numerical

aperture):

𝑁𝐴 =𝑑

𝑓= 𝑛sin𝛼

• 𝑛 = index of refraction (1 in air).

• 𝛼 = maximum half angle of

incident light:

𝑅 =𝑘1𝜆

𝑁𝐴

𝛼 = Maximum half-angle

44/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Development

43

44

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

45/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Development

• We now wish to dissolve the regions of the photoresist which

have higher solubility.

• Exposed regions (positive photoresist).

• Masked regions (negative photoresist).

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

• After exposure to UV light

we can assume the regions

of photoresist exposed are

either damaged (positive

photoresist) or

strengthened (negative

photoresist).

46/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Development• There are generally three strategies to development of

photoresist:

Immersion

Developing

develop solution

Wafers

pH and # of lots processed

are monitored

Spray Developing

Developer

fresh developer with each batch

Puddle Technique

fixed amount of developer

dispensed and rinsed

45

46

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

47/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Development• We need the following:

• Original thickness of positive resist should not be

measurably reduced.

• Development time should be short.

• Minimum pattern distortion (negative resists tend to

swell).

48/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Resist Contrast• Resist Contrast quantifies the ability of the resist to distinguish

light/dark in the aerial image.

• To evaluate it we plot the developed thickness (i.e. thickness

remaining after development) as a function of dose (𝑄).

Dose (mJcm-2) = Intensity (mW/cm-2) time (s)

𝑄 = 𝐼𝑡

𝑄0𝑄0

𝑄𝑓𝑄𝑓

47

48

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

49/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Resist Contrast• Quantitatively, the contrast is defined by 𝛾:

𝛾 =1

log10𝑄𝑓𝑄0

• Where:

• 𝑄0 is the onset of

exposure effect.

• 𝑄𝑓 is the dose at

which the exposure

is complete

Develo

ped

Th

ickn

ess

Log10(Q)

𝑄0𝑄0

𝑄𝑓

• 𝛾 is typically 2 – 10.

50/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Post-Bake• After the photoresist is

developed another

annealing step takes place.

• In this case the baking is to

strengthen the photoresist.

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

• A similar hotplate is used,

but the temperature is likely

to be a little higher (~130˚C

to 180˚C).

• This is called post-bake or

hard-bake typically.

49

50

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

51/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Processing• At this stage we should

have our features defined

as we want them.

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

• We can now process the

regions of the wafer we

wish to.

• We will cover the various processes as the course progresses.

• For example, we will talk about etching next time (Lecture 10):

Substrate

Film

Photoresist

Substrate

Film

Photoresist

52/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Photoresist Removal• Finally, when we have

completed out processing

we need to remove the

photoresist.

Photo room

Clean

Align

Masks

Grow Barrier

Layer (e.g. SiO2)

Expose

PrebakeApply

Photoresist

PostbakeDevelop

Process (Etch /

Implant/ Lift-off)

Remove

Photoresist

• This is another subject we

will not cover in detail here

as it depends on the

preceding steps.

• But generally you can

expect some sort of plasma

removal and at least one

more cleaning step (RCA

clean).

51

52

ECE418 / ECE518 – Spring 2021

Lecture 9 – Wednesday April 14th 2021

53/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Summary• We have looked at the basics of photolithography.

DevelopEtchStrip

Expose

Mask

54/54

ECE 418 / 518 – Semiconductor Processing

Spring 2021 - John Labram

Next Time…• After the break, we are going to look at etching.

Substrate: Si

SiO2

Photoresist

Solution

of reactants

Wafers

53

54