Day2.Combinational Logic

Click here to load reader

-

Upload

ron-liu -

Category

Technology

-

view

408 -

download

0

Transcript of Day2.Combinational Logic

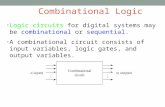

- 1. Logic & Combinational Logic

2. LAB: Logic Operationtest_counterdutcounter Stimulus and controlcount[7:0]clkresetenablecounter Responselogic_block logic_out monitorAverificationB logic_blockCC B A logic_out0 0 0 1 assign 0 0 1 1 !: NOT 0 1 0 10 1 1 1 &&: AND1 0 0 0 ||: OR 1 0 1 01 1 0 01 1 1 1 3. Decoder I1 I0 Y0 Y1 Y2 Y3 001000 010100 100010 110001 4. 7 segment decoder Binary a b c d e f g dp 0000 0 0 0 0 0 0 1 1 0001 1 0 0 1 1 1 1 1 ...... 5. MAX II 7 segment Common pin Segment pin LED 6. Verilog Codecase (in) 4'h0: seg_out = 8'b1100_0000; // 0 active low '0' 4'h1: seg_out = 8'b1111_1001; // 1 4'h2: seg_out = 8'b1010_0100; // 2 4'h3:4'h4: ...............................4'hf: default:end case; 7. LAB: Decodertest_counterdutcounter Stimulus and controlcount[7:0]clkresetenable counterResponse useled_dec monitor seg0 procedureverification timing control led_deca = seg(0); seg1b = seg(1);c = seg(2);d = seg(3);e = seg(4);f = seg(5);g = seg(6);dp = seg(7) 8. Encoder I0 I1 I2 I3 I4 I5 I6 I7 Y2 Y1 Y0 IDLE 00000000xxx1 100000000000 010000000010 IDLE = (!I0) * (!I1)....(!I7) = !(I0+I1+...I7) 001000000100 000100000110 Y0 = I1 + I3 + I5 + I7 000010001000 Y1 = I2 + I3 + I6 + I7 000001001010 Y2 = I4 + I5 + I6 + I7 ................ 9. Priotity Encoder I7 = R7I6 = R6 * (!R7)I5 = R5 * (!R6) * (!R7)......I0 = R0 * (!R1).....(!R7)Y0 = I1 + I3 + I5 + I7Y1 = I2 + I3 + I6 + I7Y2 = I4 + I5 + I6 + I7 10. Multiplexer, De-Mux 11. ComparatorAGTBOUT = (A>B) + (A=B) * AGTBINAEQBOUT = (A=B) * AEQBINALTBOUT = (A