Compal LA-6592P r10

-

Upload

krista-tran -

Category

Documents

-

view

279 -

download

25

description

Transcript of Compal LA-6592P r10

-

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Cover Sheet

1 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Cover Sheet

1 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Cover Sheet

1 75Thursday, January 13, 2011

Compal Electronics, Inc.

BOM P/N :

PCB NO :

COMPAL CONFIDENTIAL

MODEL NAME :

E3 MACALLAN 14" SG

rPGA Sandy Bridge +

FCBGA PCH Cougar Point-M

REV : 1.0(A00)

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

@ : Nopop Component

PAL51/53

LA-6592P (DAA00001V10)

43192931L01

2011-1-13

GPIO MAP: E3 Master GPIO Map10102010.xlsx

1@

2@

MB Type

TPM EN/ TCM DIS

TPM DIS/ TCM EN

BOM P/N

TPM DIS/ TCM DIS

1@

2@

ATG TPM EN/ TCM DIS

ATG TPM DIS/ TCM EN

ATG TPM DIS/ TCM DIS 2@

3@

3@

4@

43192931L01

43192931L02

43192931L11

43192931L12

2@

3@

3@

4@

CONN@ : ME controll and stuff by default

43192931L03

43192931L13

Part Number Description

DAA00001V10 PCB 0FE LA-6592P REV0 M/B DIS

MB PCB

Part Number Description

DAA00001V10 PCB 0FE LA-6592P REV0 M/B DIS

MB PCB

-

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

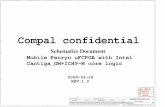

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

DIS Block Diagram

2 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

DIS Block Diagram

2 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

DIS Block Diagram

2 75Thursday, January 13, 2011

Compal Electronics, Inc.

PCI Express BUS

PCIE x1

MDC

HD Audio I/F

WWAN/UWB

HeadPhone &

MIC JackRJ45

S-ATA 0/1 6GB/s, S-ATA 2/3/4/5 3GB/s

1/2 Mini Card

WiFi ON/OFF &

Power ON/OFF SW

GUARDIAN III

EMC4022

Thermal

PCH XDP Port

CPU XDP Port

DC/DC Interface

LED

Memory BUS (DDR3)BANK 0, 1, 2, 3, 4 ,5 ,6 ,7DDRIII-DIMM X2

Touch Screen

KB CONNTP CONN

LPC BUS1/2 Mini Card

BCM5882

USHSmart Card

Lane x 8

FDI

RFID

W25X64ZE

16M 4K sector

HDD

SATA RepeaterMAX4951BE

USB7

E-Module Dig.

MIC

Trough eDP Cable

INT.Speaker

ECE5028

PCIE1PCIE3

TPM1.2

China TPM1.2

Lane x 4

USB6

PCIE5

PWM FAN

92HD90B2HDA Codec

DELL CONFIDENTIAL/PROPRIETARY

USB10

Trough eDP Cable

USB Port

Camera

USB

RJ11

LAN SWITCH

PI3L720

82579LM

Intel Lewisville

SATA RepeaterMAX4951BE

PCIE2

TDA8034HN

SSX44B

SATA

Flash

E-SATASATA

EXPRESSCard

BT

Option

SDXC/MMC/MSOZ600FJ0LN

Card reader

SPI

2560

2560

2062

To Docking side

on IO boardSMSC SIO

rPGA CPU

INTEL

DMI2

Sandy Bridge

BGA

COUGAR POINT-M

988 pins

4MB (Socket 988B)

BC BUS

Fingerprint

CONN

DAI

DOCK LAN

FP_USB

SMSC KBC

MEC5055

Full Mini CardWLAN

N12M-NSHDMI CONN HDMI Repeater

PS121

PEG

dLVDS

Compal confidential Model: PAL51/53Block Diagram

DPE

DPC

DPD

USB[8,9]

SATA5

DOCK LAN

DAI

DOCKING PORT

CRT CONN

dVGAVGA

1066/1333MHz

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

LVDS CONN

PAGE 6-11

PAGE 46-51

PAGE 14-21

On IO board

PAGE 40

PAGE 35

PAGE 14

PAGE 14

PAGE 33,34

PAGE 33

PAGE 41

PAGE 42

PAGE 43 PAGE 43

PAGE 29

PAGE 7

PAGE 14

PAGE 22

PAGE 31

PAGE 44

PAGE 45

PAGE 28

PAGE 28PAGE 30

PAGE 30PAGE 32

PAGE 32

PAGE 38

PAGE 38

PAGE 39

PAGE 39

PAGE 43

PAGE 24

PAGE 12,13

USB5USB4

100MHz

33MHz

W25Q16BVSSIG

64M 4K sector

100MHzPCI Express BUS

on IO board

iVGA

VGA

iLVDS

iLVDS

PAGE 23

LVDS SwitchPI3LVD400ZFEX

MAX14885EVideo Switch

PAGE 25

USB Port

USB Port

USB Port

on IO board

PCIE4

PAGE 24

PAGE 26PAGE 26

PAGE 35

PAGE 34PAGE 36PAGE 36PAGE 36PAGE 37

PAGE 33

PAGE 33

PAGE 23

PAGE 22

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Index and Config.

3 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Index and Config.

3 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Index and Config.

3 75Thursday, January 13, 2011

Compal Electronics, Inc.

PM TABLE

DELL CONFIDENTIAL/PROPRIETARY

MINI CARD-2 WLAN

PCI EXPRESS

Lane 1

DESTINATION

Lane 2

Lane 3

Lane 4

MINI CARD-1 WWAN

POWER STATES

Lane 5

Lane 6

Express card

MMI

+3.3V_M +3.3V_M

(M-OFF)

ON

ON

ON

ON

OFF

OFF

OFFOFF

+3.3V_SUS

+5V_ALW

+5V_RUN

+3.3V_ALW_PCH

+1.5V_MEM

S0

S3

S5 S4/AC don't exist

ON

powerplane

S5 S4/AC

State

OFFON

ON

ON

ON ON

OFF

OFF

OFF

OFFOFF

+15V_ALW

+3.3V_RTC_LDO

+1.05V_M

E3 Module Bay (USB3)

JESA1 (Ext Left Side )

JESA1 (Right Side ESATA)

WLAN

JMINI3(Flash)

WWAN

DOCKING8

9

USH->BIO

10 Express card

11

JUSB2 (Right side 1)

2

3

1

4

USB PORT#

0

DESTINATION

6

5

7

DOCKING

Camera

JUSB3 (Right side 2)

PCH

Lane 7

Lane 8 None

10/100/1G LOM

12

13 LCD Touch

Bluetooth

+1.05V_M

+1.8V_RUN

+1.05V_RUN_VTT

+3.3V_RUN

+0.75V_DDR_VTT

+1.5V_RUN

+VCC_CORE

+1.05V_RUN

1/2vMINI CARD-3 PCIE

HDD

NA

ODD/ E3 Module Bay

SATA

SATA 0

DESTINATION

NA

SATA 1

SATA 2

SATA 3

SATA 4

SATA 5

ESATA

Dock

0

1

BIO

NAUSH

need to update Power Status and PM Table

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Dock DP port 2

DSC DP/HDMI Port

Port C

Connetion

Port D

Port E

Dock DP port 1

MB HDMI Conn

OFF

OFF

OFF

LOW

LOW

OFF

OFF

S0 (Full ON) / M0

SLP S3#

SLPS5#

HIGH

Signal

State

SLPS4#

HIGH HIGH

ALWAYSPLANE

ON

MPLANE

ON

SUSPLANE

RUNPLANE

CLOCKS

ON ON ON

S3 (Suspend to RAM) / M3 LOW HIGH HIGH ON ON ON OFF

S4 (Suspend to DISK) / M3 ON ON OFF

SLPA#

HIGH

HIGH

LOW HIGH HIGH

S5 (SOFT OFF) / M3 ON ON OFFLOW HIGHLOW

S3 (Suspend to RAM) / M-OFF

S5 (SOFT OFF) / M-OFF

LOW HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

S4 (Suspend to DISK) / M-OFF HIGH

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Power Rail

4 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Power Rail

4 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Power Rail

4 75Thursday, January 13, 2011

Compal Electronics, Inc.

BATTERY

+PWR_SRC

ADAPTER

FDC654P+BL_PWR_SRC

EN_INVPWR

SI3456BDVSI3456BDV

HD

DC

_E

N

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

+5V_MOD

MO

DC

_E

N

CHARGER

+3.3V_ALW

SN0608098

+15V_ALW

+5V_ALW

ALWON

SI3456

+3.3V_LAN+3.3V_SUS

RUN_ON

NTMS4920

RU

N_O

N

+3.3V_RUN

+5V_HDD

Q21

(Q30)(Q27)

(PU2)

(Q34) (Q55)

+5V_RUN

SI4164DY

(Q50)

+VCC_CORE

MAX17411

(PU9)

+1.5V_MEM +0.75V_DDR_VTT

DD

R_O

N

0.7

5V

_V

R_E

N

RT8209BGQW

(PU3)

+1.05V_RUN_VTT +1.05V_M

M_O

N

SU

S_O

N

S13456

(Q54)

1.0

5V

_0.8

V_P

WR

OK

RT9026GFP

(PU5)

SI3456

+3.3V_M

(Q58)

M_O

N

+3.3V_ALW_PCH

PC

H_A

LW

_O

N

SI3456

(Q49)

+1.5V_RUN

RUN_ON

NTGS4141N

(Q59)

AU

X_O

N

+1.8V_RUN

RU

N_O

N

(PU4)

+3.3V_WLAN

SI3456

(Q38)

AU

X_E

N_W

OW

L

SI4164

(Q63)

+1.05V_RUN

(PU7)

RU

N_O

N

+3.3V_M

Pop option

CP

U_V

TT

_O

N

ISL95870A+GPU_CORE

PGPU_PWR_EN

(PU15)

+1.5V_CPU_VDDQ

AO4728

(QC3)

CPU1.5V_S3_GATE

TPS51311SN1003055

(PU6)

SN1003055

Pop option

+1.0V_LAN

+0.8V_VCCSA

+VCC_SAISL95870AH

1.05V_VTTPWRGD

(PU13)

MAX17411

(PU9)+VCC_GFXCORE

1.05V_0.8V_PWROK

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

SMBUS TOPOLOGY

5 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

SMBUS TOPOLOGY

5 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

SMBUS TOPOLOGY

5 75Thursday, January 13, 2011

Compal Electronics, Inc.

MEC 5055

MEM_SMBDATA

MEM_SMBCLK

KBC

C9

H14

+3.3V_ALW_PCH

2.2K

2.2K

200 DIMMA

SMBUS Address [A4]

202

DIMMB

SMBUS Address [A0]

200

202

C8

G12

+3.3V_LAN

2.2K

2.2K

LAN_SMBCLK

LAN_SMBDATA

+3.3V_ALW

129

127

SMBUS Address 2.2K

DOCK_SMB_CLK

DOCK_SMB_DAT DOCKING

2.2K

B4

A3

1A

1A

A4

B5

2.2K

2.2K

LCD_SMBCLK

LCD_SMDATA

1B

1B

1C

1C

B59

A56

+3.3V_ALW2.2K

2.2K

100 ohm

100 ohmBATTERYCONN

7

6 SMBUS Address [0x16]PBAT_SMBCLK

PBAT_SMBDAT

3A

1E

1E

2B

2B

B501G

1G A47

2A

2A

B7

A7

+3.3V_ALW2.2K

2.2K

2D

2D

30

29BAY_SMBDAT

BAY_SMBCLK

A49

B52

CARD_SMBCLK

CARD_SMBDAT

+3.3V_SUS2.2K

2.2K

SMBUS Address [C8]LOM

CHARGER_SMBCLK

CHARGER_SMBDAT Charger SMBUS Address [0x12]

SML1_SMBDATA

PCH

SML1_SMBCLK

E14M16

A50

B53

B49

B48

3A

B6A5

+3.3V_ALW_PCH2.2K

2.2K

USH

+3.3V_ALW

USH_SMBCLK

USH_SMBDAT

+3.3V_ALW2.2K

2.2K

53

51SMBUS Address [TBD]XDP1

SMBUS Address [TBD]XDP2

53

51

8

9

GPU_SMBCLK

GPU_SMBDAT GPU SMBUS Address [0xXX]

+3.3V_RUN2.2K

2.2K

M9

L9 SMBUS Address [0xa4]

10

9

31

28

G SensorSMBUS Address [0x3B]

2N7002

2N7002

+3.3V_RUN2.2K

2.2K

14

13

2.2K

2.2K

Express card

7

8 SMBUS Address [TBD]

APR_EC: 0x48 SPR_EC: 0x70 MSLICE_EC: 0x72 USB: 0x59 AUDIO: 0x34 SLICE_BATTERY: 0x17 SLICE_CHARGER: 0x13

SMBUS Address [0x9a]

E3 Module BaySMBUS Address [0xd2]

@

@

+3.3V_ALW

WWANSMBUS Address [TBD]32

30

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DMI_CRX_PTX_P1DMI_CRX_PTX_P2

DMI_CTX_PRX_N0

DMI_CRX_PTX_N2

DMI_CTX_PRX_P2DMI_CTX_PRX_P1

DMI_CRX_PTX_N0

DMI_CRX_PTX_P0

DMI_CRX_PTX_N3

DMI_CTX_PRX_N3

DMI_CRX_PTX_P3

DMI_CTX_PRX_P3

DMI_CTX_PRX_P0

DMI_CTX_PRX_N1

DMI_CRX_PTX_N1

DMI_CTX_PRX_N2

EDP_COMP

PEG_COMP

PEG_CTX_GRX_C_P0

PEG_CTX_GRX_C_P1

PEG_CTX_GRX_P0

PEG_CTX_GRX_C_P3

PEG_CTX_GRX_C_P2

PEG_CTX_GRX_C_N3

PEG_CTX_GRX_C_N0 PEG_CTX_GRX_N0

PEG_CTX_GRX_C_N1

PEG_CTX_GRX_C_N2

PEG_CTX_GRX_C_P5

PEG_CTX_GRX_C_P6

PEG_CTX_GRX_C_P4PEG_CTX_GRX_C_N4

PEG_CTX_GRX_C_N6

PEG_CTX_GRX_C_N5

PEG_CTX_GRX_C_P7

PEG_CTX_GRX_C_P8

PEG_CTX_GRX_C_P9

PEG_CTX_GRX_C_N8

PEG_CTX_GRX_C_N7

PEG_CTX_GRX_C_P10

PEG_CTX_GRX_C_P11PEG_CTX_GRX_C_N11

PEG_CTX_GRX_C_N9

PEG_CTX_GRX_C_N10

PEG_CTX_GRX_C_P12PEG_CTX_GRX_C_N12

PEG_CTX_GRX_C_N13PEG_CTX_GRX_C_P13

PEG_CTX_GRX_C_P14PEG_CTX_GRX_C_N14

PEG_CTX_GRX_C_P15PEG_CTX_GRX_C_N15

PEG_CTX_GRX_P1PEG_CTX_GRX_N1

PEG_CTX_GRX_N2PEG_CTX_GRX_P2

PEG_CTX_GRX_P3

PEG_CTX_GRX_P4

PEG_CTX_GRX_N3

PEG_CTX_GRX_N4

PEG_CTX_GRX_P5

PEG_CTX_GRX_P6

PEG_CTX_GRX_P7

PEG_CTX_GRX_N5

PEG_CTX_GRX_N7

PEG_CTX_GRX_N6

PEG_CTX_GRX_P8

PEG_CTX_GRX_P9

PEG_CTX_GRX_P10

PEG_CTX_GRX_N8

PEG_CTX_GRX_N9

PEG_CTX_GRX_P11

PEG_CTX_GRX_N12PEG_CTX_GRX_P12

PEG_CTX_GRX_N11

PEG_CTX_GRX_N10

PEG_CTX_GRX_N13PEG_CTX_GRX_P13

PEG_CTX_GRX_P14

PEG_CTX_GRX_P15

PEG_CTX_GRX_N14

PEG_CTX_GRX_N15

PEG_CRX_GTX_N10

PEG_CRX_GTX_N4

PEG_CRX_GTX_N13

PEG_CRX_GTX_N7PEG_CRX_GTX_N6

PEG_CRX_GTX_N2PEG_CRX_GTX_N1

PEG_CRX_GTX_N15

PEG_CRX_GTX_N5

PEG_CRX_GTX_N9

PEG_CRX_GTX_N14

PEG_CRX_GTX_N8

PEG_CRX_GTX_N12

PEG_CRX_GTX_N3

PEG_CRX_GTX_N0

PEG_CRX_GTX_N11

PEG_CRX_GTX_P13

PEG_CRX_GTX_P0

PEG_CRX_GTX_P5PEG_CRX_GTX_P6

PEG_CRX_GTX_P2

PEG_CRX_GTX_P8

PEG_CRX_GTX_P4PEG_CRX_GTX_P3

PEG_CRX_GTX_P7

PEG_CRX_GTX_P9

PEG_CRX_GTX_P15PEG_CRX_GTX_P14

PEG_CRX_GTX_P10PEG_CRX_GTX_P11PEG_CRX_GTX_P12

PEG_CRX_GTX_P1

PEG_CTX_GRX_C_N14

PEG_CTX_GRX_C_N7

PEG_CTX_GRX_C_N0

PEG_CTX_GRX_C_N3

PEG_CTX_GRX_C_N1

PEG_CTX_GRX_C_N4

PEG_CTX_GRX_C_N8

PEG_CTX_GRX_C_N5

PEG_CTX_GRX_C_N2

PEG_CTX_GRX_C_N6

PEG_CTX_GRX_C_N9

PEG_CTX_GRX_C_N12

PEG_CTX_GRX_C_P1PEG_CTX_GRX_C_P2

PEG_CTX_GRX_C_N15

PEG_CTX_GRX_C_N10

PEG_CTX_GRX_C_P0

PEG_CTX_GRX_C_N11

PEG_CTX_GRX_C_N13

PEG_CTX_GRX_C_P3

PEG_CTX_GRX_C_P8

PEG_CTX_GRX_C_P11

PEG_CTX_GRX_C_P14

PEG_CTX_GRX_C_P5

PEG_CTX_GRX_C_P10

PEG_CTX_GRX_C_P4

PEG_CTX_GRX_C_P12

PEG_CTX_GRX_C_P15

PEG_CTX_GRX_C_P6PEG_CTX_GRX_C_P7

PEG_CTX_GRX_C_P9

PEG_CTX_GRX_C_P13

PEG_CTX_GRX_P[0..15]

PEG_CTX_GRX_N[0..15]

PEG_COMP

EDP_COMP

FDI_CTX_PRX_N1FDI_CTX_PRX_N2FDI_CTX_PRX_N3FDI_CTX_PRX_N4

FDI_CTX_PRX_N6FDI_CTX_PRX_N5

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0FDI_CTX_PRX_P1FDI_CTX_PRX_P2FDI_CTX_PRX_P3

FDI_CTX_PRX_P5FDI_CTX_PRX_P4

FDI_CTX_PRX_P6FDI_CTX_PRX_P7

FDI_FSYNC0FDI_FSYNC1

FDI_LSYNC0

FDI_INT

FDI_LSYNC1

FDI_CTX_PRX_N0

+1.05V_RUN_VTT+1.05V_RUN_VTT

DMI_CRX_PTX_P016

DMI_CRX_PTX_N316

DMI_CRX_PTX_P116

DMI_CRX_PTX_N116

DMI_CRX_PTX_P316

DMI_CRX_PTX_N216

DMI_CRX_PTX_P216

DMI_CRX_PTX_N016

DMI_CTX_PRX_N016DMI_CTX_PRX_N116DMI_CTX_PRX_N216DMI_CTX_PRX_N316

DMI_CTX_PRX_P016DMI_CTX_PRX_P116DMI_CTX_PRX_P216DMI_CTX_PRX_P316

PEG_CRX_GTX_N[0..15] 46

PEG_CRX_GTX_P[0..15] 46

PEG_CTX_GRX_N[0..15] 46

PEG_CTX_GRX_P[0..15] 46

FDI_CTX_PRX_N116FDI_CTX_PRX_N016

FDI_CTX_PRX_N416FDI_CTX_PRX_N316FDI_CTX_PRX_N216

FDI_CTX_PRX_N716FDI_CTX_PRX_N616FDI_CTX_PRX_N516

FDI_CTX_PRX_P216FDI_CTX_PRX_P116FDI_CTX_PRX_P016

FDI_CTX_PRX_P516FDI_CTX_PRX_P416FDI_CTX_PRX_P316

FDI_FSYNC016

FDI_LSYNC016

FDI_CTX_PRX_P716FDI_CTX_PRX_P616

FDI_LSYNC116

FDI_FSYNC116

FDI_INT16

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (1/6)

6 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (1/6)

6 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (1/6)

6 75Thursday, January 13, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

eDP_COMPIO and ICOMPO signals should be shorted near

balls and routed with typical impedance

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

XDP_TMS

XDP_TDO_R

SM_RCOMP0

XDP_DBRESET#

XDP_TRST#

XDP_TDI_R

XDP_TCLK

XDP_PRDY#

SM_RCOMP2

XDP_PREQ#

SM_RCOMP1

XDP_DBRESET#_R

CLK_XDPCLK_XDP#

XDP_OBS4XDP_OBS5

XDP_OBS6XDP_OBS7

CFD_PWRBTN#_XDP

CFG1

CFG2

CFG0

CFG3

CFG4CFG5

CFG6CFG7

XDP_TMS

XDP_PREQ#XDP_PRDY#

XDP_DBRESET#

XDP_TDOXDP_TRST#XDP_TDI

XDP_TCLK

H_CPUPWRGD

XDP_OBS0XDP_OBS1

XDP_OBS2XDP_OBS3

CFG0

H_CPUPWRGD_XDP

XDP_RST#_RXDP_HOOK2

DDR_XDP_WAN_SMBDAT_R1DDR_XDP_WAN_SMBCLK_R1

XDP_OBS2XDP_OBS3XDP_OBS3_R

XDP_OBS5_R

XDP_OBS2_RXDP_OBS1_RXDP_OBS0_R

XDP_OBS4_R XDP_OBS4

XDP_OBS7

XDP_OBS5XDP_OBS6_RXDP_OBS7_R

XDP_OBS6

XDP_OBS0XDP_OBS1

DDR_HVREF_RST

VCCPWRGOOD_0_R

H_PM_SYNC

H_CATERR#

H_PROCHOT#_R

H_THERMTRIP#_R

PM_DRAM_PWRGD_CPU

VCCPWRGOOD_0_R

H_CATERR#

H_PROCHOT#

H_THERMTRIP#

CPU_DMICPU_DMI#

DDR3_DRAMRST#_CPU

XDP_DBRESET#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDO

XDP_TDI_R

XDP_PREQ#

SYS_PWROK_XDP

SYS_PWROK_XDP

CLK_XDP

CLK_XDP#

SM_RCOMP0

SM_RCOMP2SM_RCOMP1

XDP_TDIXDP_TDI_R

XDP_TDO_R XDP_TDO

PCH_PLTRST#_R

PCH_PLTRST#_BUF PCH_PLTRST#_R

CFG11CFG10

CFG9CFG8

CFG16CFG17

XDP_RST#_R

CPU_DPLLCPU_DPLL#

RUNPWROK_AND PM_DRAM_PWRGD_CPU

+1.05V_RUN_VTT

+1.05V_RUN_VTT +1.05V_RUN_VTT

+1.05V_RUN_VTT

+1.05V_RUN_VTT

+1.05V_RUN_VTT

+3.3V_RUN

+3.3V_ALW_PCH

+3.3V_RUN

+3.3V_ALW_PCH

+1.5V_CPU_VDDQ

+3.3V_ALW_PCH

XDP_DBRESET# 14,16

SIO_PWRBTN#_R14,16

CFG0 9CFG1 9

CFG2 9CFG3 9

CFG4 9CFG5 9

CFG6 9CFG7 9

DDR3_DRAMRST# 12

H_THERMTRIP#22

H_CPUPWRGD18

H_PM_SYNC16

CPU_DETECT#41

H_PROCHOT#42,58,60

CLK_CPU_DMI 15

SYS_PWROK16,41

H_PECI18

CLK_CPU_ITP 15

CLK_CPU_ITP# 15

CLK_XDP_ITP9

CLK_XDP_ITP#9

PCH_PLTRST#14,17

CFG119CFG109

CFG9 9CFG8 9

CFG16 9CFG17 9

DDR_HVREF_RST_GATE42

DDR_HVREF_RST_PCH15

PLTRST_XDP# 17CLK_CPU_DMI# 15

CLK_CPU_DPLL 15CLK_CPU_DPLL# 15

RUN_ON_CPU1.5VS3#11,44

RUNPWROK41,42

PM_DRAM_PWRGD16

DDR_XDP_WAN_SMBDAT12,13,14,15,28,36DDR_XDP_WAN_SMBCLK12,13,14,15,28,36

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (2/6)

7 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (2/6)

7 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (2/6)

7 75Thursday, January 13, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Place near JXDP1

Keep R1132, R1133, R1136-R119 for slew rate control.

For ESD concern, please put near CPU

Avoid stub in the PWRGD path

while placing resistors RC25 & RC130

place RC129 near CPU

PU/PD for JTAG signals

Buffered reset to CPU

Close to JCBU1

Max 500mils

Open drain buffer

SM_RCOMP2 --> 15mil

SM_RCOMP1/0 --> 20mil

The resistor for HOOK2 should beplaced

such that the stub is very small on CFG0 net

Follow DG Rev0.71 SM_DRAMPWROK topology

CC1560.1U_0402_16V4Z~D

CC1560.1U_0402_16V4Z~D

1 2

G

DS

QC2BSS138W-7-F_SOT323-3~D

G

DS

QC2BSS138W-7-F_SOT323-3~D2

13

RC39 0_0402_5%~D@RC39 0_0402_5%~D@1 2

RH107 0_0402_5%~D@

RH107 0_0402_5%~D@ 1 2

RC30 0_0402_5%~D@RC30 0_0402_5%~D@1 2

RC46 0_0402_5%~D@RC46 0_0402_5%~D@1 2

RC13010K_0402_5%~DRC13010K_0402_5%~D

12

RC16 0_0402_5%~D@RC16 0_0402_5%~D@ 1 2

RC

43

25

.5_

04

02

_1

%~

DR

C4

32

5.5

_0

40

2_

1%

~D

12

RC

45

20

0_

04

02

_1

%~

DR

C4

52

00

_0

40

2_

1%

~D

12

RC28 130_0402_5%~DRC28 130_0402_5%~D1 2

RC7 1K_0402_5%~DRC7 1K_0402_5%~D1 2

RC1241K_0402_5%~D

@RC1241K_0402_5%~D

@

12

RC126 56_0402_5%~D@RC126 56_0402_5%~D@1 2

RC48 0_0402_5%~D@RC48 0_0402_5%~D@1 2

UC1

SN74LVC1G07DCKR_SC70-5~D

UC1

SN74LVC1G07DCKR_SC70-5~D

NC1

A2

G3

Y4

P5

RC128 49.9_0402_1%~D@RC128 49.9_0402_1%~D@1 2

RC18 200_0402_5%~DRC18 200_0402_5%~D1 2

G

D

S

QC1SSM3K7002FU_SC70-3~DG

D

S

QC1SSM3K7002FU_SC70-3~D

2

13

RC6 0_0402_5%~D@ RC6 0_0402_5%~D@1 2

CC

65

0.1

U_

04

02

_1

6V

4Z

~D

CC

65

0.1

U_

04

02

_1

6V

4Z

~D

1

2

RC44 62_0402_5%~DRC44 62_0402_5%~D1 2

CC1770.047U_0402_16V4Z~DCC1770.047U_0402_16V4Z~D

1

2

RC34 0_0402_5%~D@RC34 0_0402_5%~D@1 2

JXDP1

SAMTE_BSH-030-01-L-D-A

@JXDP1

SAMTE_BSH-030-01-L-D-A

@

GND01

OBSFN_A03

OBSFN_A15

GND27

OBSDATA_A09

OBSDATA_A111

GND413

OBSDATA_A215

OBSDATA_A317

GND619

OBSFN_B021

OBSFN_B123

GND825

OBSDATA_B027

OBSDATA_B129

GND1031

OBSDATA_B233

OBSDATA_B335

GND1237

PWRGOOD/HOOK039

HOOK141

VCC_OBS_AB43

HOOK245

HOOK347

GND1449

SDA51

SCL53

TCK155

TCK057

GND1659

GND12

OBSFN_C04

OBSFN_C16

GND38

OBSDATA_C010

OBSDATA_C112

GND514

OBSDATA_C216

OBSDATA_C318

GND720

OBSFN_D022

OBSFN_D124

GND926

OBSDATA_D028

OBSDATA_D130

GND1132

OBSDATA_D234

OBSDATA_D336

GND1338

ITPCLK/HOOK440

ITPCLK#/HOOK542

VCC_OBS_CD44

RESET#/HOOK646

DBR#/HOOK748

GND1550

TD052

TRST#54

TDI56

TMS58

GND1760

RC29 51_0402_1%~DRC29 51_0402_1%~D12

RC27 51_0402_1%~DRC27 51_0402_1%~D12

RC127 0_0402_5%~DRC127 0_0402_5%~D1 2

RC4051_0402_1%~D

RC4051_0402_1%~D

12

RC12200_0402_5%~DRC12200_0402_5%~D

12

RC19 1K_0402_5%~DRC19 1K_0402_5%~D12

RC15 0_0402_5%~D@RC15 0_0402_5%~D@ 1 2

RC25 0_0402_5%~D@RC25 0_0402_5%~D@1 2

RC6439_0402_5%~D

RC6439_0402_5%~D

12

RC38 0_0402_5%~D@RC38 0_0402_5%~D@1 2

RC

42

14

0_

04

02

_1

%~

DR

C4

21

40

_0

40

2_

1%

~D

12

RC57 56_0402_5%~DRC57 56_0402_5%~D1 2

RC35 51_0402_1%~DRC35 51_0402_1%~D12

RC5 1K_0402_5%~DRC5 1K_0402_5%~D1 2

RC

47

5_

04

02

_1

%~

DR

C4

75

_0

40

2_

1%

~D

12

RC10 43_0402_5%~DRC10 43_0402_5%~D1 2

CC

66

0.1

U_

04

02

_1

6V

4Z

~D

CC

66

0.1

U_

04

02

_1

6V

4Z

~D

1

2

RC4151_0402_1%~D

RC4151_0402_1%~D

12

RC37 0_0402_5%~D@RC37 0_0402_5%~D@1 2

RC504.99K_0402_1%~D

RC504.99K_0402_1%~D

12

RC8 1K_0402_5%~DRC8 1K_0402_5%~D12

RH106 0_0402_5%~D@RH106 0_0402_5%~D@1 2

RC129 0_0402_5%~D@RC129 0_0402_5%~D@1 2

RC36 0_0402_5%~D@RC36 0_0402_5%~D@1 2

RC17 0_0402_5%~D@RC17 0_0402_5%~D@ 1 2

RH109 0_0402_5%~D@RH109 0_0402_5%~D@1 2

RC31 0_0402_5%~D@RC31 0_0402_5%~D@1 2

RH108 0_0402_5%~D@RH108 0_0402_5%~D@1 2

RC24 0_0402_5%~D@ RC24 0_0402_5%~D@1 2

RC47 0_0402_5%~D@RC47 0_0402_5%~D@1 2

UC2

74AHC1G09GW_TSSOP5~D

UC2

74AHC1G09GW_TSSOP5~D

B1

A2

G3

O4

P5

RC33 0_0402_5%~D@RC33 0_0402_5%~D@1 2

CLOCKS

MISC

THERMAL

PWR MANAGEMENT

DDR3

MISC

JTAG & BPM

JCPU1B

Sandy Bridge_rPGA_Rev1p0

CLOCKS

MISC

THERMAL

PWR MANAGEMENT

DDR3

MISC

JTAG & BPM

JCPU1B

Sandy Bridge_rPGA_Rev1p0

SM_RCOMP[1]A5

SM_RCOMP[2]A4

SM_DRAMRST#R8

SM_RCOMP[0]AK1

BCLK#A27

BCLKA28

DPLL_REF_CLK#A15

DPLL_REF_CLKA16

CATERR#AL33

PECIAN33

PROCHOT#AL32

THERMTRIP#AN32

SM_DRAMPWROKV8

RESET#AR33

PRDY#AP29

PREQ#AP27

TCKAR26

TMSAR27

TRST#AP30

TDIAR28

TDOAP26

DBR#AL35

BPM#[0]AT28

BPM#[1]AR29

BPM#[2]AR30

BPM#[3]AT30

BPM#[4]AP32

BPM#[5]AR31

BPM#[6]AT31

BPM#[7]AR32

PM_SYNCAM34

SKTOCC#AN34

PROC_SELECT#C26

UNCOREPWRGOODAP33

RC32 51_0402_1%~D@RC32 51_0402_1%~D@ 12

RC125 0_0402_5%~DRC125 0_0402_5%~D1 2

CC

14

00

.1U

_0

40

2_

16

V4

Z~

DC

C1

40

0.1

U_

04

02

_1

6V

4Z

~D

1

2

RC13 0_0402_5%~D@RC13 0_0402_5%~D@ 1 2

RC110_0402_5%~D

@RC110_0402_5%~D

@

12

RC9 0_0402_5%~D@RC9 0_0402_5%~D@1 2

RC23 0_0402_5%~D@ RC23 0_0402_5%~D@1 2

RC26 0_0402_5%~D@ RC26 0_0402_5%~D@12

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_A_D59

DDR_A_D31

DDR_A_D9

DDR_A_BS1

DDR_A_D50

DDR_A_D42

DDR_A_D29

DDR_A_D51

DDR_A_D46

DDR_A_D36

DDR_A_D18

DDR_A_D4

DDR_A_D58

DDR_A_D55

DDR_A_D14

DDR_A_D24

DDR_A_D8

DDR_A_D63

DDR_A_D49

DDR_A_D41

DDR_A_D34

DDR_A_D28

DDR_A_D25

DDR_A_D35

DDR_A_D17

DDR_A_D13

DDR_A_D3

DDR_A_RAS#

DDR_A_D57

DDR_A_D54

DDR_A_D22DDR_A_D21

DDR_A_D6

DDR_A_D23

DDR_A_D7

DDR_A_BS2

DDR_A_D62

DDR_A_D48

DDR_A_D40

DDR_A_D33

DDR_A_D27

DDR_A_WE#

DDR_A_D44

DDR_A_D16

DDR_A_D12

DDR_A_D2

DDR_A_CAS#

DDR_A_D56

DDR_A_D53

DDR_A_D45

DDR_A_D38

DDR_A_D20

DDR_A_D60

DDR_A_D5

DDR_A_D61

DDR_A_D47

DDR_A_D39

DDR_A_D32

DDR_A_D26

DDR_A_D10

DDR_A_D0

DDR_A_BS0

DDR_A_D43

DDR_A_D15

DDR_A_D11

DDR_A_D1

DDR_A_D52

DDR_A_D37

DDR_A_D30

DDR_A_D19

DDR_B_D29

DDR_B_RAS#

DDR_B_D59

DDR_B_D50DDR_B_D49

DDR_B_D13

DDR_B_D11

DDR_B_D19

DDR_B_D14

DDR_B_D3

DDR_B_D55

DDR_B_D47

DDR_B_WE#

DDR_B_BS2

DDR_B_D52

DDR_B_D44

DDR_B_D41

DDR_B_D8

DDR_B_D5

DDR_B_CAS#

DDR_B_D56

DDR_B_D48

DDR_B_D38

DDR_B_D35

DDR_B_D26DDR_B_D25

DDR_B_D4

DDR_B_D63

DDR_B_D34

DDR_B_D32

DDR_B_D10

DDR_B_BS1

DDR_B_D17

DDR_B_D51

DDR_B_D40

DDR_B_D36

DDR_B_D31

DDR_B_D21DDR_B_D20

DDR_B_D15

DDR_B_D7

DDR_B_D62

DDR_B_D46

DDR_B_D42

DDR_B_D18

DDR_B_D12

DDR_B_D1

DDR_B_D53

DDR_B_D37

DDR_B_D22

DDR_B_D57

DDR_B_D27

DDR_B_D54

DDR_B_D45

DDR_B_D39

DDR_B_D30

DDR_B_D9

DDR_B_D60

DDR_B_D58

DDR_B_D33

DDR_B_D0

DDR_B_D61

DDR_B_D43

DDR_B_D28

DDR_B_D23DDR_B_D24

DDR_B_D16

DDR_B_D6

DDR_B_D2

DDR_B_BS0

M_CLK_DDR#0

M_CLK_DDR#1

DDR_CKE0_DIMMA

DDR_A_DQS7

DDR_A_DQS1DDR_A_DQS2

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS3DDR_A_DQS4

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS6

DDR_A_DQS#2DDR_A_DQS#1DDR_A_DQS#0

DDR_A_DQS#3DDR_A_DQS#4

DDR_A_DQS#6

DDR_A_MA0DDR_A_MA1

DDR_A_MA3

DDR_A_MA7DDR_A_MA8

DDR_A_MA13

DDR_A_MA2

DDR_A_MA14

DDR_A_MA5

DDR_A_MA10

DDR_A_MA4

DDR_A_MA11

DDR_A_MA9

DDR_A_MA6

DDR_A_MA12

M_CLK_DDR1

M_CLK_DDR0

DDR_A_MA15

DDR_CS1_DIMMA#DDR_CS0_DIMMA#

DDR_CKE1_DIMMA

M_ODT1M_ODT0

M_CLK_DDR3

M_CLK_DDR#2

M_CLK_DDR#3

DDR_B_MA10DDR_B_MA9

DDR_B_MA14

DDR_B_MA5

DDR_B_MA13

DDR_B_MA11

DDR_B_MA7

DDR_B_MA2

DDR_B_MA0

DDR_B_MA6

DDR_B_MA1

DDR_B_MA12

DDR_B_MA4

DDR_B_MA8

DDR_B_MA3

DDR_B_DQS3DDR_B_DQS2

DDR_B_DQS7

DDR_B_DQS4

DDR_B_DQS1

DDR_B_DQS5DDR_B_DQS6

DDR_B_DQS0

DDR_B_DQS#3

DDR_B_DQS#6

DDR_B_DQS#1

M_CLK_DDR2

DDR_B_DQS#2

DDR_B_DQS#0

DDR_B_DQS#5

DDR_B_DQS#7

DDR_B_DQS#4

M_ODT2

DDR_CKE2_DIMMB

DDR_B_MA15

DDR_CKE3_DIMMB

M_ODT3

DDR_CS2_DIMMB#DDR_CS3_DIMMB#

DDR_A_D[0..63]12

DDR_A_BS012DDR_A_BS112DDR_A_BS212

DDR_A_WE#12

DDR_A_CAS#12DDR_A_RAS#12

DDR_B_D[0..63]13

DDR_B_BS213DDR_B_BS113

DDR_B_WE#13

DDR_B_CAS#13DDR_B_RAS#13

DDR_B_BS013

DDR_A_DQS[0..7] 12

DDR_A_DQS#[0..7] 12

DDR_A_MA[0..15] 12

DDR_CKE1_DIMMA 12

DDR_CKE0_DIMMA 12

DDR_CS0_DIMMA# 12

M_ODT0 12

DDR_CS1_DIMMA# 12

M_ODT1 12

M_CLK_DDR1 12

M_CLK_DDR0 12

M_CLK_DDR#1 12

M_CLK_DDR#0 12

DDR_B_MA[0..15] 13

DDR_B_DQS#[0..7] 13

DDR_B_DQS[0..7] 13

DDR_CS3_DIMMB# 13DDR_CS2_DIMMB# 13

M_ODT3 13

DDR_CKE3_DIMMB 13

DDR_CKE2_DIMMB 13

M_ODT2 13

M_CLK_DDR#2 13M_CLK_DDR2 13

M_CLK_DDR#3 13M_CLK_DDR3 13

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (3/6)

8 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (3/6)

8 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (3/6)

8 75Thursday, January 13, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

DDR SYSTEM MEMORY B

JCPU1D

Sandy Bridge_rPGA_Rev1p0

DDR SYSTEM MEMORY B

JCPU1D

Sandy Bridge_rPGA_Rev1p0

SB_BS[0]AA9

SB_BS[1]AA7

SB_BS[2]R6

SB_CAS#AA10

SB_RAS#AB8

SB_WE#AB9

SB_CLK[0]AE2

SB_CLK[1]AE1

SB_CLK#[0]AD2

SB_CLK#[1]AD1

SB_CKE[0]R9

SB_CKE[1]R10

SB_ODT[0]AE4

SB_ODT[1]AD4

SB_DQS[4]AN6

SB_DQS#[4]AN5

SB_DQS[5]AP8

SB_DQS#[5]AP9

SB_DQS[6]AK11

SB_DQS#[6]AK12

SB_DQS[7]AP14

SB_DQS#[7]AP15

SB_DQS[0]C7

SB_DQS#[0]D7

SB_DQS[1]G3

SB_DQS#[1]F3

SB_DQS[2]J6

SB_DQS#[2]K6

SB_DQS[3]M3

SB_DQS#[3]N3

SB_MA[0]AA8

SB_MA[1]T7

SB_MA[2]R7

SB_MA[3]T6

SB_MA[4]T2

SB_MA[5]T4

SB_MA[6]T3

SB_MA[7]R2

SB_MA[8]T5

SB_MA[9]R3

SB_MA[10]AB7

SB_MA[11]R1

SB_MA[12]T1

SB_MA[13]AB10

SB_MA[14]R5

SB_MA[15]R4

SB_DQ[0]C9

SB_DQ[1]A7

SB_DQ[2]D10

SB_DQ[3]C8

SB_DQ[4]A9

SB_DQ[5]A8

SB_DQ[6]D9

SB_DQ[7]D8

SB_DQ[8]G4

SB_DQ[9]F4

SB_DQ[10]F1

SB_DQ[11]G1

SB_DQ[12]G5

SB_DQ[13]F5

SB_DQ[14]F2

SB_DQ[15]G2

SB_DQ[16]J7

SB_DQ[17]J8

SB_DQ[18]K10

SB_DQ[19]K9

SB_DQ[20]J9

SB_DQ[21]J10

SB_DQ[22]K8

SB_DQ[23]K7

SB_DQ[24]M5

SB_DQ[25]N4

SB_DQ[26]N2

SB_DQ[27]N1

SB_DQ[28]M4

SB_DQ[29]N5

SB_DQ[30]M2

SB_DQ[31]M1

SB_DQ[32]AM5

SB_DQ[33]AM6

SB_DQ[34]AR3

SB_DQ[35]AP3

SB_DQ[36]AN3

SB_DQ[37]AN2

SB_DQ[38]AN1

SB_DQ[39]AP2

SB_DQ[40]AP5

SB_DQ[41]AN9

SB_DQ[42]AT5

SB_DQ[43]AT6

SB_DQ[44]AP6

SB_DQ[45]AN8

SB_DQ[46]AR6

SB_DQ[47]AR5

SB_DQ[48]AR9

SB_DQ[49]AJ11

SB_DQ[50]AT8

SB_DQ[51]AT9

SB_DQ[52]AH11

SB_DQ[53]AR8

SB_DQ[54]AJ12

SB_DQ[55]AH12

SB_DQ[56]AT11

SB_DQ[57]AN14

SB_DQ[58]AR14

SB_DQ[59]AT14

SB_DQ[60]AT12

SB_DQ[61]AN15

SB_DQ[62]AR15

SB_DQ[63]AT15

RSVD_TP[11]AB2

RSVD_TP[12]AA2

RSVD_TP[13]T9

RSVD_TP[14]AA1

RSVD_TP[15]AB1

RSVD_TP[16]T10

SB_CS#[0]AD3

SB_CS#[1]AE3

RSVD_TP[17]AD6

RSVD_TP[18]AE6

RSVD_TP[19]AD5

RSVD_TP[20]AE5

DDR SYSTEM MEMORY A

JCPU1C

Sandy Bridge_rPGA_Rev1p0

DDR SYSTEM MEMORY A

JCPU1C

Sandy Bridge_rPGA_Rev1p0

SA_BS[0]AE10

SA_BS[1]AF10

SA_BS[2]V6

SA_CAS#AE8

SA_RAS#AD9

SA_WE#AF9

SA_CLK[0]AB6

SA_CLK[1]AA5

SA_CLK#[0]AA6

SA_CLK#[1]AB5

SA_CKE[0]V9

SA_CKE[1]V10

SA_CS#[0]AK3

SA_CS#[1]AL3

SA_ODT[0]AH3

SA_ODT[1]AG3

SA_DQS[0]D4

SA_DQS#[0]C4

SA_DQS[1]F6

SA_DQS#[1]G6

SA_DQS[2]K3

SA_DQS#[2]J3

SA_DQS[3]N6

SA_DQS#[3]M6

SA_DQS[4]AL5

SA_DQS#[4]AL6

SA_DQS[5]AM9

SA_DQS#[5]AM8

SA_DQS[6]AR11

SA_DQS#[6]AR12

SA_DQS[7]AM14

SA_DQS#[7]AM15

SA_MA[0]AD10

SA_MA[1]W1

SA_MA[2]W2

SA_MA[3]W7

SA_MA[4]V3

SA_MA[5]V2

SA_MA[6]W3

SA_MA[7]W6

SA_MA[8]V1

SA_MA[9]W5

SA_MA[10]AD8

SA_MA[11]V4

SA_MA[12]W4

SA_MA[13]AF8

SA_MA[14]V5

SA_MA[15]V7

SA_DQ[0]C5

SA_DQ[1]D5

SA_DQ[2]D3

SA_DQ[3]D2

SA_DQ[4]D6

SA_DQ[5]C6

SA_DQ[6]C2

SA_DQ[7]C3

SA_DQ[8]F10

SA_DQ[9]F8

SA_DQ[10]G10

SA_DQ[11]G9

SA_DQ[12]F9

SA_DQ[13]F7

SA_DQ[14]G8

SA_DQ[15]G7

SA_DQ[16]K4

SA_DQ[17]K5

SA_DQ[18]K1

SA_DQ[19]J1

SA_DQ[20]J5

SA_DQ[21]J4

SA_DQ[22]J2

SA_DQ[23]K2

SA_DQ[24]M8

SA_DQ[25]N10

SA_DQ[26]N8

SA_DQ[27]N7

SA_DQ[28]M10

SA_DQ[29]M9

SA_DQ[30]N9

SA_DQ[31]M7

SA_DQ[32]AG6

SA_DQ[33]AG5

SA_DQ[34]AK6

SA_DQ[35]AK5

SA_DQ[36]AH5

SA_DQ[37]AH6

SA_DQ[38]AJ5

SA_DQ[39]AJ6

SA_DQ[40]AJ8

SA_DQ[41]AK8

SA_DQ[42]AJ9

SA_DQ[43]AK9

SA_DQ[44]AH8

SA_DQ[45]AH9

SA_DQ[46]AL9

SA_DQ[47]AL8

SA_DQ[48]AP11

SA_DQ[49]AN11

SA_DQ[50]AL12

SA_DQ[51]AM12

SA_DQ[52]AM11

SA_DQ[53]AL11

SA_DQ[54]AP12

SA_DQ[55]AN12

SA_DQ[56]AJ14

SA_DQ[57]AH14

SA_DQ[58]AL15

SA_DQ[59]AK15

SA_DQ[60]AL14

SA_DQ[61]AK14

SA_DQ[62]AJ15

SA_DQ[63]AH15

RSVD_TP[1]AB4

RSVD_TP[2]AA4

RSVD_TP[4]AB3

RSVD_TP[5]AA3

RSVD_TP[3]W9

RSVD_TP[6]W10

RSVD_TP[7]AG1

RSVD_TP[8]AH1

RSVD_TP[9]AG2

RSVD_TP[10]AH2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

CFG10CFG11

CFG13CFG14CFG15CFG16CFG17

CFG12

CFG1CFG2

CFG0

CFG3CFG4CFG5CFG6CFG7CFG8CFG9

RSVD3RSVD4

RSVD1RSVD2

CFG4

CFG6

CFG5

CFG2

CFG7

RSVD4

RSVD2

RSVD1

RSVD3

+DIMM0_1_VREF_CPU+DIMM0_1_CA_CPU

+DIMM0_1_CA_CPU

+DIMM0_1_VREF_CPU

+VCC_CORE

+VCC_GFXCORE

+DIMM0_1_VREF_CPU+DIMM0_1_CA_CPU

CFG07CFG17CFG27CFG37CFG47CFG57CFG67CFG77CFG87CFG97CFG107CFG117

CLK_XDP_ITP 7CLK_XDP_ITP# 7

CFG177CFG167

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (4/6)

9 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (4/6)

9 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (4/6)

9 75Thursday, January 13, 2011

Compal Electronics, Inc.PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

DELL CONFIDENTIAL/PROPRIETARY

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

PCIE Port Bifurcation Straps

CFG[6:5]

11: (Default) x16 - Device 1 functions 1 and 2 disabled

CFG7

PEG DEFER TRAINING

0: PEG Wait for BIOS for training

1: (Default) PEG Train immediatelyfollowing xxRESETB de assertion

CFG4

Display Port Presence Strap

0 : Enabled; An external Display Port device isconnected to the Embedded Display Port

1 : Disabled; No Physical Display Portattached to Embedded Display Port

CFG Straps for Processor

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

0:Lane Reversed

1:(Default) Normal Operation; Lane #definition matches socket pin map definition

follow DG0.9 change to 1Kohm 5%

T37 PAD~D@T37 PAD~D@

RC120 49.9_0402_1%~D@RC120 49.9_0402_1%~D@1 2

RC561K_0402_5%~D

@RC561K_0402_5%~D

@

12

T45 PAD~D@T45 PAD~D@

RC541K_0402_5%~D

@RC541K_0402_5%~D

@

12

T12 PAD~D@T12 PAD~D@

T42 PAD~D@T42 PAD~D@

T4 PAD~D@T4 PAD~D@

T33 PAD~D@T33 PAD~D@T35 PAD~D@T35 PAD~D@

T39 PAD~D@T39 PAD~D@

T24 PAD~D@T24 PAD~D@

T38 PAD~D@T38 PAD~D@

T31 PAD~D@T31 PAD~D@

T21 PAD~D@T21 PAD~D@

T9 PAD~D@T9 PAD~D@T11 PAD~D@T11 PAD~D@

T16 PAD~D@T16 PAD~D@

T52 PAD~D@T52 PAD~D@

T17 PAD~D@T17 PAD~D@

T49 PAD~D@T49 PAD~D@

T40 PAD~D@T40 PAD~D@

T7 PAD~D@T7 PAD~D@

T53 PAD~D@T53 PAD~D@

T32 PAD~D@T32 PAD~D@

T46 PAD~D@T46 PAD~D@

T30 PAD~D@T30 PAD~D@T29 PAD~D@T29 PAD~D@

RC531K_0402_5%~D

@RC531K_0402_5%~D

@

12

T5 PAD~D@T5 PAD~D@

T20 PAD~D@T20 PAD~D@

T44 PAD~D@T44 PAD~D@

T48 PAD~D@T48 PAD~D@

RC97 1K_0402_5%~D@RC97 1K_0402_5%~D@1 2

T2 PAD~D@T2 PAD~D@

T27 PAD~D@T27 PAD~D@

T8 PAD~D@T8 PAD~D@

T18 PAD~D@T18 PAD~D@

T6 PAD~D@T6 PAD~D@

T51 PAD~D@T51 PAD~D@

T19 PAD~D@T19 PAD~D@

T1 PAD~D@T1 PAD~D@

T43 PAD~D@T43 PAD~D@

T34 PAD~D@T34 PAD~D@

T13 PAD~D@T13 PAD~D@

T47 PAD~D@T47 PAD~D@

T36 PAD~D@T36 PAD~D@

T23 PAD~D@T23 PAD~D@

T25 PAD~D@T25 PAD~D@

RC511K_0402_5%~D

@RC511K_0402_5%~D

@

12

T3 PAD~D@T3 PAD~D@

T28 PAD~D@T28 PAD~D@

T22 PAD~D@T22 PAD~D@RC123 49.9_0402_1%~D@RC123 49.9_0402_1%~D@

1 2

RESERVED

JCPU1E

Sandy Bridge_rPGA_Rev1p0

RESERVED

JCPU1E

Sandy Bridge_rPGA_Rev1p0

CFG[0]AK28

CFG[1]AK29

CFG[2]AL26

CFG[3]AL27

CFG[4]AK26

CFG[5]AL29

CFG[6]AL30

CFG[7]AM31

CFG[8]AM32

CFG[9]AM30

CFG[10]AM28

CFG[11]AM26

CFG[12]AN28

CFG[13]AN31

CFG[14]AN26

CFG[15]AM27

CFG[16]AK31

CFG[17]AN29

RSVD34AM33

RSVD35AJ27

RSVD38J16

RSVD42AT34

RSVD39H16

RSVD40G16

RSVD41AR35

RSVD43AT33

RSVD45AR34

RSVD56AT2

RSVD57AT1

RSVD58AR1

RSVD46B34

RSVD47A33

RSVD48A34

RSVD49B35

RSVD50C35

RSVD51AJ32

RSVD52AK32

RSVD30AE7

RSVD31AK2

RSVD28L7

RSVD29AG7

RSVD27J15

RSVD16C30

RSVD15D23

RSVD17A31

RSVD18B30

RSVD20D30

RSVD19B29

RSVD22A30

RSVD21B31

RSVD23C29

RSVD24J20

RSVD37T8

RSVD6B4

RSVD7D1

RSVD8F25

RSVD9F24

RSVD11D24

RSVD12G25

RSVD13G24

RSVD14E23

RSVD32W8

RSVD33AT26

RSVD25B18

RSVD44AP35

RSVD10F23

RSVD5AJ26

VAXG_VAL_SENSEAJ31

VSSAXG_VAL_SENSEAH31

VCC_VAL_SENSEAJ33

VSS_VAL_SENSEAH33

KEYB1

VCC_DIE_SENSEAH27

VCCIO_SELA19

RSVD54AN35

RSVD55AM35

RC521K_0402_5%~D

@RC521K_0402_5%~D

@

12

T14 PAD~D@T14 PAD~D@

RC122 49.9_0402_1%~D@RC122 49.9_0402_1%~D@1 2

T15 PAD~D@T15 PAD~D@

T10 PAD~D@T10 PAD~D@

T155 PAD~D@T155 PAD~D@

RC96 1K_0402_5%~D@RC96 1K_0402_5%~D@1 2

T26 PAD~D@T26 PAD~D@

T41 PAD~D@T41 PAD~D@

T50 PAD~D@T50 PAD~D@

RC121 49.9_0402_1%~D@RC121 49.9_0402_1%~D@1 2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

VCCSENSE_RVSSSENSE_R

VTT_SENSE_RVSSIO_SENSE_R

H_CPU_SVIDALRT#

VIDSOUT

H_CPU_SVIDALRT#VIDSCLK

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+VCC_CORE

+1.05V_RUN_VTT

+1.05V_RUN_VTT

+1.05V_RUN_VTT

VSSSENSE 58VCCSENSE 58

VTT_SENSE 57

VIDALERT_N 58

VIDSCLK 58VIDSOUT 58

VTT_GND 57

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (5/6)

10 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (5/6)

10 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

Sandy Bridge (5/6)

10 75Thursday, January 13, 2011

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

53A 8.5A

CPU Power Rail Table

1.5

0.65-0.9

VCC

VCCIO

VAXG

VCCPLL

VDDQ

VCCSA

Voltage Rail

0.65-1.3

1.05

1.8

53

8.5

26

3

12-16

6

0.0-1.1

VoltageS0 Iccmax

Current (A)

5A to Mem controller(+1.5V_CPU_VDDQ)

5-6A to 2 DIMMs/channel

2-5A to +1.5V_RUN & +0.75V_DDR_VTT

*

* Description

5

+1.5V_MEM 1.5

Iccmax current changed for PDDG Rev0.7

Note: Place the PU resistors close to CPU

R1555 close to CPU 300 - 1500mils

CAD Note: Place the PU

resistors close to CPU

R1558 close to CPU 300 - 1500mils

DELL CONFIDENTIAL/PROPRIETARY

Place RC66, RC70near CPU

SVID note: VIDALERT# trace

routing need to be routed between

VIDSCLK and VIDSOUT signals

+ CC133470U_D2_2V-M~D

@+ CC133470U_D2_2V-M~D

@

1

2 3

CC11822U_0805_6.3VAM~DCC11822U_0805_6.3VAM~D

1

2

CC

80

22

U_

08

05

_6

.3V

AM

~D

CC

80

22

U_

08

05

_6

.3V

AM

~D

1

2

CC12222U_0805_6.3VAM~DCC12222U_0805_6.3VAM~D

1

2

CC6810U_0805_4VAM~DCC6810U_0805_4VAM~D

1

2

CC11322U_0805_6.3VAM~DCC11322U_0805_6.3VAM~D

1

2

CC

81

22

U_

08

05

_6

.3V

AM

~D

CC

81

22

U_

08

05

_6

.3V

AM

~D

1

2

RC68 0_0402_5%~D@RC68 0_0402_5%~D@1 2

CC

85

22

U_

08

05

_6

.3V

AM

~D

CC

85

22

U_

08

05

_6

.3V

AM

~D

1

2

+ CC131470U_D2_2V-M~D

+ CC131470U_D2_2V-M~D

1

2 3

CC

86

22

U_

08

05

_6

.3V

AM

~D

CC

86

22

U_

08

05

_6

.3V

AM

~D

1

2

CC

84

22

U_

08

05

_6

.3V

AM

~D

CC

84

22

U_

08

05

_6

.3V

AM

~D

1

2

RC67 0_0402_5%~D@RC67 0_0402_5%~D@1 2

+

CC

10

83

30

U_

D2

_2

VM

_R

6M

~D

+

CC

10

83

30

U_

D2

_2

VM

_R

6M

~D

1

2

RC132 0_0402_5%~D@RC132 0_0402_5%~D@1 2

CC

78

22

U_

08

05

_6

.3V

AM

~D

CC

78

22

U_

08

05

_6

.3V

AM

~D

1

2

CC11222U_0805_6.3VAM~DCC11222U_0805_6.3VAM~D

1

2

CC8710U_0805_4VAM~DCC8710U_0805_4VAM~D

1

2

CC7310U_0805_4VAM~DCC7310U_0805_4VAM~D

1

2

CC7710U_0805_4VAM~DCC7710U_0805_4VAM~D

1

2

CC

91

22

U_

08

05

_6

.3V

AM

~D

@C

C9

12

2U

_0

80

5_

6.3

VA

M~

D@1

2

RC63130_0402_1%~DRC63130_0402_1%~D

12

+ CC134470U_D2_2V-M~D

+ CC134470U_D2_2V-M~D

1

2 3

CC11122U_0805_6.3VAM~DCC11122U_0805_6.3VAM~D

1

2

CC

70

22

U_

08

05

_6

.3V

AM

~D

CC

70

22

U_

08

05

_6

.3V

AM

~D

1

2

CC

83

22

U_

08

05

_6

.3V

AM

~D

CC

83

22

U_

08

05

_6

.3V

AM

~D

1

2

CC

92

22

U_

08

05

_6

.3V

AM

~D

@C

C9

22

2U

_0

80

5_

6.3

VA

M~

D@1

2

CC11022U_0805_6.3VAM~DCC11022U_0805_6.3VAM~D

1

2

CC11522U_0805_6.3VAM~DCC11522U_0805_6.3VAM~D

1

2

CC11622U_0805_6.3VAM~DCC11622U_0805_6.3VAM~D

1

2

CC11422U_0805_6.3VAM~DCC11422U_0805_6.3VAM~D

1

2

CC12422U_0805_6.3VAM~DCC12422U_0805_6.3VAM~D

1

2

CC8810U_0805_4VAM~DCC8810U_0805_4VAM~D

1

2

CC

93

22

U_

08

05

_6

.3V

AM

~D

@C

C9

32

2U

_0

80

5_

6.3

VA

M~

D@1

2

RC66

100_0402_1%~D

RC66

100_0402_1%~D

12

CC

90

22

U_

08

05

_6

.3V

AM

~D

@C

C9

02

2U

_0

80

5_

6.3

VA

M~

D@1

2

+ CC132470U_D2_2V-M~D

+ CC132470U_D2_2V-M~D

1

2 3

+

CC

10

73

30

U_

D2

_2

VM

_R

6M

~D

+

CC

10

73

30

U_

D2

_2

VM

_R

6M

~D

1

2

CC

79

22

U_

08

05

_6

.3V

AM

~D

CC

79

22

U_

08

05

_6

.3V

AM

~D

1

2

CC7510U_0805_4VAM~DCC7510U_0805_4VAM~D

1

2

CC

82

22

U_

08

05

_6

.3V

AM

~D

CC

82

22

U_

08

05

_6

.3V

AM

~D

1

2

RC6075_0402_1%~DRC6075_0402_1%~D

12

CC12522U_0805_6.3VAM~DCC12522U_0805_6.3VAM~D

1

2

CC7110U_0805_4VAM~DCC7110U_0805_4VAM~D

1

2

RC61 43_0402_5%~DRC61 43_0402_5%~D1 2

CC

69

22

U_

08

05

_6

.3V

AM

~D

CC

69

22

U_

08

05

_6

.3V

AM

~D

1

2

+

CC

10

93

30

U_

D2

_2

VM

_R

6M

~D

@+

CC

10

93

30

U_

D2

_2

VM

_R

6M

~D

@

1

2

CC

89

22

U_

08

05

_6

.3V

AM

~D

CC

89

22

U_

08

05

_6

.3V

AM

~D

1

2

CC12022U_0805_6.3VAM~DCC12022U_0805_6.3VAM~D

1

2

+ CC130470U_D2_2V-M~D

@+ CC130470U_D2_2V-M~D

@

1

2 3

CC11722U_0805_6.3VAM~DCC11722U_0805_6.3VAM~D

1

2

CC7210U_0805_4VAM~DCC7210U_0805_4VAM~D

1

2

CC7610U_0805_4VAM~DCC7610U_0805_4VAM~D

1

2

RC133 0_0402_5%~D@RC133 0_0402_5%~D@1 2

RC70

100_0402_1%~D

RC70

100_0402_1%~D

12

+ CC129470U_D2_2V-M~D

+ CC129470U_D2_2V-M~D

1

2 3

CC12122U_0805_6.3VAM~DCC12122U_0805_6.3VAM~D

1

2

CC12322U_0805_6.3VAM~DCC12322U_0805_6.3VAM~D

1

2

POWER

CORE SUPPLY

PEG AND DDR

SENSE LINES

SVID

JCPU1F

Sandy Bridge_rPGA_Rev1p0

POWER

CORE SUPPLY

PEG AND DDR

SENSE LINES

SVID

JCPU1F

Sandy Bridge_rPGA_Rev1p0

VCC_SENSEAJ35

VSS_SENSEAJ34

VIDALERT#AJ29

VIDSCLKAJ30

VIDSOUTAJ28

VSSIO_SENSEA10

VCC1AG35

VCC2AG34

VCC3AG33

VCC4AG32

VCC5AG31

VCC6AG30

VCC7AG29

VCC8AG28

VCC9AG27

VCC10AG26

VCC11AF35

VCC12AF34

VCC13AF33

VCC14AF32

VCC15AF31

VCC16AF30

VCC17AF29

VCC18AF28

VCC19AF27

VCC20AF26

VCC21AD35

VCC22AD34

VCC23AD33

VCC24AD32

VCC25AD31

VCC26AD30

VCC27AD29

VCC28AD28

VCC29AD27

VCC30AD26

VCC31AC35

VCC32AC34

VCC33AC33

VCC34AC32

VCC35AC31

VCC36AC30

VCC37AC29

VCC38AC28

VCC39AC27

VCC40AC26

VCC41AA35

VCC42AA34

VCC43AA33

VCC44AA32

VCC45AA31

VCC46AA30

VCC47AA29

VCC48AA28

VCC49AA27

VCC50AA26

VCC51Y35

VCC52Y34

VCC53Y33

VCC54Y32

VCC55Y31

VCC56Y30

VCC57Y29

VCC58Y28

VCC59Y27

VCC60Y26

VCC61V35

VCC62V34

VCC63V33

VCC64V32

VCC65V31

VCC66V30

VCC67V29

VCC68V28

VCC69V27

VCC70V26

VCC71U35

VCC72U34

VCC73U33

VCC74U32

VCC75U31

VCC76U30

VCC77U29

VCC78U28

VCC79U27

VCC80U26

VCC81R35

VCC82R34

VCC83R33

VCC84R32

VCC85R31

VCC86R30

VCC87R29

VCC88R28

VCC89R27

VCC90R26

VCC91P35

VCC92P34

VCC93P33

VCC94P32

VCC95P31

VCC96P30

VCC97P29

VCC98P28

VCC99P27

VCC100P26

VCCIO1AH13

VCCIO12J11

VCCIO18G12

VCCIO19F14

VCCIO20F13

VCCIO21F12

VCCIO22F11

VCCIO23E14

VCCIO24E12

VCCIO2AH10

VCCIO3AG10

VCCIO4AC10

VCCIO5Y10

VCCIO6U10

VCCIO7P10

VCCIO8L10

VCCIO9J14

VCCIO10J13

VCCIO11J12

VCCIO13H14

VCCIO14H12

VCCIO15H11

VCCIO16G14

VCCIO17G13

VCCIO25E11

VCCIO32C12

VCCIO33C11

VCCIO34B14

VCCIO35B12

VCCIO36A14

VCCIO37A13

VCCIO38A12

VCCIO39A11

VCCIO26D14

VCCIO27D13

VCCIO28D12

VCCIO29D11

VCCIO30C14

VCCIO31C13

VCCIO_SENSEB10

VCCIO40J23

CC11922U_0805_6.3VAM~DCC11922U_0805_6.3VAM~D

1

2

CC6710U_0805_4VAM~DCC6710U_0805_4VAM~D

1

2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

RUN_ON_CPU1.5VS3#

RUN_ON_CPU1.5VS3

RUN_ON_CPU1.5VS3

H_FC_C22

+1.5V_MEM +1.5V_CPU_VDDQ+15V_ALW+3.3V_ALW2

+1.5V_MEM

+V_DDR_REF

+VCC_GFXCORE

+1.8V_RUN

+VCC_SA

+1.5V_CPU_VDDQ

+V_SM_VREF_CNT

+V_SM_VREF_CNT

RUN_ON37,41,44,55,63

CPU1.5V_S3_GATE42 RUN_ON_CPU1.5VS3# 7,44

VCC_AXG_SENSE 58VSS_AXG_SENSE 58

VCCSA_VID_1 61

+GND_VCC_SA 61

+VCCSA_SENSE 61

Title

Size Document Number Rev

Date: Sheet of

LA-6592P1.0

Sandy Bridge (6/6)

11 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P1.0

Sandy Bridge (6/6)

11 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P1.0

Sandy Bridge (6/6)

11 75Thursday, January 13, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

+1.5V_CPU_VDDQ Source

+V_SM_VREF should

have 10 mil trace width

26A

5A

3A

6A

RC

83

10

K_

04

02

_5

%~

DR

C8

31

0K

_0

40

2_

5%

~D

12

CC

16

11

0U

_0

80

5_

4V

AM

~D

CC

16

11

0U

_0

80

5_

4V

AM

~D

1

2

CC

15

22

2U

_0

80

5_

6.3

VA

M~

DC

C1

52

22

U_

08

05

_6

.3V

AM

~D

1

2

RC134 0_0402_5%~D@RC134 0_0402_5%~D@1 2

CC

17

51

U_

04

02

_6

.3V

6K

~D

CC

17

51

U_

04

02

_6

.3V

6K

~D

1

2

CC179 0.1U_0402_10V7K~DCC179 0.1U_0402_10V7K~D12

CC

17

41

U_

04

02

_6

.3V

6K

~D

CC

17

41

U_

04

02

_6

.3V

6K

~D

1

2

+C

C1

67

33

0U

_D

2_

2V

M_

R6

M~

D

+C

C1

67

33

0U

_D

2_

2V

M_

R6

M~

D

1

2

CC

13

51

0U

_0

80

5_

6.3

V6

M~

DC

C1

35

10

U_

08

05

_6

.3V

6M

~D

1

2

CC

16

61

0U

_0

80

5_

4V

AM

~D

CC

16

61

0U

_0

80

5_

4V

AM

~D

1

2

PJP1

PAD-OPEN 4x4m

@PJP1

PAD-OPEN 4x4m

@

1 2

CC150 0.1U_0402_10V7K~DCC150 0.1U_0402_10V7K~D12

+

CC

17

63

30

U_

D2

_2

.5V

M_

R6

M~

D

+

CC

17

63

30

U_

D2

_2

.5V

M_

R6

M~

D

1

2

RC137 0_0402_5%~D@RC137 0_0402_5%~D@1 2

QC4BDMN66D0LDW-7_SOT363-6~DQC4BDMN66D0LDW-7_SOT363-6~D

3

5

4

CC

15

32

2U

_0

80

5_

6.3

VA

M~

DC

C1

53

22

U_

08

05

_6

.3V

AM

~D

1

2

CC

13

72

2U

_0

80

5_

6.3

VA

M~

DC

C1

37

22

U_

08

05

_6

.3V

AM

~D

1

2

CC

15

12

2U

_0

80

5_

6.3

VA

M~

DC

C1

51

22

U_

08

05

_6

.3V

AM

~D

1

2

RC77 0_0402_5%~D@RC77 0_0402_5%~D@1 2

POWER

GRAPHICS

DDR3 -1.5V RAILS

SENSE

LINES

1.8V RAIL

SA RAIL

VREF

MISC

JCPU1G

Sandy Bridge_rPGA_Rev1p0

POWER

GRAPHICS

DDR3 -1.5V RAILS

SENSE

LINES

1.8V RAIL

SA RAIL

VREF

MISC

JCPU1G

Sandy Bridge_rPGA_Rev1p0

SM_VREFAL1

VSSAXG_SENSEAK34

VAXG_SENSEAK35

VAXG1AT24

VAXG2AT23

VAXG3AT21

VAXG4AT20

VAXG5AT18

VAXG6AT17

VAXG7AR24

VAXG8AR23

VAXG9AR21

VAXG10AR20

VAXG11AR18

VAXG12AR17

VAXG13AP24

VAXG14AP23

VAXG15AP21

VAXG16AP20

VAXG17AP18

VAXG18AP17

VAXG19AN24

VAXG20AN23

VAXG21AN21

VAXG22AN20

VAXG23AN18

VAXG24AN17

VAXG25AM24

VAXG26AM23

VAXG27AM21

VAXG28AM20

VAXG29AM18

VAXG30AM17

VAXG31AL24

VAXG32AL23

VAXG33AL21

VAXG34AL20

VAXG35AL18

VAXG36AL17

VAXG37AK24

VAXG38AK23

VAXG39AK21

VAXG40AK20

VAXG41AK18

VAXG42AK17

VAXG43AJ24

VAXG44AJ23

VAXG45AJ21

VAXG46AJ20

VAXG47AJ18

VAXG48AJ17

VAXG49AH24

VAXG50AH23

VAXG51AH21

VAXG52AH20

VAXG53AH18

VAXG54AH17

VDDQ11U4

VDDQ12U1

VDDQ13P7

VDDQ14P4

VDDQ15P1

VDDQ1AF7

VDDQ2AF4

VDDQ3AF1

VDDQ4AC7

VDDQ5AC4

VDDQ6AC1

VDDQ7Y7

VDDQ8Y4

VDDQ9Y1

VDDQ10U7

VCCPLL1B6

VCCPLL2A6

VCCSA1M27

VCCSA2M26

VCCSA3L26

VCCSA4J26

VCCSA5J25

VCCSA6J24

VCCSA7H26

VCCSA8H25

VCCSA_SENSEH23

VCCSA_VID1C24

VCCPLL3A2

FC_C22C22

QC4ADMN66D0LDW-7_SOT363-6~DQC4ADMN66D0LDW-7_SOT363-6~D

61

2

QC3AO4728L_SO8~D

QC3AO4728L_SO8~D

4

78

65

123

RC74100K_0402_5%~DRC74100K_0402_5%~D

12

CC

14

62

2U

_0

80

5_

6.3

VA

M~

DC

C1

46

22

U_

08

05

_6

.3V

AM

~D

1

2

CC

16

51

0U

_0

80

5_

4V

AM

~D

CC

16

51

0U

_0

80

5_

4V

AM

~D

1

2

CC

16

21

0U

_0

80

5_

4V

AM

~D

CC

16

21

0U

_0

80

5_

4V

AM

~D

1

2

CC

16

41

0U

_0

80

5_

4V

AM

~D

CC

16

41

0U

_0

80

5_

4V

AM

~D

1

2

RC

73

20

K_

04

02

_5

%~

D@

RC

73

20

K_

04

02

_5

%~

D@1

2

CC

14

52

2U

_0

80

5_

6.3

VA

M~

DC

C1

45

22

U_

08

05

_6

.3V

AM

~D

1

2

RC79 0_0402_5%~D@RC79 0_0402_5%~D@1 2

CC178 0.1U_0402_10V7K~DCC178 0.1U_0402_10V7K~D12

QC5NTR4503NT1G_SOT23-3~D

QC5NTR4503NT1G_SOT23-3~D

1

2

3

CC

16

81

0U

_0

80

5_

4V

AM

~D

CC

16

81

0U

_0

80

5_

4V

AM

~D

1

2

VSS

JCPU1H

Sandy Bridge_rPGA_Rev1p0

VSS

JCPU1H

Sandy Bridge_rPGA_Rev1p0

VSS1AT35

VSS2AT32

VSS3AT29

VSS4AT27

VSS5AT25

VSS6AT22

VSS7AT19

VSS8AT16

VSS9AT13

VSS10AT10

VSS11AT7

VSS12AT4

VSS13AT3

VSS14AR25

VSS15AR22

VSS16AR19

VSS17AR16

VSS18AR13

VSS19AR10

VSS20AR7

VSS21AR4

VSS22AR2

VSS23AP34

VSS24AP31

VSS25AP28

VSS26AP25

VSS27AP22

VSS28AP19

VSS29AP16

VSS30AP13

VSS31AP10

VSS32AP7

VSS33AP4

VSS34AP1

VSS35AN30

VSS36AN27

VSS37AN25

VSS38AN22

VSS39AN19

VSS40AN16

VSS41AN13

VSS42AN10

VSS43AN7

VSS44AN4

VSS45AM29

VSS46AM25

VSS47AM22

VSS48AM19

VSS49AM16

VSS50AM13

VSS51AM10

VSS52AM7

VSS53AM4

VSS54AM3

VSS55AM2

VSS56AM1

VSS57AL34

VSS58AL31

VSS59AL28

VSS60AL25

VSS61AL22

VSS62AL19

VSS63AL16

VSS64AL13

VSS65AL10

VSS66AL7

VSS67AL4

VSS68AL2

VSS69AK33

VSS70AK30

VSS71AK27

VSS72AK25

VSS73AK22

VSS74AK19

VSS75AK16

VSS76AK13

VSS77AK10

VSS78AK7

VSS79AK4

VSS80AJ25

VSS81AJ22

VSS82AJ19

VSS83AJ16

VSS84AJ13

VSS85AJ10

VSS86AJ7

VSS87AJ4

VSS88AJ3

VSS89AJ2

VSS90AJ1

VSS91AH35

VSS92AH34

VSS93AH32

VSS94AH30

VSS95AH29

VSS96AH28

VSS97AH26

VSS98AH25

VSS99AH22

VSS100AH19

VSS101AH16

VSS102AH7

VSS103AH4

VSS104AG9

VSS105AG8

VSS106AG4

VSS107AF6

VSS108AF5

VSS109AF3

VSS110AF2

VSS111AE35

VSS112AE34

VSS113AE33

VSS114AE32

VSS115AE31

VSS116AE30

VSS117AE29

VSS118AE28

VSS119AE27

VSS120AE26

VSS121AE9

VSS122AD7

VSS123AC9

VSS124AC8

VSS125AC6

VSS126AC5

VSS127AC3

VSS128AC2

VSS129AB35

VSS130AB34

VSS131AB33

VSS132AB32

VSS133AB31

VSS134AB30

VSS135AB29

VSS136AB28

VSS137AB27

VSS138AB26

VSS139Y9

VSS140Y8

VSS141Y6

VSS142Y5

VSS143Y3

VSS144Y2

VSS145W35

VSS146W34

VSS147W33

VSS148W32

VSS149W31

VSS150W30

VSS151W29

VSS152W28

VSS153W27

VSS154W26

VSS155U9

VSS156U8

VSS157U6

VSS158U5

VSS159U3

VSS160U2

RC78100K_0402_5%~DRC78100K_0402_5%~D

12

CC

17

01

0U

_0

80

5_

4V

AM

~D

CC

17

01

0U

_0

80

5_

4V

AM

~D

1

2

CC

13

92

2U

_0

80

5_

6.3

VA

M~

DC

C1

39

22

U_

08

05

_6

.3V

AM

~D

1

2

CC

13

82

2U

_0

80

5_

6.3

VA

M~

DC

C1

38

22

U_

08

05

_6

.3V

AM

~D

1

2

CC

14

42

2U

_0

80

5_

6.3

VA

M~

DC

C1

44

22

U_

08

05

_6

.3V

AM

~D

1

2

RC138 0_0402_5%~D@RC138 0_0402_5%~D@1 2

CC

16

91

0U

_0

80

5_

4V

AM

~D

CC

16

91

0U

_0

80

5_

4V

AM

~D

1

2

RC72100K_0402_5%~DRC72100K_0402_5%~D

12

CC

14

72

2U

_0

80

5_

6.3

VA

M~

DC

C1

47

22

U_

08

05

_6

.3V

AM

~D

1

2

+ CC172330U_D2_2VM_R6M~D

+ CC172330U_D2_2VM_R6M~D

1

2

CC1364700P_0402_25V7K~DCC1364700P_0402_25V7K~D

1

2

CC

17

11

0U

_0

60

3_

6.3

V6

M~

D@

CC

17

11

0U

_0

60

3_

6.3

V6

M~

D@1

2

CC149 0.1U_0402_10V7K~DCC149 0.1U_0402_10V7K~D12

PJP2

PAD-OPEN 4x4m

@PJP2

PAD-OPEN 4x4m

@

1 2

CC

14

82

2U

_0

80

5_

6.3

VA

M~

DC

C1

48

22

U_

08

05

_6

.3V

AM

~D

1

2

CC

16

31

0U

_0

80

5_

4V

AM

~D

CC

16

31

0U

_0

80

5_

4V

AM

~D

1

2

CC

17

31

0U

_0

80

5_

4V

AM

~D

CC

17

31

0U

_0

80

5_

4V

AM

~D

1

2

CC

14

12

2U

_0

80

5_

6.3

VA

M~

DC

C1

41

22

U_

08

05

_6

.3V

AM

~D

1

2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_A_D0DDR_A_D1

DDR_A_D2DDR_A_D3

DDR_A_D4DDR_A_D5

DDR_A_D6DDR_A_D7

DDR_A_D8

DDR_A_D10DDR_A_D11

DDR_A_D18DDR_A_D19

DDR_A_D21

DDR_A_D26DDR_A_D27

DDR_A_D28DDR_A_D29

DDR_A_D32

DDR_A_D34DDR_A_D35

DDR_A_D36DDR_A_D37

DDR_A_D40DDR_A_D41

DDR_A_D42DDR_A_D43

DDR_A_D45

DDR_A_D46

DDR_A_D49

DDR_A_D50DDR_A_D51

DDR_A_D52DDR_A_D53

DDR_A_D55

DDR_A_D56DDR_A_D57

DDR_A_D58DDR_A_D59

DDR_A_D60DDR_A_D61

DDR_A_D62

DDR_A_MA2DDR_A_MA0DDR_A_MA1

DDR_A_MA3

DDR_A_MA4DDR_A_MA5DDR_A_MA6DDR_A_MA8

DDR_A_MA7DDR_A_MA9

DDR_A_MA10

DDR_A_MA11DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_BS0DDR_A_BS1

DDR_A_BS2

DDR_CS1_DIMMA#

DDR_CS0_DIMMA#

M_CLK_DDR0M_CLK_DDR#0

M_CLK_DDR1M_CLK_DDR#1

DDR_CKE0_DIMMA DDR_CKE1_DIMMA

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#M_ODT0

M_ODT1

DDR_A_D63

DDR_A_MA15

DDR_A_D23

DDR_A_D31

DDR_A_D17

DDR_A_D9 DDR_A_D13

DDR_A_D20DDR_A_D16

DDR_A_D25

DDR_A_D30

DDR_A_D24

DDR_A_D14DDR_A_D15

DDR_A_D12

DDR_A_D22

DDR_A_D39

DDR_A_D54

DDR_A_D33

DDR_A_D38

DDR_A_D47

DDR_A_D44

DDR_A_D48

DDR3_DRAMRST#_R

DDR3_DRAMRST#_R

+0.75V_DDR_VTT

+1.5V_MEM

+1.5V_MEM+1.5V_MEM

+3.3V_RUN

+0.75V_DDR_VTT+0.75V_DDR_VTT

+DIMM0_1_VREF_CA

+1.5V_MEM

+V_DDR_REF

+1.5V_MEM

+V_DDR_REF

+DIMM0_1_CA_CPU

+DIMM0_1_VREF_CPU

+DIMM0_1_VREF_DQ

DDR_A_D[0..63]8

DDR_A_DQS[0..7]8

DDR_A_MA[0..15]8

DDR_A_DQS#[0..7]8

DDR_CKE0_DIMMA8

DDR_A_BS28

DDR_CS1_DIMMA#8

DDR_A_WE#8DDR_A_CAS#8

DDR_A_BS08

DDR_A_BS1 8

M_ODT0 8

DDR_A_RAS# 8

M_CLK_DDR1 8M_CLK_DDR#1 8M_CLK_DDR#08

M_CLK_DDR08

DDR_XDP_WAN_SMBCLK 7,13,14,15,28,36

DDR_CKE1_DIMMA 8

DDR_CS0_DIMMA# 8

M_ODT1 8

DDR3_DRAMRST# 7DDR3_DRAMRST#_R13

DDR_XDP_WAN_SMBDAT 7,13,14,15,28,36

Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

DDRIII-SODIMM SLOT1

12 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

DDRIII-SODIMM SLOT1

12 75Thursday, January 13, 2011

Compal Electronics, Inc.Title

Size Document Number Rev

Date: Sheet of

LA-6592P 1.0

DDRIII-SODIMM SLOT1

12 75Thursday, January 13, 2011

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Layout Note:Place near JDIMMA

Layout Note:Place near JDIMMA.203,204

Populate RD1 for Intel DDR3VREFDQ multiple methods M1

JDIMMA H=5.2Note:Check voltage tolerance of VREF_DQ at the DIMM socket

All VREF traces should

have 10 mil trace width

2-3A to 1 DIMMs/channel

change footprint.

CD

13

10

U_

06

03

_6

.3V

6M

~D

@C

D1

31

0U

_0

60

3_

6.3

V6

M~

D@

1

2

CD

31

U_

04

02

_6

.3V

6K

~D

CD

31

U_

04

02

_6

.3V

6K

~D

1

2

RD7 0_0402_5%~D@RD7 0_0402_5%~D@1 2

CD

12

.2U

_0

60

3_

6.3

V6

K~

DC

D1

2.2

U_

06

03

_6

.3V

6K

~D

1

2

RD31 0_0402_5%~D@RD31 0_0402_5%~D@1 2

CD

11

10

U_

06

03

_6

.3V

6M

~D

CD

11

10

U_

06

03

_6

.3V

6M

~D

1

2

CD