A Fully Differential Low-PowerHigh-Linearity 77-GHz SiGe ...

A 3 – 5 GHz CMOS High Linearity Ultra Wideband Low Noise

Transcript of A 3 – 5 GHz CMOS High Linearity Ultra Wideband Low Noise

A 3 – 5 GHz CMOS High Linearity Ultra Wideband Low Noise Amplifier in 0.18µ CMOS

Long Bu and Joanne E. DeGroat

Electrical & Computer Engineering The Ohio State University

205 Dreese Lab, 2015 Neil Ave. Columbus, OH 43210 USA

Abstract: - In this paper, the significance of linearity for UWB front-end circuit is discussed. The effects of strong narrow band interferer on UWB signal are investigated. Wideband linearization techniques for UWB LNA are first proposed in this work. A high linearity UWB LNA is designed in TSMC 0.18µ CMOS process The simulation results show that the designed LNA exhibits very high IIP3 (6.9~13.8 dBm) while maintaining low noise figure (3~6 dB) over the design frequency range (3-5 GHz). Key-Words: - Ultra-wideband, receiver, low noise amplifier (LNA), distortion, high linearity, RFIC, CMOS 1 Introduction Recently, the UWB technology experienced a rapid development and draws many attentions. The very wide bandwidth of UWB communication makes the RF front-end very susceptible to strong narrow band interferers which can potentially block the desired signal. Thus high linearity LNA is highly desirable for UWB applications. Several LNA linearization theories and techniques for narrow band application has been reported and proved effective. However, no Ultra Wideband LNA linearization techniques have been proposed to date. In this paper, previous works on LNA linearity improvement are reviewed. Wideband linearization techniques is developed to improve the linearity of Ultra Wideband LNA while maintaining good noise figure and gain, which optimizes the dynamic range of the front end. A high linearity UWB LNA is designed in 0.18µm CMOS process and its performance is discussed. 2 Linearity Problem in UWB LNA

2.1 Significance of High Linearity LNA in

UWB System Noise figure has long been accepted as a major figure of merit for LNA. Then what is the significance of linearity in the design of UWB LNA? In presence of strong interferers, the nonlinearity of the LNA will result in many adverse effects such as desensitization, cross modulation and intermodulation, which degrade the performance of

the receiver. In most conventional receiver architecture, there is only one signal path from the front-end to the ADC. In this case, the latter stages in the receiver path become saturated before the LNA does. Thus the linearity of the overall receiver is mainly determined by the later stages but only slightly affected by the linearity of the LNA Many recent research works proposed receiver architectures that divide wideband signal into channels or subbands and process them separately [1-4]. In this research, the UWB LNA is developed for the OFDM UWB receiver that employs the concept of ADC in frequency domain [5]. The architecture of the receiver is shown in Fig. 1.

LNA

BPF LPF ADC

f1

BPF LPF ADC

f2

BPF LPF ADC

fn

Matched Filter

∫cT

dt0

)( S/H

∫cT

dt0

)( S/H

∫cT

dt0

)( S/H

D1

D2

Dn

Fig. 1 UWB receiver architecture

In this type of receiver architecture, if the strong narrow band interferers are present, one or several subband(s) may be blocked, while other subbands can still process the incoming signal. Thus the data stream can be kept uninterrupted. However, if the interferer is strong enough to saturate the LNA which processes the signal in all frequency bands, the whole receiver will be blocked. In these cases,

Proceedings of the 5th WSEAS Int. Conf. on CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL & SIGNAL PROCESSING, Dallas, USA, November 1-3, 2006 5

the linearity of the LNA determines the robustness of the receiver to strong interferers. 2.2 Effect of Non-linearity in UWB LNA Due to its wide bandwidth, the UWB receiver differs in many ways from its narrow band counterparts. Thus it is worthwhile to reevaluate the effect of non-linearity in UWB LNA. In conventional narrow band receiver, the main purpose of linearization is to minimize the IM products that can potentially fall in band. However, the wide bandwidth of UWB guarantees that strong narrowband interferes and their IM products will fall in band. This problem of narrow band nature can be solved using the channelized receiver architectures or advanced modulation techniques. In contrast, the efforts in UWB LNA linearization should be focused on the effect of strong narrow band interferers on the whole frequency band, or at least a significant portion of the overall bandwidth. A memoryless, time–variant non-linear amplifier can be described as a truncated power series which ignore the contribution of higher order nonlinearity:

33

2210)( vcvcvccvi +++≈ (1)

Suppose a strong narrow band interferer tA 11 cosω is present at the input of the amplifier, its effect on an arbitrary signal tone tA 22 cosω can be studied by looking into the output of the amplifier. If the relative bandwidth is smaller than 50%, the harmonics and 2nd order IM products fall out of band. Thus only fundamentals and 3rd order IM products are considered. Fig. 2 illustrates the relative magnitude of the fundamentals and the 3rd order IM products.

1ω 2ω212 ωω − 122 ωω −

43 2

213 AAc

43 1

223 AAc

2213

31311 2

343 AAcAcAc ++

2123

32321 2

343 AAcAcAc ++

Fig.2 fundamentals and the 3rd order IM products

First, the magnitude of the fundamental at 2ω is a function of the magnitude of the interferer A1. Assuming A1>>A2, the gain of the fundamental at

2ω can be approximated as )23( 2

131 Acc + . Since c3

is negative in most cases, the gain at 2ω is reduced

(desensitized) with large A1. In extreme case, the small signal gain drops to zero and the amplifier is blocked. Second, if the power level of the strong narrow band interferer varies with time, the amplitude of the fundamental at 2ω is modulated by the amplitude of the interferer. Third, the effect of 3rd order intermodulation is considered. From Fig. 2, it can be observed that the IM3 on the interferer side is stronger than the IM3 on the signal side, with a magnitude ratio of A1/A2. Considering that the radio emission level of UWB signal is limited to -42 dBm/MHz by FCC regulation, this magnitude ratio can be rather large. Thus the IM3 on the signal side is negligibly weak and only the IM3 on the interferer side needs to be considered. Now consider the intermodulation effect of strong narrow band interferer on the whole frequency band. A strong narrow band interferer essentially mirrors the whole spectrum around itself, attenuates the power level by and adds to the original spectrum, as shown in Fig. 3. Thus the power of the interferer is spread into the whole bandwidth through 3rd order intermodulation and increases the noise floor.

)3/()4( 2131 Acc

1ω 2ω212 ωω − Fig. 3 Effect of 3rd IM on UWB signal

The above discussion leads to the conclusion that desensitization (blocking), cross modulation and intermodulation are three major mechanisms that the strong narrow band interferer corrupts signal in a wide frequency range. Thus efforts should be made to improve the linearity of the UWB LNA and minimize these effects. 2.4 Limitations of Existing Linearity

Improvement Techniques Several techniques have been recently proposed to improve the linearity of LNA. The approach in [6]

Proceedings of the 5th WSEAS Int. Conf. on CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL & SIGNAL PROCESSING, Dallas, USA, November 1-3, 2006 6

optimizes the linearity of LNA by biasing the LNA at the optimum biasing point, where the 3rd order distortion of the amplifier equals zero. This technique suffers from its sensitivity to biasing voltage variation. In addition, its effectiveness is limited at high frequency due to the feedback path formed by the source degenerative inductor. Modified derivative superposition method [7] solves the biasing problem by using two MOSFET biased at different voltage, which produces relatively flat 3rd order coefficient near the zero crossing. The feedback problem at high frequency is solved by adding an additional source inductor. This method achieves very high IIP3 (22 dBm) in 0.25µ CMOS. Some other techniques, such as feed forward linearization [8, 9], and active post distortion method [10] also demonstrated their effectiveness in LNA linearization. However, these techniques are all narrow band in nature because the achieved high IIP3 relies on accurate phase match, which is impractical in UWB applications. 3 High Linearity UWB LNA Design 3.1 Wideband Linearization Techniques Due to the difficulty in direct application of the existing linearization techniques on UWB LNA, high linearity UWB LNA is rarely reported. The current reported state of art CMOS UWB LNA shows an IIP3 of around –5 dBm. In this work we propose wideband linearization techniques that are suitable for UWB LNA. In many UWB LNA designs, source follower is used as the output stage. Such implementation provides convenient output impedance match over broad frequency range. However, since the later stage has a more significant effect on linearity, the non-linearity of the output stage MOSFET can reduce the IIP3 of the overall LNA significantly. Thus to avoid using active device for output impedance match is very critical in designing high linearity LNA. In applications where output matching is necessary, passive impedance matching network can be used to provide a flat gain over the bandwidth. Careful selection of quality factor of LNA also helps in improving the linearity of the LNA. The quality factor of LNA is defined as

sgss RC

Qω

1= . Since the

signal is amplified by Qs before applied to the gate, high Qs will increase the overall gain but decrease

the linearity of the overall LNA. Thus excess gain can be traded for linearity by reducing the quality factor of LNA. The shrinking feature size of CMOS process also has a positive effect on the linearity of the LNA. For short channel devices, high electrical field results in velocity saturation of carriers. Thus the transconductance of the MOSFET approaches a constant value at high biasing voltage, which results in a much more linear behavior than its long channel counterpart. By choosing small channel length and increasing the biasing voltage Vgs, the linearity of the LNA can be greatly improved. 3.2 Noise Optimization At RF frequency, the thermal noise in the channel is the major source of noise in MOSFET device, the effect of which can be model by two correlated noise current generators at gate and drain. Starting from the classic two port noise model, the optimum source impedance for best noise performance is derived [11, 12]:

γδ

αω5

)1( 2cCG gsopt

−= )

51(

γδαω cCB gsopt −−= (2)

In equation (2), α is a parameter that reflects the degree to which the operation of the device deviates from the long channel regime, which is defined as:

0d

m

gg

=α (3)

At high biasing voltage which is required for linearity enhancement, the short channel effect becomes more magnificent and α takes smaller value. In order for Gopt to remain at the level of 50 Ω, Cgs has to be increased by increasing the device width. On the other hand, high biasing voltage results in high current density which mandates that the device width to be reduced in order to keep reasonable power consumption. This problem can be solved by choosing small device width to reduce the drain current and adding a capacitance Ct across the gate to maintain simultaneous input and noise match. 3.3 LNA Circuit Design Based on the wideband linearization techniques described above, a high linearity UWB LNA was designed in TSMC 0.18µ CMOS process with a power supply of 1.8 V. The LNA circuit is shown in Fig. 4. The designed LNA employs common source cascode architecture with inductive source degeneration. A 0.53 nH source inductor is used to generate a real impedance of 50 Ω at the input

Proceedings of the 5th WSEAS Int. Conf. on CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL & SIGNAL PROCESSING, Dallas, USA, November 1-3, 2006 7

without the thermal noise of a real resistor. The gate of the M1 is biased at a relatively high level of 1.06 V in order to improve the linearity of the LNA. A shunt capacitor Ct is placed across the gate. The purpose of this is two fold: first, the quality factor Qs of the LNA is reduced in favor of linearity; second, it helps to realize simultaneous input and noise match with high bias voltage. The drain current is 16 mA and the total power consumption is 29 mW.

Vin

Vout

M1

M2

Vbias

Ls

Lg

Ct

RL CL LL

C1

C2

C3

C4

L1

L2

L3 L4

Fig. 4 High Linearity UWB LNA circuit

Third order chebychev bandpass filter is used for wideband impedance match at the input. A 200 Ω resistor RL is placed in parallel with the load inductor LL in order to reduce the quality factor and thus increase the bandwidth. The output impedance match is realized using a 2nd order Butterworth filter and an impedance inverter. All the passive devices are implemented on chip except source inductance Ls, which is implemented using a bond wire.

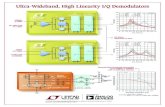

3.4 Simulation Results The designed UWB LNA is simulated using Cadence SpectreRF simulator. Fig. 5 shows the simulated S11 and S22 over the frequency range of 1 – 7 GHz. The designed LNA shows excellent input and output impedance match. The S11 and S22 remain lower than -12 dB over the 3 – 5 GHz frequency range. Fig. 6 shows the noise figure of the LNA is 3~6 dB in the 3 – 5 GHz range. The high Vgs of core transistor augments the noise figure slightly. The loss as a result of low Q on chip passive devices in the input matching network contributes the majority part of this noise figure. If the matching network is implemented off chip, the noise figure can be kept lower than 1.5 dB over the 3 – 5 GHz range.

The linearity of the designed LNA is evaluated by the IIP3 value acquired using two tone test. Fig. 7 show the simulated IIP3 over the frequency range of 1 – 7 GHz. For out of band signal, the IIP3 is rather high, which is the result of the strong attenuation from the matching network. For in band signal, the simulated IIP3 increases from 6.9 dBm at 3 GHz to 13.8 dBm at 5 GHz. This is because the quality factor of the LNA is lower at higher frequency. This level of IIP3 represents a significant improvement compared to current state of art design (IIP3<-5dBm). These results prove the effectiveness of the propose wideband linearization techniques.

Fig. 5 Simulated S11 and S22

Fig. 6 Noise figure of the LNA

0

10

20

30

40

50

1 2 3 4 5 6 7 8Frequency (GHz)

IIP3

(dB

m)

Fig. 7 Simulated IIP3 in 1 – 7 GHz

The S21 of the LNA is simulated and plotted as shown in Fig. 8. The maximum power gain of 9.3 dB is achieved at 3 GHz. The power gain decreases with increasing frequency and reaches a minimum of 5 dB at 5 GHz. This gain drop is a result of lower impedance of Cgs at higher frequency. The loss

Proceedings of the 5th WSEAS Int. Conf. on CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL & SIGNAL PROCESSING, Dallas, USA, November 1-3, 2006 8