8086 architecture

-

Upload

rishab-kataria -

Category

Engineering

-

view

118 -

download

3

Transcript of 8086 architecture

8086/8088 Microprocessor

Introduction to the processor and its pin configuration

Topics

• Basic Features

• Pinout Diagram

• Minimum and Maximum modes

• Description of the pins

Basic Features

• 8086 announced in 1978; 8086 is a 16 bit microprocessor with a 16 bit data bus

• 8088 announced in 1979; 8088 is a 16 bit microprocessor with an 8 bit data bus

• Both manufactured using High-performance

Metal Oxide Semiconductor (HMOS) technology

• Both contain about 29000 transistors• Both are packaged in 40 pin dual-in-line

package (DIP)

8086/8088 Pinout Diagrams

GNDAD14AD13AD12AD11AD10AD9AD8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGND

VCCAD15A16/S3A17/S4A18/S5A19/S6

HOLDHLDA

ALE

READYRESET

BHE/S7MN/MXRD

WRM/IODT/RDEN

INTATEST

1234567891011121314151617181920

3130292827262524232221

4039383736353433328086

GNDA14A13A12A11A10 A9 A8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGND

VCCA15A16/S3A17/S4A18/S5A19/S6

HOLDHLDA

ALE

READYRESET

SS0MN/MXRD

WRIO/MDT/RDEN

INTATEST

1234567891011121314151617181920

3130292827262524232221

4039383736353433328088

BHE has no meaning on the 8088 and has been eliminated

Multiplex of Data and Address Lines in 8088

• Address lines A0-A7 and Data lines D0-D7 are multiplexed in 8088. These lines are labelled as AD0-AD7. – By multiplexed we mean

that the same pysical pin carries an address bit at one time and the data bit another time

GNDA14A13A12A11A10 A9 A8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGND

VCCA15A16/S3A17/S4A18/S5A19/S6

HOLDHLDA

ALE

READYRESET

SS0MN/MXRD

WRIO/MDT/RDEN

INTATEST

1234567891011121314151617181920

3130292827262524232221

4039383736353433328088

Multiplex of Data and Address Lines in 8086

• Address lines A0-A15 and Data lines D0-D15 are multiplexed in 8086. These lines are labelled as AD0-AD15.

GNDAD14AD13AD12AD11AD10AD9AD8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGND

VCCAD15A16/S3A17/S4A18/S5A19/S6

HOLDHLDA

ALE

READYRESET

BHE/S7MN/MXRD

WRM/IODT/RDEN

INTATEST

1234567891011121314151617181920

3130292827262524232221

4039383736353433328086

Minimum-mode and Maximum-mode Systems

• 8088 and 8086 microprocessors can be configured to work in either of the two modes: the minimum mode and the maximum mode

Minimum mode: Pull MN/MX to logic 1 Typically smaller systems and contains a

single microprocessor Cheaper since all control signals for

memory and I/O are generated by the microprocessor.

Maximum mode Pull MN/MX logic 0 Larger systems with more than one

processor (designed to be used when a coprocessor (8087) exists in the system)

GNDAD14AD13AD12AD11AD10AD9AD8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGND

VCCAD15A16/S3A17/S4A18/S5A19/S6

HOLDHLDA

ALE

READYRESET

BHE/S7MN/MXRD

WRM/IODT/RDEN

INTATEST

1234567891011121314151617181920

3130292827262524232221

4039383736353433328086

Lost Signals in Max Mode

Minimum-mode and Maximum-mode Signals

GNDAD14AD13AD12AD11AD10AD9AD8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGND

VCCAD15A16/S3A17/S4A18/S5A19/S6

RQ/GT0RQ/GT1

QS0

READYRESET

BHE/S7MN/MXRD

LOCKS2S1S0

QS1TEST

1234567891011121314151617181920

3130292827262524232221

4039383736353433328086

Max Mode

GNDAD14AD13AD12AD11AD10AD9AD8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGND

VCCAD15A16/S3A17/S4A18/S5A19/S6

HOLDHLDA

ALE

READYRESET

BHE/S7MN/MXRD

WRM/IODT/RDEN

INTATEST

1234567891011121314151617181920

3130292827262524232221

4039383736353433328086

Min Mode

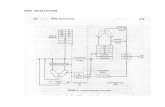

Vcc GND

808

6 C

PU

F / CA E N 1A E N 2

C l o c kg e n e r a t o r

+ 5 V

R E S

W a i t - S t a t eG e n e r a t o r

C L KR E A D YR E S E T

M / I OI N T A

R DW R

P C L K

M N / M X + 5 V

S T B

O E

8 2 8 2L a t c h

A L E

A D 0 - A D 1 5A 1 6 - A 1 9

B H E B H E

D 0 - D 1 5

8 2 8 6

D T / RD E N

TO E

1 6

A 0 - A 1 9

A d d r e s s B u s

C o n t r o lB u s

8086 System Minimum mode

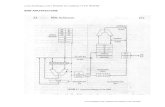

8086

CP

U

C l o c kg e n e r a t o r

W a i t - S t a t eG e n e r a t o r

C L K

R E A D Y

R E S E T

M N / M X

A D 0 - A D 1 5A 1 6 - A 1 9 B H E

S T B

O E

8 2 8 2L a t c h

A 0 - A 1 9

A d d r e s s B u s

+ 5 V

R E SS 0

S 1

S 2

C L KS 0

S 1

S 2

D A T A

8 2 8 6T r a n s c e i v e r

T

O E

A L E

G n d

D E N

D T / R

M R D C

M W T C

I O R C

I O W C

A I O W C

A M W C

I N T A

8288

Bus

Con

tro

ller

8086 System Maximum Mode

Description of the Pins

GNDAD14AD13AD12AD11AD10AD9AD8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGND

VCCAD15A16/S3A17/S4A18/S5A19/S6

RQ/GT0RQ/GT1

QS0

READYRESET

BHE/S7MN/MXRD

LOCKS2S1S0

QS1TEST

1234567891011121314151617181920

3130292827262524232221

4039383736353433328086

Max Mode

GNDAD14AD13AD12AD11AD10AD9AD8AD7AD6AD5AD4AD3AD2AD1AD0NMIINTRCLKGND

VCCAD15A16/S3A17/S4A18/S5A19/S6

HOLDHLDA

ALE

READYRESET

BHE/S7MN/MXRD

WRM/IODT/RDEN

INTATEST

1234567891011121314151617181920

3130292827262524232221

4039383736353433328086

Min Mode

Vcc GND

CPU component Contents

Flags Cleared

Instruction Pointer 0000H

CS FFFFH

DS, SS and ES 0000H

Queue Empty

RESET Operation results

AD0 – AD15 Address

Data

AD0 - AD15: Address Data Bus

A17/S4 A16/S3 Function

0

0 Extra segment access

0

1 Stack segment access

1

0 Code segment access

1 1 Data segment access

A17/S4, A16/S3 Address/Status

A18/S5: The status of the interrupt enable flag bit is updated at the beginning of each cycle. The status of the flag is indicated through this pin

A19/S6: When Low, it indicates that 8086 is in control of the bus. During a "Hold acknowledge" clock period, the 8086 tri-states the S6 pin and thus allows another bus master to take control of the status bus.

A19/S6, A18/S5 Address/Status

S2 S1 S0 Characteristics

0 0 0 Interrupt acknowledge

0 0 1 Read I/O port

0 1 0 Write I/O port

0 1 1 Halt

1 0 0 Code access

1 0 1 Read memory

1 1 0 Write memory

1 1 1 Passive State

S0, S1 and S2 Signals

QS1 QS1 Characteristics

0 0 No operation

0 1 First byte of opcode from queue

1 0 Empty the queue

1 1 Subsequent byte from queue

QS1 and QS2 Signals

IO/M DT/R SSO CHARACTERISTICS

0 0 0 Code Access

0 0 1 Read Memory

0 1 0 Write Memory

0 1 1 Passive

1 0 0 Interrupt Acknowledge

1 0 1 Read I/O port

1 1 0 Write I/O port

1 1 1 Halt

Read Write Control Signals

Data can be accessed from the memory in four different ways:

• 8 - bit data from Lower (Even) address Bank.

• 8 - bit data from Higher (Odd) address Bank.

• 16 - bit data starting from Even Address.

• 16 - bit data starting from Odd Address.

8086 Memory Addressing

H i g h e rA d d r e s s

B a n k( 5 1 2 K x 8 )

O D D

L o w e rA d d r e s s

B a n k( 5 1 2 K x 8 )

E V E N

A 1 - A 1 9A d d r e s s B u s

D a t a B u s ( D 0 - D 1 5 )

D 8 - D 1 5 D 0 - D 7

B H E A 0

Treating Even and Odd Addresses

A 1 - A 1 9

D 0 - D 1 5

B H E = 1D 8 - D 1 5 D 0 - D 7

A 0 = 0

x

x + 2

x + 4

x + 1

x + 3

x + 5

O d d B a n k E v e n B a n k

8-bit data from Even address Bank

MOV SI,4000HMOV AL,[SI+2]

A 1 - A 1 9

D 0 - D 1 5

B H E = 0 A 0 = 1

x

x + 2x + 1x + 3

O d d B a n k E v e n B a n k

D 8 - D 1 5D 0 - D 7

8-bit Data from Odd Address Bank

MOV SI,4000HMOV AL,[SI+3]

A 1 - A 1 9

D 0 - D 1 5

B H E = 0A 0 = 0

x

x + 2x + 1x + 3

O d d B a n k E v e n B a n k

D 8 - D 1 5

D 0 - D 7

16-bit Data Access starting from Even Address

MOV SI,4000HMOV AX,[SI+2]

A 1 - A 1 9

O d d B a n k E v e n B a n k

D 8 - D 1 5D 0 - D 7

A 1 - A 9

0 0 0 5

0 0 0 70 0 0 9

0 0 0 40 0 0 60 0 0 8

A 1 - A 1 9

O d d B a n k E v e n B a n k

D 8 - D 1 5D 0 - D 7

A 1 - A 9

0 0 0 5

0 0 0 70 0 0 9

0 0 0 40 0 0 60 0 0 8

( a ) F i r s t A c c e s s f r o m O d d A d d r e s s ( b ) N e x t A c c e s s f r o m E v e n A d d r e s s

16-bit Data Access starting from Odd Address

MOV SI,4000HMOV AX,[SI+5]

T 1 T 2 T 3 T w a i t T 4

C L K

A D 0 - A D 1 5

B H E

A L E

S 2 S 0-

M / I O

R D

R E A D Y

D T / R

D E N

W R

Read Timing Diagram

Write Machine Cycle

• INTR is used to request a hardware interrupt.• It is recognized by the processor only when IF =

1, otherwise it is ignored (STI instruction sets this flag bit).

• The request on this line can be disabled (or masked) by making IF = 0 (use instruction CLI)

• If INTR becomes high and IF = 1, the 8086 enters an interrupt acknowledge cycle (INTA becomes active) after the current instruction has completed execution.

INTR (input)Hardware Interrupt Request Pin

• If I/O peripheral wants to interrupt the processor, the “interrupt controller” will send high pulse to the 8086 INTR pin.

• What about if a simple system to be built and hardware interrupts are not needed;

What to do with INTR and INTA?

For Discussion

• The Non Maskable Interrupt input is similar to INTR except that the NMI interrupt does not check to see if the IF flag bit is at logic 1.

• This interrupt cannot be masked (or disabled) and no acknowledgment is required.

• It should be reserved for “catastrophic” events such as power failure or memory errors.

NMI (input) Non-Maskable Interrupt line

8086 External Interrupt Connections

NMI - Non-Maskable Interrupt INTR - Interrupt Request

Interrupt Logic

int intoDivideError

SingleStep

NMI Requesting Device

8086 CPUIntel

8259A

PIC

NMI

INTR

Software Traps

Programmable Interrupt Controller

(part of chipset)

• The TEST pin is an input that is tested by the WAIT instruction.

• If TEST is at logic 0, the WAIT instruction functions as a NOP.

• If TEST is at logic 1, then the WAIT instruction causes the 8086 to idle, until TEST input becomes a logic 0.

• This pin is normally driven by the 8087 co-processor (numeric coprocessor) .

• This prevents the CPU from accessing a memory result before the NDP has finished its calculation

TEST (input)

• This input is used to insert wait states into processor Bus Cycle.

• If the READY pin is placed at a logic 0 level, the microprocessor enters into wait states and remains idle.

• If the READY pin is placed at a logic 1 level, it has no effect on the operation of the processor.

• It is sampled at the end of the T2 clock pulse

• Usually driven by a slow memory device

Ready (input)

CLK

Ready

Reset

+ 5 VR

C

RES

X1

X2

F/C

RDY1RDY2

8284

AEN1AEN2

RESET KEY

8086 Microprocessor

8284 Connected to 8086 Mp

• The HOLD input is used by DMA controller to request a Direct Memory Access (DMA) operation.

• If the HOLD signal is at logic 1, the microprocessor places its address, data and control bus at the high impedance state.

• If the HOLD pin is at logic 0, the microprocessor works normally.

HOLD (input)

• Hold acknowledge is made high to indicate to the DMA controller that the processor has entered hold state and it can take control over the system bus for DMA operation.

HLDA (output)Hold Acknowledge Output

DMA Operation