piezoMEMS competence centre established at SINTEF T …€¦ · · 2013-04-29piezoMEMS competence...

Transcript of piezoMEMS competence centre established at SINTEF T …€¦ · · 2013-04-29piezoMEMS competence...

7/02/13 | ISSUE N°139 | 3

piezoMEMS competence centre established at SINTEF

INSIDE…

REVERSE COSTING

The MEMS market is increasingly turning its attention to creating semiconductor-based devices that convert real-world

non-digital as wel l as non-elec tronic information such as mechanical, thermal, acoustic, chemical, optical and biomedical phenomena to and from the digital domain. One particularly promising technology is the integration of piezoelectric thin films with silicon MEMS.Piezoelectr ic ity is the abil ity of some materials to generate an electric potential in response to applied mechanical stress. The piezoelectric effect is reversible in that

materials exhibiting the direct piezoelectric effect (the production of electricity when stress is applied) also exhibit the converse piezoelectric effect (the production of stress and/or strain when an electr ic f ield is applied). This is what makes the piezoMEMS technology so versatile. Due to this two-way operation of piezoelectric materials - going all the way from DC operation to several tens of MHz - piezoMEMS technology provides a huge pool of design opportunities.A market analysis for piezoMEMS based devices was recently performed by Yole Développement. PiezoMEMS have already

demonstrated their potential for use in mass product applications like ink-jet print heads by EPSON and Matsushita. As of 2012/2013 there are many others to come. Examples of known future applicat ions inc lude RF switches, fi lters, gyro sensor, tilted mirror arrays, energy harvesters, particle detection for biomedical applications and actuators for fi ne positioning- i.e. for optical lenses (www.polight.com).

The piezoMEMS processpiezoMEMS is fabricated using modif ied versions of established MEMS processes as well as specially developed add-on processes. To develop this process deep knowledge about piezo and ferroelectric materials were needed and it is important to realize that the rules and processes used when designing and fabricating Si-MEMS often cannot be applied to piezoMEMS. One important issue is the incompatibility of non-CMOS materials in most MEMS fabs.The full fabrication chain, including the development of high volume tools for thin fi lm deposition and in-line quality control, has been in focus for several years, most recently through the FP7 project piezoVolume- coordinated by SINTEF.

The competence centreThe piezoMEMS Competence Centre at SINTEF (www.piezomicrosystems.com) is a perfect match for small and medium size companies that want to get started with piezoelectric MEMS based on PZT. Since piezoMEMS technology is quite new, and there are no open facilities for volume production of piezoMEMS, it is natural that the barrier for considering piezoMEMS

technology is quite high. The Competence Centre has a large network of infrastructure as well as experts able to guide people through the challenges with this new technology. We cover the whole process from design to packaging and offer small-scale production of devices. People within the Competence Centre have worked with design, model l ing, process development and prototyping of piezoMEMS since 2002 and several successful projects have been completed. The unique experience that has been acquired reduces the risks and time-to-marked for our customers. Technology transfer from prototyping to high volume production is ensured through collaboration with independent MEMS fabs – in addition to the in-house capabilities at SINTEF. The continuing research in material science and fabrication processes at SINTEF ensures access to state-of-the-art technology. SINTEF has taken a leading role in the competence center, in a joint effort with our technology partners to bring piezoMEMS to the market.www.piezomicrosystems.comwww.sintef.no

Embedded die packaging is an emerging solution for increased integration in mobile products. It’s supported by a

game-changing, low-cost, panel-based PCB infrastructure that has the potential to create an alternative supply chain for t oday ’s we l l - e s t ab l i shed packag ing standards.Rohm and TDK-EPC have joined forces to p r ov ide an a l t e r na t i ve s o lu t i on f o r embedded die technology.

This SiP module is a second-source supply version of Texas Instruments’ MicroSiP™ DC-DC Converter, with packaging from AT&S (see our article in Micronews #125).

TDK-EPC’s embedded die processT D K- E P C ’ s p r o c e s s , c a l l e d S E S U B (Semiconductor Embedded in SUBstrate), is an innovat ive SiP module packaging

t e chno logy based on t he emerg ing “embedded die in laminate substrate” concept. Most of the packaging assembly operations are done at the panel-scale level, and a fan-out area with a four layers 3D in te r c onnec t i on r ou t ing pa th i s provided.

This packaging technology extends the package size beyond the IC surface area and a l l ows f o r mount ing add i t i ona l components such as discretes and passives on top of the laminated SiP module.

Supply chain and costing resultsWe believe that manufacture of the IC die and copper RDL are handled by Rohm Semiconduc tor in Japan. The SESUB packaging is performed by TDK-EPC on a large-scale panel in Japan, allowing for assembly o f thousands o f packages simultaneously.

A l t hough f u l l y c ompat ib l e w i th the previously analyzed TI module, the process and cost structure is very different.

A full reverse costing report, including technological analysis of the device and detailed manufacturing costs, is currently available.

Rohm DC/DC micro converter using TDK-EPC embedded die packaging

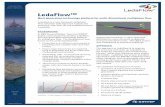

piezoMEMS wafer before dicing. Several design-types for various technology demonstrators are shown for this joint

piezoVolume project wafer. (Courtesy of Sintef)

Device fabrication

Market value

Model

Design

Processand fab

M

Design n

Ideasand IP

piezoMEMS Competence Center covers the whole piezoMEMS process, illustrated here as the working tools of hardware and know-how needed for manufacturing piezoMEMS. (Courtesy of Sintef)

CONSULTING

Recent reverse costing reports• ST LSM333D: 4x4mm 9-Axis IMU• Luxtera Silicon Photonic Die• TI DLP: nHD Pico Projector• SETi UVTOP270: UV LED• Mitsubishi CM450DY-24S: 1200V IGBT Power

Module

System Plus Consulting develops costing tools and performs on demand reverse costing studies of semiconductors (from integrated circuits to power devices, from single chip packages to MEMS and multichip modules) & of electronic boards and systems.

www.systemplus.fr

SiP module cost breakdown (Courtesy of System Plus Consulting)

SiP cross-section and drawing(Courtesy of System Plus Consulting)

IC Die Cost60%

SESUB PackagingCost + TDK-EPC

Overheads20%

Passives AssemblyCost EMSOverheads

8%Final test + Yield

losses cost2 %Passives

Components Cost10%

Embedded active component

Inductor Capacitor Capacitor

Four redistribution

layers Solder ball

Rohm DC-DC micro converter(Courtesy of System Plus Consulting)