EE382V: Embedded System Design and...

Transcript of EE382V: Embedded System Design and...

EE382V:

Embedded System Design and Modeling

Andreas Gerstlauer

Electrical and Computer Engineering

University of Texas at Austin

Lecture 4 – System Design Flow and Methodology

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 2

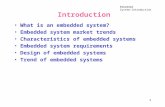

Lecture 4: Outline

• SpecC system design methodology

• From specification to implementation

–Specification

–System design

–Processor design

• Models and transformations

–Specification model

–Computation model

–Communication model

– Implementation model

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 3

System Design

• Specification to architecture to implementation

• Behavior to structure

1. System level: system specification to system architecture

2. Processor level: component behavior to component microarchitecture

Specification

+ constraints

Memory

Memory

µProcessor

Interface

Comp.IP

Bus

Interface

Interface

Interface

Custom HW

System architecture

+ estimates

Processors

IPs

Memories

Busses

Processor Implementation

+ results

Registers

ALUs/FUs

Memories

Gates

Mem RFState

Control

ALU

Datapath

PC

Control Pipeline

State

IF FSM

State

IF FSM

IP NetlistRAM

IR

Memory

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 4

System Design Needs

• Design models

• Representation for validation and analysis

• Specification for further implementation/synthesis

• Design languages

• Specification down to implementation– Models of Computation (MoC)

• System-level design languages (SLDL)– C-based, event-driven SLDLs [SpecC, SystemC]

� Well-defined, rigorous system-level semantics

� Unambiguous, explicit abstractions, models– Objects and composition rules

� Systematic flow from specification to implementation– Transformations and refinements

� Modeling flow

� Design automation for synthesis and verification

Flow

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 5

System Design Process

Computation

Communication

A B

C

D F

Un-

timedApproximate-

timed

Cycle-

timed

Un-

timed

Approximate-

timed

A. System specification model

B. Component model

C. Bus-arbitration model

D. Bus-functional model

E. Cycle-accurate computation model

F. RTL/ISS Implementation model

E

Cycle-

timed

Source: Lukai Cai, D. Gajski. “Transaction level modeling: An overview”, ISSS 2003

• Abstraction based on level of detail (structure/timing)

• Computation and communication

� System design flow

� Path from model A to model F

� Design methodology

� Set of models and transformations between models

© 2008 A. Gerstlauer 6

Top-Down Design Flow

Implementation

Architecture

Specification

Logic design

Product planning

Structure Timing

System design

Processor design

pure functional

bus functional

RTL / IS

requirements

untimed

timing accurate

cycle accurate

constraints

gates gate delays

© 2008 A. Gerstlauer 7

Top-Down Design Flow

Implementation model

Communication model

Specification model

Logic design

Product planning

pure functional

transaction level

bus functional

RTL / IS

requirements

untimed

estimated timing

timing accurate

cycle accurate

constraints

Computation model

Processor design

Communication design

Computation design

Structure Timing

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 8

Top-Down Design Flow

untimed

estimated timing

timing accurate

cycle accurate

constraints

pure functional

transaction level

bus functional

RTL / IS

requirements

Specification model

Algor.IP

Proto.IP

Computation model

Communication refinement

Comp.IP

Implementation model

Software

synthesisInterface

synthesis

Hardware

synthesisRTOSIP

RTLIP

Computation refinement

Capture

Communication model

Product planning

Logic designStructure Timing

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 9

Design Methodology

System design Validation flow

Specification model

Algor.IP

Proto.IP

Computation model

Communication refinement

Communication model

Comp.IP

Estimation

ValidationAnalysis

Compilation Simulation model

Estimation

ValidationAnalysis

Compilation Simulation model

Estimation

ValidationAnalysis

Compilation Simulation model

Implementation model

Software

compilation

Interface

synthesis

Hardware

synthesis

BackendEstimation

ValidationAnalysis

Compilation Simulation model

RTOSIP

RTLIP

Computation refinement

Capture

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 10

Specification Model

• High-level, abstract model

• Pure system functionality

• Algorithmic behavior

• No implementation details

• No implicit structure / architecture

• Behavioral hierarchy

• Untimed

• Executes in zero (logical) time

• Causal ordering

• Events only for synchronization

Specification model

Computation refinement

Computation model

Communication model

Implementation model

Communication refinement

Processor refinement

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 11

Specification Model Example

B1

v1

v2

e2

B1

B2 B3

• Simple, typical specification model

• Hierarchical parallel-serial composition

• Communication through ports and variables, events

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 12

Specification Level Communication

• Message-passing

• Abstract communication

and synchronization

• Encapsulate in channel

B2 B3

c2

v2

e2

B2 B3

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 13

Clean Specification Model Example

B2 B3

c2

B1

v1

B1

• Synthesizable specification model

• Hierarchical parallel-serial composition

• Communication through variables and standard channels

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 14

Computation Refinement

• PE allocation / selection

• Behavior partitioning

• Variable partitioning

• Scheduling

Specification model

Computation refinement

Computation model

Communication model

Implementation model

Communication refinement

Processor refinement

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 15

PE Allocation, Behavior Partitioning

• Allocate PEs

• Partition behaviors

• Globalize communicationB2 B3

c2

B1

v1

B1

� Additional level of hierarchy to model PE structure

PE1

PE2

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 16

Model after Behavior Partitioning

B3B2

B1B1 PE1

c2

v1

B13rcv

B34snd

B13snd

B34rcv

cb13

cb34

PE2

� Synchronization to preserve execution order/semantics

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 17

• Map global variables to local memories

Variable Partitioning

� Shared memory vs. message passing implementation

B3

B13rcv

B34snd

B2

B1B1

B13snd

B34rcv

PE1

c2

v1

cb13

cb34

PE2

v1 v1

• Communicate data over message-passing channels

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 18

Model after Variable Partitioning

B3

B13rcv

B34snd

B2

B1B1

B13snd

B34rcv

PE1

c2

v1

cb13

cb34

PE2

v1

� Keep local variable copies in sync• Communicate updated values at synchronization points• Transfer control & data over message-passing channel

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 19

Timed Computation

• Execution time of behaviors

• Estimated target delay / timing budget

• Granularity

• Behavior / function / basic-block level

� Annotate behaviors

• Simulation feedback

• Synthesis constraints

behavior B2( in int v1, ISend c2 )

{

void main(void) {

…

waitfor( delay1 );

c2.send( … );

…

}

};

waitfor( B2_DELAY1 );waitfor( B2_DELAY1 );

waitfor( B2_DELAY2 );waitfor( B2_DELAY2 );

1

5

10

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 20

Scheduling

• Static scheduling

– Fixed behavior execution order

– Flattened behavior hierarchy

� Serialize behavior execution on components

B2

B1B1

B13snd

B34rcv

PE1

• Dynamic scheduling

– Pool of tasks

– Scheduler, abstracted OS

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 21

Computation Model Example

B3

B13rcv

B34snd

B2

B1B1

B13snd

B34rcv

PE1

c2

v1

cb13

cb34

PE2

v1

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 22

Computation Model

• Component structure/architecture

• Top level of behavior hierarchy

• Behavioral/functional component view

• Behaviors grouped under top-level

component behaviors

• Sequential behavior execution

• Timed

• Estimated execution delays

Specification model

Computation model

Communication model

Implementation model

Processor refinement

Computation refinement

Communication refinement

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 23

Communication Refinement

• Network allocation / protocol selection

• Channel partitioning

• Protocol stack insertion

• Inlining

Specification model

Computation model

Communication model

Implementation model

Processor refinement

Communication refinement

Computation refinement

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 24

Network Allocation / Channel Partitioning

B3

B34snd

B2

B1B1

B13snd

B34rcv

PE1

c2

v1

cb13

cb34

PE2

v1

B13rcv

• Allocate busses

• Partition channels

• Update

communication

� Additional level of hierarchy to model bus structure

Bus1

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 25

Model after Channel Partitioning

B3

B34snd

B2

B1B1

B13snd

B34rcv

PE1

v1

PE2

v1

B13rcv

c2

cb13

cb34

Bus1

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 26

Protocol Insertion

c2

cb13

cb34

Bus1

Protocol

Layer

Network

Layers

Bus1

• Insert protocol layer

• Bus protocol channel from database

• Create network layers

• Implement message-passing over bus protocol

• Replace bus channel

• Hierarchical combination of complete protocol

stack

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 27

Model after Protocol Insertion

B2

B1B1

B13snd

B34rcv

PE1

v1

B3

B34snd

PE2

v1

B13rcv

Bus1

IBusSlave

IBusMaster

ready

address[15:0]

data[31:0]

BusProtocol

Master Slave

IProtocolSlave

IProtocolMaster

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 28

Inlining

Bus1

IBusSlave

IBusMaster

control

address[15:0]

data[31:0]

BusProtocol

IProtocolSlave

IProtocolMaster

PE1 PE2

PE2PE2Bus

IBusSlave

PE2Protocol

IProtocolSlave

PE1Bus

IBusMaster

PE1Protocol

IProtocolMaster

PE1

ready

address[15:0]

data[31:0]

• Create bus interfaces

and drivers

• Refine

communication

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 29

Communication Model Example

control

address[15:0]

data[31:0]

B3

B34snd

v1

B13rcv

B2

B1B1

B13snd

B34rcv

PE1

v1

PE2

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 30

Communication Model

• Component & bus structure/architecture

• Top level of hierarchy

• Bus-functional component models

• Timing-accurate bus protocols

• Behavioral component description

• Timed

• Estimated component delays

Specification model

Computation model

Communication model

Implementation model

Processor refinement

Communication refinement

Computation refinement

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 31

Processor Refinement

• Cycle-accurate implementation of PEs

• Hardware synthesis down to RTL

• Software synthesis down to IS

• Interface synthesis down to RTL/IS

Specification model

Computation model

Communication model

Implementation model

Processor refinement

Communication refinement

Computation refinement

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 32

Hardware Synthesis

• Schedule operations into clock cycles

• Define clock boundaries in leaf behavior C code

• Create FSMD model from scheduled C code

B3

B34snd

v1

B13rcv

PE2

PE2_CLK

PE2_CLK

PE2_CLK

Clock boundaries

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 33

Software Synthesis

• Implement behavior on processor instruction-set

• Code generation

• Compilation

B2

B1B1

B13snd

B34rcv

PE1

v1

Ff2

MOVE r0, r1

SHL r3

ADD r2, r3, r4

INC r2

PUSH r1

CALL Ff3

POP r0

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 34

Interface Synthesis

• Implement communication on components

• Hardware bus interface logic

• Software bus drivers

PE2Bus

IBusSlave

PE2Protocol

IProtocolSlave

ready

ack

addr[15:0]

data[31:0]

PE1Bus

IBusMaster

PE1Protocol

IProtocolMaster

ready

ack

addr[15:0]

data[31:0]

S0

S1

S2

S3

S4

DRV

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 35

Implementation Model

Software processor Custom hardware

ready

ack

address[15:0]

data[31:0]

PE2

PE2_CLKPE1_CLK

OBJ

PORTA

PORTB

INTA

PORTC

PE1

Instruction

Set

Simulator

(ISS)

S0

S1

S2

S3

S4

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 36

Implementation Model

• Cycle-accurate system description

• RTL description of hardware

– Behavioral/structural FSMD view

• Object code for processors

– Instruction-set co-simulation

• Clocked bus communication

– Bus interface timing based on PE clock

Specification model

Architecture model

Communication model

Implementation model

Processor refinement

Communication synthesis

Architecture exploration

EE382V: Embedded Sys Dsgn and Modeling, Lecture 4 © 2008 A. Gerstlauer 37

Lecture 4: Summary

• Design methodology

• Four levels of abstraction– Specification model: untimed, functional

– Computation model: estimated, structural

– Communication model: timed, bus-functional

– Implementation model: cycle-accurate, RTL/IS

• Three refinement steps– Computation refinement

– Communication refinement

– Processor refinement

» HW / SW / interface synthesis

• Well-defined, formal models & transformations– Automatic, gradual refinement

– Executable models, test bench re-use

– Simple verification

![SE100-Cpp UT Intro.pptx [Read-Only]users.ece.utexas.edu/~gerstl/ee382v-ics_f09/lectures/lecture_1a.pdf– Simple data, Conditionals, Loops & Functions • Modular programming – Namespaces,](https://static.fdocuments.us/doc/165x107/602366b71283a5133910b458/se100-cpp-ut-intropptx-read-onlyusersece-gerstlee382v-icsf09lectureslecture1apdf.jpg)