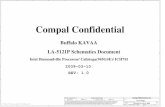

Compal Confidential...LA-2301 0.2 Cover Sheet B Thursday, April 08, 2004 147 Compal Confidential...

Transcript of Compal Confidential...LA-2301 0.2 Cover Sheet B Thursday, April 08, 2004 147 Compal Confidential...

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

Cover SheetB

1 47Thursday, April 08, 2004

Compal ConfidentialFortworth20 EDW10 Schematic Document

Intel Protability Processor with ATi RC300ML + IXP1502004-03-16

REV: 0.2

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

Block DiagramB

2 47Thursday, April 08, 2004

LPC BUS

Clock Generator

PCI BUS

Block DiagramCompal confidential

Model Name : Fortworth 20

USB conn

Thermal SensorADM1032

page 5

A-LinkUSBx3USB port 0, 1, 2, 3

AMP& PhoneJack

page 30ALC250

AC97 Codec MDC

Power CircuitDC/DC

CardBus / SD / SM /MMC / MS Pro / XD

page 24

ENE CB714

Slot 0page 25

BGA-457Pin

BGA-718 Pin

FSB

Fan Controlpage 37

page 37

DC/DC InterfaceSuspend

ATi SB200C IXP 150

Touch Pad

K/B Controller

uFCPGA 478 Pin

400/533 MHz

3.3V 33MHz3.3V 48MHz USB2.0

3.3V 24.576MHz

3.3V ATA100

3.3V 33MHz

File Name : LA-2301 Rev: 0.1

page 19,20,21,22

HDDpage 23

AC-Link

ATi RC300ML

page 31

CDROM

ENE KB910\

page 33Power On/OffReset & RTC

page 35

page 23

page 30

page 29

page 4,5,6

page 17

page 7,8,9,10,11,12

ICS951402

HD#(0..63)HA#(3..31)

66MHz 4X 266MB/s

200pin DDR-SODIMM X1BANK 0, 1, 2, 3

page 15,16

Memory BUS(DDR)2.5V 200MHz DDR266/333

page 30

RJ11

T/P Switch Board

page 38,39,40,41 42,43,44,45,46

Compal Electronics, Inc.

LVDS Connectorpage 18

page 18

CRT Connector

On Board RAMx 8 cells

LAN

page 26

Realtek RTL8100CL

RJ45page 26

TV Connectorpage 10

Super I/O

Mini-PCI

page 28

IEEE 1394

page 27

TI TSB43AB21A

5 in 1Conn.

page 25

page 13,14

SMsCLPC47N217

page 32

page 34

Flash ROM

page 33Int.KBD

EC I/O Bufferpage 34

SST39VF040-90-4C-NH

page 32

FIR Module

Parallel Portpage 32

TFDU6102-TR3

NorthWood-MT -- 533Presscot-MT--533

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

NotesB

3 47Thursday, April 08, 2004

ON

+CPU_CORE

Voltage Rails

VINB+

ONOFF OFF

Adapter power supply (19V)AC or battery power rail for power circuit.Core voltage for CPU

+1.8VS

+5VS

+CPU_VID ON OFF OFF1.2V rail for Processor VID

+2.5VS 2.5V switched power railON ON*

+3VS

S0-S1 S3 S5

ON OFF

ON OFF

N/A N/A N/AN/AN/AN/A

Power Plane Description

OFF

OFF

ON

OFF

+3VOFF

OFF

ON

2.5V always on power rail

3.3V power rail

RTCVCC

OFF

ON+12VALW

ON

+5VALW

ON

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

+3VALW

12V always on power rail

ON

ON*

5V always on power rail

ONOFF

3.3V always on power rail

ON

ON

ON

ONON

ON

+2.5V

5V switched power rail

OFF

ON*

2.5V power rail

3.3V switched power rail

RTC power

OFF

ON

OFFON

+1.25VS 1.25V switched power rail1.8V switched power rail

+2.5VALW ON*ON*

Vcc 3.3V +/- 5%100K +/- 5%Ra

Board ID Rb V min0123

08.2K +/- 5%

0 V0.216 V 0.250 V 0.289 V0.436 V0.712 V

0.503 V0.819 V

0.538 V0.875 V

AD_BID V typAD_BID VAD_BID max

18K +/- 5%33K +/- 5%56K +/- 5%100K +/- 5%200K +/- 5%

3.300 V

0 V 0 V

4567 NC

1.036 V1.453 V 1.650 V 1.759 V1.935 V2.500 V

2.200 V3.300 V

2.341 V

1.185 V 1.264 V

Board ID PCB Revision0.1

Board ID Table for AD channel

01234567

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

EC SM Bus1 addressDevice Address Address

1010 000X b

ADM1032

EC SM Bus2 addressDevice

Smart Battery

EEPROM(24C16)

1001 100X b0001 011X b

External PCI Devices

IDSEL # PIRQREQ/GNT #DEVICENB Internal VGA

LAN

CARD BUS

N/A

AD19

AD20 2

N/A

1

A

C/D

I2C / SMBUS ADDRESSING

DEVICE HEX ADDRESSDDR SO-DIMM 0

CLOCK GENERATOR (EXT.)

A0

D2

1 0 1 0 0 0 1 X

1 1 0 1 0 0 1 X

+5V 5V power rail OFFONON

A

D

Mini-PCI AD18 3

5 in 1 AD20 2 B

A1394 0AD16

ALC250 0000 000X b

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

HD#63HD#62HD#61

HD#59HD#60

HD#58HD#57

H_IERR#

HD#56

HD#52

HD#55HD#54HD#53

HD#51

HD#48

HD#45

HD#49

HD#47HD#46

HD#50

H_ADS#

HD#44

H_BREQ0#

HD#43

HD#38

HD#33

HD#39

HD#36

HD#40

HD#42HD#41

HD#37

HD#26

HD#30

HD#32

HD#28

HD#35

HD#31

HD#34

HD#27

HD#29

HD#25

HD#18

HD#24

HD#20HD#19

HD#21HD#22HD#23

HD#13

HD#11

HD#15HD#16

HD#14

HD#7HD#8

HD#17

HD#9

HD#12

HD#10

HD#6

HD#0

HD#4

HD#1

HD#3HD#2

HD#5

H_REQ#[0..4]

H_REQ#4H_REQ#3H_REQ#2

H_REQ#0H_REQ#1

HA#11

HD#[0..63]

HA#27

HA#14

HA#12

HA#20

HA#17

HA#30

HA#23HA#22

HA#9

HA#21

HA#26

HA#3

HA#16

HA#6

HA#24

HA#29

HA#31

HA#28

HA#18

HA#7

HA#5

HA#25

HA#15

HA#4

HA#13

HA#19

HA#8

HA#10

HA#[3..31]

CLK_EXT_CPUCLK_EXT_CPU#

HD#[0..63] 7

HA#[3..31]7

H_REQ#[0..4]7

H_ADS#7

H_BREQ0#7

H_BNR#7

H_HIT#7H_HITM#7

H_BPRI#7

H_LOCK#7

H_DEFER#7

CLK_EXT_CPU17CLK_EXT_CPU#17

H_BOOTSELECT 44

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2CPU(1/2)

B

4 47Thursday, April 08, 2004

Compal Electronics, Inc.

R_C

Pop: NorthwoodDepop: Prescott

H_BR0# PU R :Intel 220 OhmATi RC300 51 OhmATi RS250 56 Ohm

R1 56_0402_5%1 2

R2 51_0402_5%1 2

R5@0_0402_5%

@

1 2

Northwood-MTPrescott-MT

HOSTADDR

CONTROL

CLK

CONTROL GND POWER

HOSTADDR

POWER

JP1A

AMP_1473129-1

A#3K2A#4K4A#5L6A#6K1A#7L3A#8M6A#9L2A#10M3A#11M4A#12N1A#13M1A#14N2A#15N4A#16N5A#17T1A#18R2A#19P3A#20P4A#21R3A#22T2A#23U1A#24P6A#25U3A#26T4A#27V2A#28R6A#29W1A#30T5A#31U4A#32V3A#33W2A#34Y1A#35AB1

REQ#0J1REQ#1K5REQ#2J4REQ#3J3REQ#4H3ADS#G1

AP#0AC1AP#1V5BINIT#AA3IERR#AC3

BNR#G2BPRI#D2BR0#H6

LOCK#G4

DEFER#E2HITM#E3HIT#F3

D#0 B21D#1 B22D#2 A23D#3 A25D#4 C21D#5 D22D#6 B24D#7 C23D#8 C24D#9 B25

D#10 G22D#11 H21D#12 C26D#13 D23D#14 J21D#15 D25D#16 H22D#17 E24D#18 G23D#19 F23D#20 F24D#21 E25D#22 F26D#23 D26D#24 L21D#25 G26D#26 H24D#27 M21D#28 L22D#29 J24D#30 K23D#31 H25D#32 M23D#33 N22D#34 P21D#35 M24D#36 N23D#37 M26D#38 N26D#39 N25D#40 R21D#41 P24D#42 R25D#43 R24D#44 T26D#45 T25D#46 T22D#47 T23D#48 U26D#49 U24D#50 U23D#51 V25D#52 U21D#53 V22D#54 V24D#55 W26D#56 Y26D#57 W25D#58 Y23D#59 Y24D#60 Y21D#61 AA25D#62 AA22D#63 AA24

VC

C_0

A10

VC

C_1

A12

VC

C_2

A14

VC

C_3

A16

VC

C_4

A18

VC

C_5

A20

VC

C_6

A8

VC

C_7

AA

10V

CC

_8A

A12

VC

C_9

AA

14V

CC

_10

AA

16V

CC

_11

AA

18V

CC

_12

AA

8V

CC

_13

AB

11V

CC

_14

AB

13V

CC

_15

AB

15V

CC

_16

AB

17V

CC

_17

AB

19V

CC

_18

AB

7V

CC

_19

AB

9V

CC

_20

AC

10V

CC

_21

AC

12V

CC

_22

AC

14V

CC

_23

AC

16V

CC

_24

AC

18V

CC

_25

AC

8V

CC

_26

AD

11V

CC

_27

AD

13V

CC

_28

AD

15V

CC

_29

AD

17V

CC

_30

AD

19V

CC

_31

AD

7V

CC

_32

AD

9V

CC

_33

AE

10V

CC

_34

AE

12V

CC

_35

AE

14V

CC

_36

AE

16V

CC

_37

AE

18V

CC

_38

AE

20V

CC

_39

AE

6V

CC

_40

AE

8V

CC

_41

AF1

1V

CC

_42

AF1

3V

CC

_43

AF1

5V

CC

_44

AF1

7V

CC

_45

AF1

9V

CC

_46

AF2

VC

C_4

7A

F21

VC

C_4

8A

F5V

CC

_49

AF7

VC

C_5

0A

F9V

CC

_51

B11

VC

C_5

2B

13V

CC

_53

B15

VC

C_5

4B

17V

CC

_55

B19

VC

C_5

6B

7V

CC

_57

B9

VC

C_5

8C

10V

CC

_59

C12

VC

C_6

1C

14V

CC

_62

C16

VC

C_6

3C

18V

CC

_64

C20

VC

C_6

5C

8V

CC

_66

D11

VC

C_6

7D

13V

CC

_68

D15

VC

C_6

9D

17V

CC

_70

D19

VC

C_7

1D

7V

CC

_72

D9

VC

C_7

4E

12V

CC

_75

E14

VC

C_7

6E

16V

CC

_77

E18

VC

C_7

8E

20V

CC

_79

E8

VC

C_8

0F1

1

VS

S_0

H1

VS

S_1

H4

VS

S_2

H23

VS

S_3

H26

VS

S_4

A11

VS

S_5

A13

VS

S_6

A15

VS

S_7

A17

VS

S_8

A19

VS

S_9

A21

VS

S_1

0A

24V

SS

_11

A26

VS

S_1

2A

3V

SS

_13

A9

VS

S_1

4A

A1

VS

S_1

5A

A11

VS

S_1

6A

A13

VS

S_1

7A

A15

VS

S_1

8A

A17

VS

S_1

9A

A19

VS

S_2

0A

A23

VS

S_2

1A

A26

VS

S_2

2A

A4

VS

S_2

3A

A7

VS

S_2

4A

A9

VS

S_2

5A

B10

VS

S_2

6A

B12

VS

S_2

7A

B14

VS

S_2

8A

B16

VS

S_2

9A

B18

VS

S_3

0A

B20

VS

S_3

1A

B21

VS

S_3

2A

B24

VS

S_3

3A

B3

VS

S_3

4A

B6

VS

S_3

5A

B8

VS

S_3

6A

C11

VS

S_3

7A

C13

VS

S_3

8A

C15

VS

S_3

9A

C17

VS

S_4

0A

C19

VS

S_4

1A

C2

VS

S_4

2A

C22

VS

S_4

3A

C25

VS

S_4

4A

C5

VS

S_4

5A

C7

VS

S_4

6A

C9

BO

OTS

ELE

CT

AD

1

VS

S_4

7A

D10

VS

S_4

8A

D12

VS

S_4

9A

D14

VS

S_5

0A

D16

VS

S_5

1A

D18

VS

S_5

2A

D21

VS

S_5

3A

D23

VS

S_5

4A

D4

VS

S_5

5A

D8

BCLK0AF22BCLK1AF23

VC

C_8

1F1

3V

CC

_82

F15

VC

C_8

3F1

7V

CC

_84

F19

VC

C_8

5F9

VC

C_7

3E

10

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

+3VS_THMSEN

H_THERMDA

H_THERMDC

H_FERR#

H_THERMTRIP#

H_PWRGD

+GTLVREF1

+VCCVIDLB

+VCCA

VCCSENSE

ITP_BPM#4

CP

U_V

ID3

H_THERMTRIP#

VSSSENSE

H_THERMDC

H_PROCHOT#

CP

U_V

ID4

ITP_BPM#3ITP_BPM#2

CPU_GHI#

COMP0

H_DPSLPR#

VSSAH_CPUSLP#

ITP_BPM#0

H_SKTOCC#

+VCCIOPLL

COMP1

CP

U_V

ID1

H_THERMDA

ITP_BPM#5

ITP_BPM#1

H_RESET#

H_INTR

H_NMI

H_CPUSLP#

H_STPCLK#

H_IGNNE#

H_A20M#

H_SMI#

H_INIT#

H_INIT#

H_INTRH_NMI

H_PWRGD

H_IGNNE#

H_A20M#

H_STPCLK#

H_FERR#

H_RESET#

H_SMI#

GND

ITP_TMS

ITP_TCK

ITP_TRST#

ITP_TDI

CP

U_V

ID0

CP

U_V

ID2

CP

U_V

ID5

+GTLVREF1

H_DPSLPR#

H_RS#07

H_TRDY#7

H_DBSY#7H_DRDY#7

BSEL012,17

H_A20M#19

H_SMI#19H_PWRGD19

H_STPCLK#19

H_INTR19H_NMI19H_INIT#19

H_DSTBN#0 7

H_DBI#0 7

EC_SMC230,33

EC_SMD230,33

H_ADSTB#1 7H_ADSTB#0 7

H_RS#17H_RS#27

H_DBI#1 7H_DBI#2 7H_DBI#3 7

CPU_VID044CPU_VID144CPU_VID244CPU_VID344CPU_VID444CPU_VID544

BSEL112,17

CPU_GHI# 20

H_THERMTRIP#6

H_RESET#7

H_FERR#19

H_CPUSLP# 19

VCCSENSE44

H_DSTBN#1 7

H_DSTBP#1 7H_DSTBP#0 7

VSSSENSE44

H_DSTBN#3 7H_DSTBN#2 7

H_DSTBP#3 7

H_PROCHOT# 43

H_DSTBP#2 7

H_IGNNE#19

H_VID_PWRGD 35

PM_STPCPU#17,19,44

+CPU_CORE

+CPU_VID

+CPU_VID

+3VS

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+3VS

+CPU_VID+3VS

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

CPU(2/2)B

5 47Thursday, April 08, 2004

CPU Temperature Sensor

for mobile CPU

Compal Electronics, Inc.

width= 10mil

10mil10mil

25mil

25mil

51.1 Ohm for Northwood,61.9 Ohm for Prescott

Place within 1.5" from CPU

GTL Reference Voltage

15mil

1. < 1.5" from the CPU Ball.2. 220P cap. has to be closed to the ball as possible.3. Intel: 0.63VCC. ATi: 0.66VCC.

R_GPop: Northwood Imp: 50 OhmDepop: Prescott Imp:60 Ohm

R25 ->Pop: PrescottDepop: Northwood

Pop: PrescottDepop: Northwood

Intel 852GME RDDP 56Ohm.ATi RC300 51OhmATi RS250 56 Ohm

NC: W/O ITP

R32 51_0402_5%1 2

R17@22_0402_5%

1 2

C10 180P_0402_50V8J12

C4 180P_0402_50V8J12

R29 51_0402_5%1 2

R1251.1_0603_1%

12

R864.7K_0402_5%

12

RP1

1K_1206_8P4R_5%

1 82 73 64 5

RP2

10K_1206_8P4R_5%

1 82 73 64 5 R38

680_0402_5%12

L2

LQG21F4R7N00_0805

1 2

R41 10K_0402_5%1 2

R36 61.9_0603_1%1 2

C11 180P_0402_50V8J12

R39

200_0402_5%

1 2

R13 300_0402_1%1 2

R27 56_0402_5%1 2

R15 51_0402_5%1 2

R100_0402_5%

12

R35 0_0603_5%1 2

Q3MMBT3904_SOT23

2

31

C5 180P_0402_50V8J12

R25 56_0402_5%1 2

R33 51_0402_5%1 2

R20 56_0402_5%1 2

Northwood-MTPrescott-MT

GROUNDCONTROL

LEGACY

MISC

THERMAL

MISC

ITP

MISC

ITPCLK GROUND MISC

MISC

DATA

ADDR

DATA

ITP

REF

JP1B

AMP_1473129-1

RS#0F1RS#1G5RS#2F4RSP#AB2TRDY#J6

A20M#C6FERR#B6IGNNE#B2SMI#B5PWRGOODAB23STPCLK#Y4

TESTHI12 AD25

LINT0D1LINT1E5INIT#W5RESET#AB25

DRDY#H2DBSY#H5

THERMDCC4THERMDAB3

TDIC1TCKD4

TDOD5TMSF7TRST#E6

COMP1P1COMP0L24

DP#0 J26DP#1 K25DP#2 K26DP#3 L25

VS

S_5

7A

E11

VS

S_5

8A

E13

VS

S_5

9A

E15

VS

S_6

0A

E17

VS

S_6

1A

E19

VS

S_6

2A

E22

VS

S_6

3A

E24

OPTIMIZED/COMPAT# AE26

VS

S_6

5A

E7

VS

S_6

6A

E9

VS

S_6

7A

F1V

SS

_68

AF1

0V

SS

_69

AF1

2V

SS

_70

AF1

4V

SS

_71

AF1

6V

SS

_72

AF1

8V

SS

_73

AF2

0

SK

TOC

C#

AF2

6

VS

S_7

5A

F6V

SS

_76

AF8

VS

S_7

7B

10V

SS

_78

B12

VS

S_7

9B

14V

SS

_80

B16

VS

S_8

1B

18V

SS

_82

B20

VS

S_8

3B

23V

SS

_84

B26

VS

S_8

5B

4V

SS

_86

B8

VS

S_8

7C

11V

SS

_88

C13

VS

S_8

9C

15V

SS

_90

C17

VS

S_9

1C

19V

SS

_92

C2

VS

S_9

3C

22V

SS

_94

C25

VS

S_9

5C

5V

SS

_96

C7

VS

S_9

7C

9V

SS

_98

D10

VS

S_9

9D

12V

SS

_100

D14

VS

S_1

01D

16V

SS

_102

D18

VS

S_1

03D

20V

SS

_104

D21

VS

S_1

05D

24V

SS

_106

D3

VS

S_1

07D

6V

SS

_108

D8

VS

S_1

09E

1V

SS

_110

E11

VS

S_1

11E

13V

SS

_112

E15

VS

S_1

13E

17V

SS

_114

E19

VS

S_1

15E

23V

SS

_116

E26

VS

S_1

17E

4V

SS

_118

E7

VS

S_1

19E

9V

SS

_120

F10

VS

S_1

21F1

2V

SS

_122

F14

VS

S_1

23F1

6V

SS

_124

F18

VS

S_1

25F2

VS

S_1

26F2

2V

SS

_127

F25

VS

S_1

28F5

VID

0A

E5

VID

1A

E4

VID

2A

E3

VID

3A

E2

VID

4A

E1

GTLREF0 AA21GTLREF1 AA6GTLREF2 F20GTLREF3 F6

NC1 A22NC2 A7

TESTHI0 AD24TESTHI1 AA2TESTHI2 AC21TESTHI3 AC20TESTHI4 AC24TESTHI5 AC23TESTHI6 AA20TESTHI7 AB22TESTHI8 U6TESTHI9 W4

TESTHI10 Y3TESTHI11 A6

VS

S_1

29F8

VS

S_1

30G

21V

SS

_131

G24

VS

S_1

32G

3V

SS

_133

G6

VS

S_1

34J2

VS

S_1

35J2

2V

SS

_136

J25

VS

S_1

37J5

VS

S_1

38K

21V

SS

_139

K24

VS

S_1

40K

3V

SS

_141

K6

VS

S_1

42L1

VS

S_1

43L2

3V

SS

_144

L26

VS

S_1

45L4

VS

S_1

46M

2V

SS

_147

M22

VS

S_1

48M

25V

SS

_149

M5

VS

S_1

50N

21V

SS

_151

N24

VS

S_1

52N

3V

SS

_153

N6

VS

S_1

54P

2V

SS

_155

P22

VS

S_1

56P

25V

SS

_157

P5

VS

S_1

58R

1V

SS

_159

R23

VS

S_1

60R

26V

SS

_161

R4

VS

S_1

62T2

1V

SS

_163

T24

VS

S_1

64T3

VS

S_1

65T6

VS

S_1

66U

2V

SS

_167

U22

VS

S_1

68U

25V

SS

_169

U5

VS

S_1

70V

1V

SS

_171

V23

VS

S_1

72V

26V

SS

_173

V4

VS

S_1

74W

21V

SS

_175

W24

VS

S_1

76W

3V

SS

_177

W6

VS

S_1

78Y

2V

SS

_179

Y22

VS

S_1

80Y

25V

SS

_181

Y5

BSEL0AD6BSEL1AD5

BPM#0AC6BPM#1AB5BPM#2AC4BPM#3Y6BPM#4AA5BPM#5AB4

DSTBN#0 E22DSTBN#1 K22DSTBN#2 R22DSTBN#3 W22

DSTBP#0 F21DSTBP#1 J23DSTBP#2 P23DSTBP#3 W23

ITP_CLK0AC26ITP_CLK1AD26

ADSTB#0 L5ADSTB#1 R5

DBI#0 E21DBI#1 G25DBI#2 P26DBI#3 V21

DBR# AE25

VCCIOPLLAD20

VCCSENSEA5

VCCAAE23

VC

CV

IDA

F4

THERMTRIP#A2

PROCHOT# C3MCERR# V6

SLP# AB26VSSAAD22

VSSSENSEA4

VID

PW

RG

DA

D2

VID

5A

D3

NC5 AE21NC4 AF24NC3 AF25

VCCVIDLBAF3

R19 56_0402_5%1 2

R18 @0_0402_5%1 2

C31U_0603_10V6K

1

2

R93

4.7K_0402_5%

1 2

R24 56_0402_5%1 2

R11 56_0402_1%1 2

+C12

33U_D2_8M_R35

1

2

R28 51_0402_5%1 2

R34 51_0402_5%1 2

R14 56_0402_1%1 2

C6 180P_0402_50V8J12

R4210K_0402_5%

12

R23 56_0402_5%1 2

C2220P_0402_50V7K

1

2

R22 56_0402_5%1 2

L1LQG21F4R7N00_0805

1 2

C7 180P_0402_50V8J12

R26 300_0402_5%1 2

C130.1U_0402_10V6K

1

2

C140.1U_0402_10V6K

1

2

R30 51_0402_5%1 2

Q4MMBT3904_SOT23

2

31

C8 180P_0402_50V8J12

R31 51_0402_5%1 2

R37 61.9_0603_1%1 2

C1@10P_0402_50V8J

12

C15@2200P_0603_50V7K

1

2

R1686.6_0603_1%

12

C9 180P_0402_50V8J12

R40 10K_0402_5%1 2

U1

ADM1032ARM_RM8

VDD1 1

ALERT# 6

THERM# 4

GND 5

D+2

D-3

SCLK8

SDATA7

R21 56_0402_5%1 2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

H_THERMTRIP#H_THERMTRIP#5 MAINPWON 38,39,41

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

CPU DecouplingB

6 47Thursday, April 08, 2004

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Layout note :Place close to CPU power andground pin as possible(

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

H_DEFER#

HA#29

COMP_N

HA#6

HA#13

COMP_P

H_BREQ0#

H_TRDY#

HA#23

H_DRDY#

HA#30

HA#7

HA#17

HA#14

HA#24

HA#31

H_DBSY#

H_REQ#0

H_RESET#

HA#8

H_DSTBP#3

HD#8

HD#47

HD#32

HD#14

H_DSTBP#2

HD#17

HD#36

HD#20

HD#15

HD#9

HD#23

H_DSTBN#2

HD#57

H_DSTBN#3

HD#16

HD#7

HD#10

HD#53

H_DSTBP#1

HD#56

HD#19

HD#43

HD#33

HD#35

HD#11

HD#55

H_DBI#0

HD#3

H_DSTBN#1

HD#0

HD#[0..63]

HD#50

HD#28

HD#62

HD#46

HD#18

H_DSTBP#0

HD#49

HD#5

HD#52

HD#60

HA#18

HD#25

HD#51

HD#45

HD#54

HD#6

HD#24

HD#12

HD#31

HD#13

HD#39

HD#48

HD#30

HD#27

HD#61

HA#15

HD#59

HD#26

HD#4

HD#2

HD#38

HD#63H_DBI#3

H_DSTBN#0

HD#40

HD#58

HD#42

H_DBI#2

HD#1

HD#21

HD#44

HD#37

HD#22

H_DBI#1

HD#34

HD#29

HD#41

HA#25

H_REQ#[0..4]

H_ADSTB#0

H_RS#2

H_REQ#1

H_ADSTB#1

HA#9

HA#19

HA#16

HA#26

HA#3

H_RS#1

H_REQ#2

HA#10

H_BNR#

H_HIT#

CPVSS

HA#20

CPVDD

HA#27

HA#4

+NB_GTLREF

H_REQ#3

H_RS#0

HA#11

H_HITM#

HA#21

H_LOCK#

H_BPRI#

HA#28

HA#5

H_REQ#4

HA#12

HA#[3..31]

HA#22

H_ADS#

NB_RST#_R

SUS_STAT#_R

SUS_STAT#_RNB_RST#_R

HD#[0..63] 4

HA#[3..31] 4

H_REQ#[0..4] 4

H_DSTBP#0 5

H_DSTBN#3 5

H_DSTBN#0 5

H_DSTBP#3 5

H_DSTBP#2 5H_DSTBN#2 5

H_DSTBP#1 5H_DSTBN#1 5

H_TRDY#5

H_RS#15

H_DEFER#4

H_HITM#4H_HIT#4

H_ADSTB#15

H_DRDY#5

H_ADSTB#05

H_RS#25

H_LOCK#4

H_DBSY#5

H_BPRI#4H_BNR#4

H_RS#05

H_RESET#5

H_BREQ0#4

H_DBI#3 5

H_DBI#0 5

H_DBI#2 5

H_DBI#1 5

H_ADS#4

NB_PWRGD22

SUS_STAT#20

NB_RST#19,23,32,33

+CPU_CORE

+1.8VS

+CPU_CORE

+1.8VS+2.5V

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

ATi RC300ML-HOST(1/5)B

7 47Thursday, April 08, 2004

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

L Note: PLACE CLOSE TO RC300M,USE 10/10 WIDTH/SPACE

PLACE CLOSE TO U27 BallW28, USE 20/20WIDTH/SPACE

R712

86.6_0603_1%

12

C6550.1U_0402_10V6K

12

C657

1U_0603_10V6K

1

2

R801

270K_0402_5%

1 2

R803330K_0402_5%

12

L40

HB-1M2012-121JT03_08051 2

R713

4.7K_0402_5%

12

PEN

TIU

MIV

AD

DR

. GR

OU

P 1

AD

DR

. GR

OU

P 0

CO

NTR

OL

MIS

C.

DAT

A G

RO

UP

0D

ATA

GR

OU

P 1

DAT

A G

RO

UP

2D

ATA

GR

OU

P 3

AGTL

+ I/F

PA

RT

1 O

F 6

U51A

CHS-216IGP9050A21_BGA718

CPU_ADS#L27CPU_BNR#K25CPU_BPRI#H26

CPU_D0# L30CPU_D1# K29CPU_D2# J29CPU_D3# H28CPU_D4# K28CPU_D5# K30CPU_D6# H29CPU_D7# J28CPU_D8# F28CPU_D9# H30

CPU_D10# E30CPU_D11# D29CPU_D12# G28CPU_D13# E29CPU_D14# D30CPU_D15# F29

CPU_D16# B26CPU_D17# C30CPU_D18# A27CPU_D19# B29CPU_D20# C28CPU_D21# C29CPU_D22# B28CPU_D23# D28CPU_D24# D26CPU_D25# B27CPU_D26# C26CPU_D27# E25CPU_D28# E26CPU_D29# A26CPU_D30# B25CPU_D31# C25

CPU_D32# F24CPU_D33# D24CPU_D34# E23CPU_D35# E24CPU_D36# F23CPU_D37# C24CPU_D38# B24CPU_D39# A24CPU_D40# F21CPU_D41# A23CPU_D42# B23CPU_D43# C22CPU_D44# B22CPU_D45# C21CPU_D46# E21CPU_D47# D22

CPU_D48# B21CPU_D49# F20CPU_D50# A21CPU_D51# C20CPU_D52# E20CPU_D53# D20

CPU_A3#M28CPU_A4#P25

CPU_D54# A20CPU_D55# D19CPU_D56# C18CPU_D57# B20CPU_D58# E18CPU_D59# B19CPU_D60# D18CPU_D61# B18CPU_D62# C17CPU_D63# A18

CPU_ADSTB0#R27

CPU_ADSTB1#T29

CPU_BR0#F25CPU_DBSY#G27

CPU_DEFER#J27CPU_DRDY#L26

CPU_LOCK#K26

CPU_TRDY#F26

CPU_REQ0#M29CPU_REQ1#N25CPU_REQ2#R26CPU_REQ3#L28CPU_REQ4#L29

CPU_HIT#J26CPU_HITM#H25

CPU_RS0#J25CPU_RS1#G26CPU_RS2#G25

CPU_DSTBN3# E19

CPU_DSTBN2# E22

CPU_DSTBN1# D27

CPU_DSTBN0# G30

CPU_DSTBP3# F18

CPU_DSTBP2# F22

CPU_DSTBP1# E27

CPU_DSTBP0# G29

CPU_DBI3# F19

CPU_DBI2# D23

CPU_DBI1# A28

CPU_DBI0# E28

CPU_CPURSET#A17

CPU_COMP_PW29

CPU_COMP_NV28

CPVSSJ23

CPU_VREFW28

THERMALDIODE_NY29THERMALDIODE_PY28

TESTMODEB17

CPVDDH23

SYSRESET#AG5POWERGOODC7

CPU_A5#M25CPU_A6#N29CPU_A7#N30CPU_A8#M26CPU_A9#N28CPU_A10#P29CPU_A11#P26CPU_A12#R29CPU_A13#P30CPU_A14#P28CPU_A15#N26CPU_A16#N27

CPU_A17#U30CPU_A18#T30CPU_A19#R28CPU_A20#R25CPU_A21#U25CPU_A22#T28CPU_A23#V29CPU_A24#T26CPU_A25#U29CPU_A26#U26CPU_A27#V26CPU_A28#T25CPU_A29#V25CPU_A30#U27CPU_A31#U28

SUS_STAT#AH5CPU_RSETA9

D71

RB751V_SOD323

21

C658

220P_0402_50V8K

1

2

R711 49.9_0402_1%1 2

R80027K_0402_5%

12

R710 24.9_0603_1%1 2

R716

51.1_0603_1%

12

C656

2.2U_0805_10V4Z1 2

R80227K_0402_5%

12

R709

330_0402_5%1 2

D70

RB751V_SOD323

21

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

AGP_SBA6

AGP_SBA7

AGP8X_DET#

AGP8X_DET#

AGP_SBA6AGP_SBA7

LVDS_SSOUT

AGPREF_4X

A_AD13

A_AD15

A_AD4

A_AD17

A_AD20

A_AD30

A_PAR

A_AD[0..31]

A_AD3

A_AD7

A_AD11

A_AD23

A_AD26

A_CBE#0

A_AD28

A_AD2

A_ACAT#

A_AD8

A_AD19

A_AD21

A_END#

A_AD25

A_AD31

A_CBE#1

A_CBE#[0..3]

A_AD6

A_DEVSEL#

A_AD1

A_AD10

A_SBGNT#

A_AD16

A_AD14

A_AD27

A_AD29

A_CBE#3

A_STROBE#

A_SBREQ#

A_AD18

A_AD9

A_AD0

A_AD5

A_AD12

A_AD22

A_OFF#

A_AD24

A_CBE#2

AGP_COMP

LVDS_SSIN

+3VS_SSVDD

AGPREF_4X EDID_CLK 18EDID_DAT 18

A_AD[0..31]12,19

A_CBE#[0..3]19

A_DEVSEL#19

A_SBGNT#19

A_OFF#19

A_END#19A_ACAT#19

A_PAR12,19A_STROBE#19

PCI_PIRQA#19,24,27

ENVDD 18ENBK# 33

A_SBREQ#19

AGP_STP# 20AGP_BUSY# 20

+3VS

+1.5VS+1.5VS

+3VS

+3VS

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

ATi RC300ML-A-LINK/AGP(2/5)Custom

8 47Thursday, April 08, 2004

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Ra

S1

S0

LVDS SPREAD SPECTRUM

Note: PLACE CLOSE TO U2 (NB RC300M)L

Close to Pin J6

R658

@0_0402_5%

12

PART 3 OF 6

PCI B

us 0

/ A-

Link

I/F

PCI B

US

1 / A

GP

Bus

(GPI

O ,

TMD

S , Z

VPor

t)

U51C

CHS-216IGP9050A21_BGA718

ALINK_AD0AK5ALINK_AD1AJ5ALINK_AD2AJ4ALINK_AD3AH4ALINK_AD4AJ3ALINK_AD5AJ2ALINK_AD6AH2ALINK_AD7AH1ALINK_AD8AG2ALINK_AD9AG1ALINK_AD10AG3ALINK_AD11AF3ALINK_AD12AF1ALINK_AD13AF2ALINK_AD14AF4ALINK_AD15AE3ALINK_AD16AE4ALINK_AD17AE5ALINK_AD18AE6ALINK_AD19AC2ALINK_AD20AC4ALINK_AD21AB3ALINK_AD22AB2ALINK_AD23AB5ALINK_AD24AB6ALINK_AD25AA2ALINK_AD26AA4ALINK_AD27AA5ALINK_AD28AA6ALINK_AD29Y3ALINK_AD30Y5ALINK_AD31Y6

ALINK_CBE#0AG4ALINK_CBE#1AE2ALINK_CBE#2AC3ALINK_CBE#3AA3

PCI_PAR/ALINK_NCAD5PCI_FRAME#/ALINK_STROBE#AC6PCI_IRDY#/ALINK_ACAT#AC5PCI_TRDY#/ALINK_END#AD2INTA#W4ALINK_DEVSEL#AD3PCI_STOP#/ALINK_OFF#AD6

ALINK_SBREQ#W5ALINK_SBGNT#W6

PCI_REQ#0/ALINK_NCV5PCI_GNT#0/ALINK_NCV6

AGP_AD0/TMD2_HSYNC Y2AGP_AD1/TMD2_VSYNC W3

AGP_AD2/TMD2_D1 W2AGP_AD3/TMD2_D0 V3AGP_AD4/TMD2_D3 V2AGP_AD5/TMD2_D2 V1AGP_AD6/TMD2_D5 U1AGP_AD7/TMD2_D4 U3AGP_AD8/TMD2_D6 T2AGP_AD9/TMD2_D9 R2

AGP_AD10/TMD2_D8 P3AGP_AD11/TMD2_D11 P2AGP_AD12/TMD2_D10 N3

AGP_AD13 N2AGP_AD14 M3AGP_AD15 M2

AGP_AD16/TMD1_VSYNC L1AGP_AD17/TMD1_HSYNC L2

AGP_AD18/TMD1_DE K3AGP_AD19/TMD1_D0 K2AGP_AD20/TMD1_D1 J3AGP_AD21/TMD1_D2 J2AGP_AD22/TMD1_D3 J1AGP_AD23/TMD1_D4 H3AGP_AD24/TMD1_D7 F3AGP_AD25/TMD1_D6 G2AGP_AD26/TMD1_D9 F2AGP_AD27/TMD1_D8 F1

AGP_AD28/TMD1_D11 E2AGP_AD29/TMD1_D10 E1

AGP_AD30/TMDS_HPD D2AGP_AD31 D1

AGP2_SBSTB/AGP3_SBSTBF/NC/LVDS_BLON E5AGP2_SBSTB#/AGP3_SBSTBS/NC/ENA_BL E6

AGP2_ADSTB0/AGP3_ADSTBF0/TMD2_CLK# T3AGP2_ADSTB0#/AGP3_ADSTBS0/TMD2_CLK U2AGP2_ADSTB1/AGP3_ADSTBF1/TMD1_CLK# G3AGP2_ADSTB1#/AGP3_ADSTBS1/TMD1_CLK H2

AGP2_CBE#0/AGP3_CBE0/TMD2_D7 R3AGP2_CBE#1/AGP3_CBE1/TMD2_DE M1

AGP2_CBE#2/AGP3_CBE2 L3AGP2_CBE#3/AGP3_CBE3/TMD1_D5 H1

AGP2_DEVSEL#/AGP3_DEVSEL/GPIO9/I2C_DATA R5AGP2_FRAME#/AGP3_FRAME/TMDS_DVI_DATA P6

AGP2_IRDY#/AGP3_IRDY/GPIO8/I2C_CLK P5AGP2_TRDY#/AGP3_TRDY/TMDS_DVI_CLK R6

AGP2_WBF#/AGP3_WBF N5

AGP2_SBA0/AGP3_SBA#0/GPIO0/VDDC_CNTL0 C3AGP2_SBA1/AGP3_SBA#1/GPIO1/VDDC_CNTL1 C2

AGP2_SBA3/AGP3_SBA#3/GPIO3/LVDS_DIGON E4

AGP2_SBA5/AGP3_SBA#5/GPIO5/AGP_BUSY# F5AGP2_SBA6/AGP3_SBA#6/GPIO6/LVDS_SSOUT G6

AGP2_SBA7/AGP3_SBA#7/GPIO7/LVDS_SSIN G5

AGP_ST0 L6AGP_ST1 M6AGP_ST2 L5

AGP8X_DET#M5

AGP_VREF/TMDS_VREFJ6

AGP2_REQ#/AGP3_REQK6AGP2_GNT#/AGP3_GNTK5

AGP2_SBA2/AGP3_SBA#2/GPIO2/LVDS_BLON# D4

AGP2_SBA4/AGP3_SBA#4/GPIO4/STP_AGP# F6

AGP2_STOP#/AGP3_STOP/GPIO10/DDC_DATA T6AGP_PAR T5

AGP2_RBF#/AGP3_RBF N6

AGP2_PIPE#/AGP3_DBI_HI C1AGP2_NC/AGP3_DBI_LO D3

AGP_COMPJ5

R653

@0_0402_5%

12

R6598.2K_0402_5%1 2

R714

@0_0402_5%

12

C662

@10P_0402_25V8K

1

2

C663

0.1U_0402_10V6K

1 2

R663

@47K_0402

12

R6611K_0603_1%

12

R654

@0_0402_5%

12

R6621K_0603_1%

12

C659

@10U_0805_6.3V6M

1

2

L41@BLM21P300S_0805

1 2

C660

@0.1U_0402_10V6K

1

2

R656@0_0402_5%

12

R651

@0_0402_5%

12

R657@0_0402_5%

12

R715

@0_0402_5%

12

R652

@0_0402_5%

12

U52

@SM561BS_SO8

Xin/CLK1

Xout 8S07

S16

VD

D2

SSCLK 4

SSCC 5

VS

S3R655

@0_0402_5%

12

R660

@52.3_0603_1%

1 2

C661

@10P_0402_25V8K

1

2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

MPVDD

DDR_SMA[0..13]

DDR_DQS[0..7]

DDR_DQ[0..63]

DDR_DM[0..7]

DDR_DQ32DDR_DQ33DDR_DQ34DDR_DQ35DDR_DQ36DDR_DQ37DDR_DQ38DDR_DQ39DDR_DQ40DDR_DQ41

DDR_DQ50

DDR_DQ45

DDR_DQ47

DDR_DQ43

DDR_DQ49

DDR_DQ46

DDR_DQ48

DDR_DQ51

DDR_DQ44

DDR_DQ42

DDR_DQ53

DDR_DQ55DDR_DQ56DDR_DQ57

DDR_DQ52

DDR_DQ59DDR_DQ60DDR_DQ61

DDR_DQ58

DDR_DQ54

DDR_DQ63DDR_DQ62

DDR_CLK1DDR_CLK1#

DDR_SCKE2DDR_SCKE3

DDR_SMA12

DDR_SMA10

DDR_SMA8

DDR_SMA11

DDR_SMA9

DDR_SMA13

MEN_COMP

DDR_SCS#3DDR_SCS#2

DDR_DQ0DDR_DQ1

MPVSS

DDR_DQ2DDR_DQ3DDR_DQ4

DDR_CLK4#

DDR_DQ5DDR_DQ6DDR_DQ7DDR_DQ8DDR_DQ9

DDR_SCKE1

DDR_DQ18

DDR_DQ13

DDR_DQ15

DDR_DQ11

DDR_DQ17

DDR_DQ14

DDR_DQ16

DDR_DQ19

DDR_DQ12

DDR_DQ10

DDR_DQ21

DDR_DQ23DDR_DQ24DDR_DQ25

DDR_DQ20

DDR_DQ27DDR_DQ28DDR_DQ29

DDR_DQ26

DDR_DQ22

DDR_DQ31DDR_DQ30

DDR_SMA4

DDR_SMA2

DDR_SMA0

DDR_SMA7DDR_SMA6DDR_SMA5

DDR_SMA3

DDR_SMA1

DDR_DM0

DDR_DM3DDR_DM2DDR_DM1

DDR_DM6

DDR_SCKE0

DDR_DM4

DDR_CLK3

DDR_DM5

DDR_SRAS#DDR_SCAS#

DDR_SWE#

DDR_DM7

DDR_CLK4

DDR_CLK3#

DDR_DQS0DDR_DQS1

DDR_DQS4

DDR_CLK0#

DDR_DQS6

DDR_DQS3

DDR_DQS7

DDR_DQS2

DDR_DQS5

DDR_CLK0

DDR_SCS#0DDR_SCS#1

+DDR_VREF

DDR_CLK014,15

DDR_CLK313

DDR_CLK1#14,15

DDR_CLK413

DDR_CLK3#13

DDR_CLK114,15

DDR_CLK4#13

DDR_CLK0#14,15

DDR_DQ[0..63] 13,14,16

DDR_DQS[0..7] 13,14,16

DDR_DM[0..7] 13,14,16

DDR_SCKE014,16DDR_SCKE115,16DDR_SCKE213,16DDR_SCKE313,16

DDR_SCS#014,16DDR_SCS#115,16DDR_SCS#213,16DDR_SCS#313,16

DDR_SRAS#13,14,15,16DDR_SCAS#13,14,15,16

DDR_SWE#13,14,15,16

DDR_SMA[0..13] 13,14,15,16

DDR_SBA013,14,15,16DDR_SBA113,14,15,16

+1.8VS

+2.5V

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

ATi RC300ML-DDR(3/5)B

9 47Thursday, April 08, 2004

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

C666

2.2U_0805_10V4Z

1 2

C665 0.47U_0603_16V7K1 2

C664 0.47U_0603_16V7K1 2

C6690.1U_0402_10V6K

1

2

L42HB-1M2012-121JT03_0805

1 2

C6680.1U_0402_10V6K

1

2

R664 49.9_0402_1%1 2

R6651K_0603_1%

MEM

I/F

PART 2 OF 6

U51B

CHS-216IGP9050A21_BGA718

MEM_DQ0 AG6MEM_DQ1 AJ7MEM_DQ2 AJ9MEM_DQ3 AJ10MEM_DQ4 AJ6MEM_DQ5 AH6MEM_DQ6 AH8MEM_DQ7 AH9MEM_DQ8 AE7MEM_DQ9 AE8

MEM_DQ10 AE12MEM_DQ11 AF12MEM_DQ12 AF7MEM_DQ13 AF8MEM_DQ14 AE11MEM_DQ15 AF11MEM_DQ16 AJ12MEM_DQ17 AH12MEM_DQ18 AH14MEM_DQ19 AH15MEM_DQ20 AH11MEM_DQ21 AJ13MEM_DQ22 AJ15MEM_DQ23 AJ16MEM_DQ24 AF18MEM_DQ25 AG20MEM_DQ26 AG21MEM_DQ27 AF22MEM_DQ28 AF19MEM_DQ29 AF20MEM_DQ30 AE22MEM_DQ31 AF23MEM_DQ32 AJ21MEM_DQ33 AJ22MEM_DQ34 AJ24MEM_DQ35 AK25MEM_DQ36 AH21MEM_DQ37 AH22MEM_DQ38 AH24MEM_DQ39 AJ25MEM_DQ40 AK26MEM_DQ41 AK27MEM_DQ42 AJ28MEM_DQ43 AH29MEM_DQ44 AH25MEM_DQ45 AJ26MEM_DQ46 AJ29MEM_DQ47 AH30MEM_DQ48 AF29MEM_DQ49 AE29MEM_DQ50 AB28MEM_DQ51 AA28MEM_DQ52 AE28MEM_DQ53 AD28MEM_DQ54 AC29MEM_DQ55 AB29MEM_DQ56 AC26MEM_DQ57 AB25MEM_DQ58 Y26MEM_DQ59 W26MEM_DQ60 AE26MEM_DQ61 AD26MEM_DQ62 AA26MEM_DQ63 Y27

MEM_DDRVREF AK20

MEM_A0AH19MEM_A1AJ17MEM_A2AK17MEM_A3AH16MEM_A4AK16MEM_A5AF17MEM_A6AE18MEM_A7AF16MEM_A8AE17MEM_A9AE16MEM_A10AJ20MEM_A11AG15MEM_A12AF15MEM_A13AE23MEM_A14AH20

MEM_DM0AH7MEM_DM1AF10MEM_DM2AJ14MEM_DM3AF21MEM_DM4AH23MEM_DM5AK28MEM_DM6AD29MEM_DM7AB26

MEM_RAS#AF24MEM_CAS#AF25

MEM_WE#AE24

MEM_CKE0AF13

MEM_DQS0AJ8MEM_DQS1AF9MEM_DQS2AH13MEM_DQS3AE21MEM_DQS4AJ23MEM_DQS5AJ27MEM_DQS6AC28MEM_DQS7AA25

MEM_CK0#AH10MEM_CK0AK10

MEM_CS#0AH26MEM_CS#1AH27MEM_CS#2AF26MEM_CS#3AG27

MPVDDAC18

MPVSSAD18

MEM_A15AE25

MEM_CKE1AE13

MEM_CK1AH18MEM_CK1#AJ19

MEM_CK2AG30MEM_CK2#AG29

MEM_CK3AK11MEM_CK3#AJ11

MEM_CK4AH17MEM_CK4#AJ18

MEM_CK5AF28MEM_CK5#AG28

MEM_CKE2AG14MEM_CKE3AF14

MEM_CAP1 AF6

MEM_CAP2 AA29

MEM_COMP AK19

R6661K_0603_1%

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

CRMA_1

LUMA_1

TV_CRMA

TV_COMPS

LVSSR

+1.8VS_AVDDQ

+3VS_VDDR

+1.8VS_AVDDDI

TV_CRMA

NB_RSET

CLK_EXT_NB#CLK_EXT_NB

+1.8VS_LPVDD

+1.8VS_LVDDR

LPVSS

CLK_EXT_AGP66

CLK_EXT_MEM66

+2.5VS_AVDD

CLK_EXT_AGP66

CLK_EXT_MEM66

+PLLVDD_18

TV_LUMA

TV_LUMA

TXCLK+ 18

TXOUT1- 18TXOUT1+ 18TXOUT2- 18TXOUT2+ 18

TXOUT0- 18TXOUT0+ 18

TXCLK- 18

TZCLK+ 18

TZOUT1- 18TZOUT1+ 18TZOUT2- 18TZOUT2+ 18

TZOUT0- 18TZOUT0+ 18

TZCLK- 18

CLK_EXT_AGP6617

CLK_EXT_NB#17CLK_EXT_NB17

CLK_EXT_MEM6617

REFCLK1_NB17

CRT_VSYNC18CRT_HSYNC18

CRT_B18CRT_G18CRT_R18

NB_DDC_DATA 18

NB_DDC_CLK 18

+1.8VS

+1.8VS

+3VS

+2.5VS

+1.8VS

+1.8VS

+1.8VS

+3VS

+3VS

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

ATi RC300ML-VEDIO(4/5)B

10 47Thursday, April 08, 2004

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

TV-OUT CONN.

R671

@10_0402_5%

12

C6710.1U_0402_10V6K

1

2

L46 10_0603_5%1 2

C681

@15P_0402_50V8J

1

2

R673

10K_0402_5%

1 2

C103 @33P_0402_50V8J1 2

L49

KC FBM-L11-201209-221LMAT_08051 2

R10175_0402_1%

12

C683

0.1U_0402_10V6K1

2

C67510U_0805_10V4Z

1

2

D1V-PORT-0603-220 M-V05_0603

21

C685

@15P_0402_50V8J

1

2

C104 @33P_0402_50V8J1 2

C682

0.1U_0402_10V6K

1

2

R10275_0402_1%

12

C674

0.1U_0402_10V6K

1

2

L45KC FBM-L11-201209-221LMAT_0805

1 2

L48

KC FBM-L11-201209-221LMAT_08051 2

L47KC FBM-L11-201209-221LMAT_0805

1 2

C110

100P_0402_25V8K

1

2

C679

0.1U_0402_10V6K1

2

R668 715 _0402_1%1 2

R669

56_0402_5%

12 R670 @75_0402_1%

1 2

C109

100P_0402_25V8K

1

2

L4 CHB2012U121_08051 2

L44

KC FBM-L11-201209-221LMAT_0805

12

L43

FBM-11-160808-121-T_0603

1 2

C684

10U_0805_10V4Z

1

2

C111

100P_0402_25V8K

1

2

R667

@10_0402_5%

12

L5 CHB2012U121_08051 2

C680

10U_0805_10V4Z

1

2

C677

0.1U_0402_10V6K

1

2

C670

0.1U_0402_10V6K

1

2

C678

0.1U_0402_10V6K

1

2

JP2

SUYIN_030008FR004T100ZL

11223344

R672 1K_0402_5%1 2

D2V-PORT-0603-220 M-V05_0603

21

C672

0.1U_0402_10V6K

1

2

PART 4 OF 6

CR

T

CLK. GEN.

SV

IDLV

DS

U51D

CHS-216IGP9050A21_BGA718

TXOUT_U0N D12TXOUT_U0P E12TXOUT_U1N F11TXOUT_U1P F12TXOUT_U2N D13TXOUT_U2P D14

TXCLK_UN E13TXCLK_UP F13

TXOUT_L0N E10TXOUT_L0P D10TXOUT_L1N B9TXOUT_L1P C9TXOUT_L2N D11TXOUT_L2P E11

TXCLK_LN B10TXCLK_LP C10

LVDDR_18 B12

LPVSS A11

LVDDR_18 C12

LPVDD_18 A12

LVSSR B11LVSSR C11

C_R E15

Y_G C15

COMP_B D15

DACSCL D6

DACSDA C6

CPUSTOP# D5

REDF14GREENF15BLUEE14DACHSYNCC8DACVSYNCD9

RSETC14

VDDR3H9

AVDDQA15

AVSSNB13

AVDD_25A14

AVDDDI_18B14

AVSSDIC13

AVSSQB15

PLLVDD_18H11

PLLVSSG11

VDDR3G9

XTALINA4XTALOUTB4

EXT_MEM_CLKA3

SYSCLK A8

SYSCLK# B8

AGPCLKINB3

HCLKIN#B5

ALINK_CLKD8

AGPCLKOUTB2

USBCLKD7REF27B7

SYS_FBCLKOUTB6

OSCC5

SYS_FBCLKOUT#A6

HCLKINA5

C673

0.1U_0402_10V6K

1

2

C112

100P_0402_25V8K

1

2

C676

0.1U_0402_10V6K

1

2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

+3VS

+CPU_CORE

+2.5V

+CPU_CORE

+1.8VS

+1.5VS

+3VS

+1.5VS

+1.5VS

+1.5VS

+3VS

+1.5VS +2.5V

+2.5V

+1.8VS

+1.5VS

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

ATi RC300ML-Power(5/5)B

11 47Thursday, April 08, 2004

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

ATI request

C694

0.1U_0402_10V6K

1

2

C710

0.1U_0402_10V6K

1

2

C761

0.1U_0402_10V6K

1

2

C732

0.1U_0402_10V6K

1

2

C750

@0.01U_0402_16V7Z

1

2

C751

@0.01U_0402_16V7Z

1

2

C705

0.1U_0402_10V6K

1

2

C742

0.1U_0402_10V6K

1

2

C740

0.1U_0402_10V6K

1

2

C693

0.1U_0402_10V6K

1

2

C737

0.1U_0402_10V6K

1

2

C720

0.1U_0402_10V6K

1

2

C735

0.1U_0402_10V6K

1

2

PA

RT

5 O

F 6

PO

WE

R

CO

RE

PW

R

AGP

PWR

MEM

I/F

PWR

CPU

I/F

PWR

ALIN

K PW

R

U51E

CHS-216IGP9050A21_BGA718

VDD_COREF10VDD_COREF9VDD_COREG12VDD_COREH12VDD_COREH13VDD_COREM12VDD_COREM13VDD_COREM14VDD_COREM17VDD_COREM18VDD_COREM19VDD_COREN12VDD_COREN13VDD_COREN14VDD_COREN17VDD_COREN18VDD_COREN19VDD_COREP12VDD_COREP13VDD_COREP14VDD_COREP17VDD_COREP18VDD_COREP19VDD_COREU12VDD_COREU13VDD_COREU14VDD_COREU17VDD_COREU18VDD_COREU19VDD_COREV12VDD_COREV13VDD_COREV14VDD_COREV17VDD_COREV18VDD_COREV19VDD_COREW12VDD_COREW13VDD_COREW14VDD_COREW17VDD_COREW18VDD_COREW19

VDD_18 H22VDD_18 H10VDD_18 AC9VDD_18 AC22

VDDP_AGP/VDDP33 G8VDDP_AGP/VDDP33 F7VDDP_AGP/VDDP33 E7

VDDP_AGP T8VDDP_AGP R4VDDP_AGP P8VDDP_AGP P7VDDP_AGP P1VDDP_AGP N4VDDP_AGP M8VDDP_AGP M7VDDP_AGP L4VDDP_AGP K8VDDP_AGP J4VDDP_AGP H7VDDP_AGP H6VDDP_AGP H5VDDP_AGP G4VDDP_AGP A2

VDDR_MEM AA23VDDR_MEM AA27VDDR_MEM AB30VDDR_MEM AC10VDDR_MEM AC12VDDR_MEM AC13VDDR_MEM AC15VDDR_MEM AC17VDDR_MEM AC19VDDR_MEM AC21VDDR_MEM AC23VDDR_MEM AC24VDDR_MEM AC25VDDR_MEM AC27VDDR_MEM AD10VDDR_MEM AD12VDDR_MEM AD13VDDR_MEM AD15VDDR_MEM AD17VDDR_MEM AD19VDDR_MEM AD21VDDR_MEM AD23VDDR_MEM AD24VDDR_MEM AD25VDDR_MEM AD27VDDR_MEM AE10VDDR_MEM AE14VDDR_MEM AE15VDDR_MEM AE19VDDR_MEM AE20VDDR_MEM AE30VDDR_MEM AE9VDDR_MEM AF27VDDR_MEM AG11VDDR_MEM AG12

VDDL_ALINKW8VDDL_ALINKAK3VDDL_ALINKAD8VDDL_ALINKAD7VDDL_ALINKAD1VDDL_ALINKAC8VDDL_ALINKAC7VDDL_ALINKAA8VDDL_ALINKAA7VDDL_ALINKAA1

VDDR2_CPUW30VDDR2_CPUU24VDDR2_CPUU23VDDR2_CPUT24VDDR2_CPUT23VDDR2_CPUP24VDDR2_CPUP23VDDR2_CPUM23VDDR2_CPUK24VDDR2_CPUK23VDDR2_CPUH24VDDR2_CPUH21VDDR2_CPUH19VDDR2_CPUH17VDDR2_CPUH16VDDR2_CPUG24VDDR2_CPUG23VDDR2_CPUG21VDDR2_CPUG17VDDR2_CPUF17VDDR2_CPUF16VDDR2_CPUE17VDDR2_CPUE16VDDR2_CPUD17VDDR2_CPUD16VDDR2_CPUC16

VDDR_MEM AG17VDDR_MEM AG18VDDR_MEM AG23VDDR_MEM AG24VDDR_MEM AG26VDDR_MEM AG8VDDR_MEM AG9VDDR_MEM AJ30VDDR_MEM AK14VDDR_MEM AK23VDDR_MEM AK8VDDR_MEM V23VDDR_MEM W23VDDR_MEM W24VDDR_MEM W25VDDR_MEM Y25

VDDP_AGP U4VDDP_AGP U5VDDP_AGP U6

C730

0.1U_0402_10V6K

1

2

C755

0.1U_0402_10V6K

1

2

C700

0.1U_0402_10V6K

1

2

C702

0.1U_0402_10V6K

1

2

C719

0.1U_0402_10V6K

1

2

C723

0.1U_0402_10V6K

1

2

C731

0.1U_0402_10V6K

1

2

C688

0.1U_0402_10V6K

1

2

C749

@0.01U_0402_16V7Z

1

2

C762

0.1U_0402_10V6K

1

2

C725

0.1U_0402_10V6K

1

2

C717

0.1U_0402_10V6K

1

2

C758

0.1U_0402_10V6K

1

2

C698

0.1U_0402_10V6K

1

2

C728

0.1U_0402_10V6K

1

2

C739

0.1U_0402_10V6K

1

2

C752

@0.01U_0402_16V7Z

1

2

C760

0.1U_0402_10V6K

1

2

C706

0.1U_0402_10V6K

1

2

C692

0.1U_0402_10V6K

1

2

C741

0.1U_0402_10V6K

1

2

C767

0.1U_0402_10V6K

1

2

C746

@0.01U_0402_16V7Z

1

2

C696

0.1U_0402_10V6K

1

2

C708

0.1U_0402_10V6K

1

2

C722

0.1U_0402_10V6K

1

2

C690

0.1U_0402_10V6K

1

2

C718

0.1U_0402_10V6K

1

2

C743

0.1U_0402_10V6K

1

2

C703

0.1U_0402_10V6K

1

2

C724

0.1U_0402_10V6K

1

2

C697

0.1U_0402_10V6K

1

2

C687

0.1U_0402_10V6K

1

2

+C714

47U_B_6.3VM

1

2

C745

@0.01U_0402_16V7Z

1

2

C711

0.1U_0402_10V6K

1

2

C691

0.1U_0402_10V6K

1

2

C716

0.1U_0402_10V6K

1

2

C756

0.1U_0402_10V6K

1

2

C729

0.1U_0402_10V6K

1

2

C701

0.1U_0402_10V6K

1

2

C757

0.1U_0402_10V6K

1

2

C748

@0.01U_0402_16V7Z

1

2

C713

0.1U_0402_10V6K

1

2

C734

0.1U_0402_10V6K

1

2

PART 6 OF 6

GND

U51F

CHS-216IGP9050A21_BGA718

VSSA29VSSAB23VSSAB24VSSAB27VSSAB4VSSAB8VSSAC1VSSAC11VSSAC14VSSAC16VSSAC20VSSAC30VSSAD11VSSAD14VSSAD16VSSAD20VSSAD4VSSAE27VSSAF30VSSAF5VSSAG10VSSAG13VSSAG16VSSAG19VSSAG22VSSAG25VSSAG7VSSAH28VSSAH3VSSAJ1VSSAK13VSSAK2VSSAK22VSSAK29VSSAK4VSSAK7VSSB1VSSB16VSSB30VSSC19VSSC23VSSC27VSSC4VSSD21VSSD25VSSE3VSSE8VSSE9VSSF27VSSF4VSSF8VSSG14VSSG15VSSG18VSSG20VSSH14VSSH15VSSH18VSSH20VSSH27VSSH4VSSH8VSSJ7 VSS J8

VSS K27VSS K4VSS L23VSS L24VSS L25VSS L7VSS L8VSS M15VSS M16VSS M27VSS M4VSS N15VSS N16VSS N23VSS N24VSS N8VSS P15VSS P16VSS P27VSS P4VSS R1VSS R12VSS R13VSS R14VSS R15VSS R16VSS R17VSS R18VSS R19

VSS R23VSS R7VSS R8VSS T12VSS T13VSS T14VSS T15VSS T16VSS T17VSS T18VSS T19VSS T27VSS T4VSS U15VSS U16VSS U7VSS U8VSS V15VSS V16VSS V27VSS V4VSS V7VSS V8VSS W15VSS W16VSS W27VSS Y1VSS Y23VSS Y24VSS Y30VSS Y4VSS Y7VSS Y8

C764

0.1U_0402_10V6K

1

2

C709

0.1U_0402_10V6K

1

2

C738

0.1U_0402_10V6K

1

2

C736

0.1U_0402_10V6K

1

2

C763

0.1U_0402_10V6K

1

2

+C695

100U_D2_10VM

1

2

C689

0.1U_0402_10V6K

1

2

C707

0.1U_0402_10V6K

1

2

C747

@0.01U_0402_16V7Z

1

2

C753

@0.01U_0402_16V7Z

1

2

C726

0.1U_0402_10V6K

1

2

C704

0.1U_0402_10V6K

1

2

C759

10U_0805_10V4Z

1

2

C727

0.1U_0402_10V6K

1

2

C766

0.1U_0402_10V6K

1

2

C744

@0.01U_0402_16V7Z

1

2

C699

0.1U_0402_10V6K

1

2

C68622U_1206_10V4Z

1

2

C754

10U_0805_10V4Z

1

2

C733

0.1U_0402_10V6K

1

2

C712

0.1U_0402_10V6K

1

2

+C715

47U_B_6.3VM

1

2

C765

0.1U_0402_10V6K

1

2

C721

0.1U_0402_10V6K

1

2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

A_AD17

A_AD30

A_AD27

A_AD31

A_AD26

A_AD24

A_AD29

A_PAR

A_AD[0..31]

A_AD22

A_AD18

A_AD23

A_AD20

A_AD21

A_AD28A_AD25

A_CBE#[0..3]

A_AD[0..31]8,19

A_PAR8,19

BSEL1 5,17

BSEL0 5,17

A_CBE#[0..3] 8,19

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

Title

Size Document Number Rev

Date: Sheet ofLA-2301 0.2

ATi RC300ML-SYS. CONFIG.B

12 47Thursday, April 08, 2004

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

A_AD25/A_AD17 : CPU VOLTAGE[1..0]

DEFAULT: 0

00: 1.05V01: 1.35V11: 1.75V10: 1.45V

0: IOQ=11:IOQ=12

DEFAULT:1

A_AD23 : CLOCK BYPASS DISABLE

A_AD24 : MOBILE CPU SELECT

0: DISABLE1: ENABLE

0: TEST MODE 1: NORMALMODE

00: 100 MHZ01: 133 MHZ10: 200MHZ11:166 MHZ

A_AD28: SPREAD SPECTRUM ENABLE

0: DISABLE1: ENABLE

0: REDUCEDE SET

DEFAULT : 0

DEFAULT: 01

1: FULL SET(internal Pull high)

A_AD26 : ENABLE IOQ

DEFAULT: 1

DEFAULT: 10

A_AD29: STRAP CONFIGURATION

00: 1.05V01: 1.35V11: 1.75V10: 1.45V

A_AD21 : AUTO_CAL ENABLE

A_AD25/A_AD17 : CPU VOLTAGE[1..0]

AD25=1 DESTOP CPUAD25=0 MOBILE CPUAD17--DON'T CARE

DEFAULT : 10: DISABLE1: ENABLE

A_AD27: FrcShortReset#

A_AD[31..30] : FSB CLK SPEED

DEFAULT:0

DEFAULT: 1

0: TEST MODE1: NORMAL(internal Pull high)

A_AD22 : OSC PAD OUTPUT PCICLK

DEFAULT: 1

DEFAULT: 1

DEFAULT : 1

A_AD20 : INTERNAL CLK GEN ENABLE

0: DEBUG MODE1: NORMAL

0: BANIAS CPU1: OTHER CPU

PAR: EXTENDED DEBUG MODE

0:PCICLK OUT 1: OSC CLK OUT

DEFAULT : 1

A_AD18 : ENABLE PHASE CALIBRATION

0: DISABLE 1:ENABLE

DEFAULT: 0R676 4.7K_0402_5%1 2

R693 @4.7K_0402_5%1 2

R685 10K_0402_5%1 2

R680 @4.7K_0402_5%1 2

R684 @10K_0402_5%1 2

R694 10K_0402_5%1 2

R674 10K_0402_5%1 2

R698 10K_0402_5%1 2

R677 4.7K_0402_5%1 2

R686 4.7K_0402_5%1 2

R691 4.7K_0402_5%1 2

R697 @4.7K_0402_5%1 2

R690 @4.7K_0402_5%1 2

R692 10K_0402_5%1 2

R689 @4.7K_0402_5%1 2

R675 @4.7K_0402_5%1 2

R701 4.7K_0402_5%1 2

D51RB751V_SOD323

2 1

R687 @4.7K_0402_5%1 2

R683 @4.7K_0402_5%1 2

R681 10K_0402_5%1 2

R679 4.7K_0402_5%1 2

R682 4.7K_0402_5%1 2

D52RB751V_SOD323

2 1

R700 @4.7K_0402_5%1 2

R699 @4.7K_0402_5%1 2

R695 10K_0402_5%1 2

R678 10K_0402_5%1 2

R688 10K_0402_5%1 2

R696 @4.7K_0402_5%1 2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_SMA13

DDR_SMA12

DDR_CS#2

DDR_SMA9DDR_SMA7

DDR_SMA5DDR_SMA3DDR_SMA1DDR_SMA10

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DM[0..7]

DDR_SMA[0..13]

DDR_SMAA8

DDR_CAS#

DDR_SMAA11DDR_SMAA9

DDR_SMAA4

DDR_SMAA1

DDR_RAS#

DDR_SMAA6

DDR_BA1

DDR_SMAA0

DDR_BA0

DDR_SMAA12

DDR_WE#

DDR_SMAA2DDR_SMAA3DDR_SMAA5

DDR_SMAA13

DDR_CKE2DDR_CKE3

DDR_SMAA7

DDR_SMAA10

DDR_SMA6

DDR_SMA8

DDR_SMA4DDR_SMA2

DDR_CS#3

DDR_SMA0

DDR_SMA11

+DDR_VREF0

DDR_DQ1

DDR_DQ2

DDR_DQ6

DDR_DQ8

DDR_DQS0

DDR_DQ12DDR_DQS1

DDR_DQ14DDR_DQ15

DDR_DQ24

DDR_DQ29

DDR_DQ26DDR_DQ30

DDR_DQ18

DDR_DQ22

DDR_DQS3

DDR_DQS2

DDR_DQ20DDR_DQ16

DDR_DQ40

DDR_DQ46DDR_DQ43

DDR_DQ52

DDR_DQS6

DDR_DQS7

DDR_DQ49

DDR_DQ33DDR_DQ36

DDR_DQ50

DDR_DQ51

DDR_DQS4DDR_DQ38

DDR_DQS5

DDR_DQ39

DDR_DQ60

DDR_DQ45

DDR_DQ61

DDR_DQ58DDR_DQ62

DDR_DQ48DDR_DQ53

DDR_DQ55

DDR_DQ54

DDR_DM7

DDR_DM6

DDR_DQ59DDR_DQ63

DDR_DQ57

DDR_DQ56

DDR_DQ44

DDR_DQ41

DDR_DQ47DDR_DQ42

DDR_DQ32DDR_DQ37

DDR_DM4

DDR_DM5

DDR_DQ35

DDR_DQ34

DDR_DQ21

DDR_DQ28

DDR_DQ25

DDR_DQ27

DDR_DQ4

DDR_DQ31

DDR_DQ3

DDR_DQ7

DDR_DQ23

DDR_DQ19

DDR_DM0

DDR_DM1

DDR_DQ9

DDR_DQ13

DDR_DM3

DDR_DM2

DDR_DQ10DDR_DQ11

DDR_DQ17

DDR_DQ0DDR_DQ5

DDR_SCKE39,16

DDR_SCS#29,16 DDR_SCS#3 9,16

DDR_SBA1 9,14,15,16

DDR_DQS[0..7] 9,14,16

DDR_DQ[0..63] 9,14,16

DDR_DM[0..7] 9,14,16

DDR_CLK39

SM_DATA_SB17,20

DDR_CLK3#9

DDR_SMA[0..13] 9,14,15,16

SM_CLK_SB17,20

DDR_CLK4# 9

DDR_SCKE2 9,16

DDR_CLK4 9

DDR_SRAS# 9,14,15,16DDR_SCAS# 9,14,15,16DDR_SWE#9,14,15,16

DDR_SBA09,14,15,16

+2.5V

+3VS

+2.5V

+2.5V

+3VS

Title

Size Document Number Rev

Date: Sheet of

LA-2301 0.2

DDR-SODIMM SLOT0

13 47Thursday, April 08, 2004

Compal Electronics, Inc.

Place these resistorclose by DIMM0,all trace lengthMax=1.4"

Layout note

Layout notePlace these resistorsclose to DIMM0,all trace length

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_SMA[0..13]

DDR_DQ[0..63]

DDR_DM[0..7]

DDR_DQS[0..7]

DDR_SBA0

DDR_SWE#DDR_SCAS#DDR_SRAS#

DDR_CLK0#

DDR_CLK0DQ[0..63]

DM[0..7]

DQS[0..7] DDR_SBA1

DDR_CKE0

DDR_CS#0

DDR_SBA0DDR_SBA1

DDR_CLK1#DDR_CLK1

DDR_CLK1#DDR_CLK1

DDR_CLK0#DDR_CLK0

DDR_CLK0#DDR_CLK0

DDR_CKE0

DDR_SBA1DDR_SBA0

DDR_CS#0

DDR_CKE0

DDR_CS#0

DDR_SBA0DDR_SBA1

DDR_CKE0

DDR_CS#0

DDR_SBA0DDR_SBA1

DDR_SMA8

DDR_SMA11

DDR_SMA9DDR_SMA10

DDR_SMA12

DDR_SMA5DDR_SMA6

DDR_SMA1

DDR_SMA3DDR_SMA2

DDR_SMA4

DDR_SMA7

DDR_SMA0

DDR_SMA13

DDR_SWE#

DDR_SRAS#DDR_SCAS#

DDR_SMA8

DDR_SMA11

DDR_SMA9DDR_SMA10

DDR_SMA12

DDR_SMA5DDR_SMA6

DDR_SMA1

DDR_SMA3DDR_SMA2

DDR_SMA4

DDR_SMA7

DDR_SMA0

DDR_SMA8

DDR_SMA11

DDR_SMA9DDR_SMA10

DDR_SMA12

DDR_SMA5DDR_SMA6

DDR_SMA1

DDR_SMA3DDR_SMA2

DDR_SMA4

DDR_SMA7

DDR_SMA0

DDR_SMA8

DDR_SMA11

DDR_SMA9DDR_SMA10

DDR_SMA12

DDR_SMA5DDR_SMA6

DDR_SMA1

DDR_SMA3DDR_SMA2

DDR_SMA4

DDR_SMA7

DDR_SMA0

DDR_SMA13

DDR_SWE#

DDR_SRAS#DDR_SCAS#

DDR_SMA13

DDR_SWE#

DDR_SRAS#DDR_SCAS#

DDR_SMA13

DDR_SWE#

DDR_SRAS#DDR_SCAS#

DDR_CLK1DDR_CLK1#

DDR_CKE0

DDR_CS#0

DDR_DQ31DDR_DQ27

DDR_DQ26DDR_DQ30

DQS0

DQS1

DDR_DQ20DDR_DQ16DDR_DQ17DDR_DQ21

DDR_DQS2

DDR_DQ18

DDR_DQ24DDR_DQ22

DDR_DQS3

DDR_DQ28

DQ20DQ16DQ17DQ21

DQS2

DQS3

DDR_DQ4

DDR_DQ1

DDR_DQ6DDR_DQ2

DDR_DQ36DDR_DQ33

DDR_DQ32DDR_DQ37

DDR_DQS4

DDR_DQ39DDR_DQ38

DDR_DQ45DDR_DQ40

DDR_DQS5

DDR_DQ8DDR_DQ12

DQS4

DQS5

DDR_DQS0

DDR_DQS1

DDR_DQ14DDR_DQ15DDR_DQ10DDR_DQ11

DDR_DM6

DDR_DQ55DDR_DQ54

DM4

DM5

DM0

DDR_DM2

DM1

DDR_DQ23DDR_DQ19

DDR_DQ57DDR_DQ56

DDR_DQ25

DDR_DM7

DDR_DQ29

DDR_DM3

DDR_DM4

DDR_DQ35DDR_DQ34DDR_DQ44DDR_DQ41

DDR_DM5

DDR_DQ46DDR_DQ43

DDR_DQ42DDR_DQ47

DDR_DQ3DDR_DQ7

DM6

DM7

DM2

DM3

DDR_DQ9DDR_DQ13

DDR_DM0

DDR_DM1

DDR_DQ52DDR_DQ49DDR_DQ48DDR_DQ53

DQS4DM4

DQS5DM5

DQS6DM6

DQS7DM7

DQS2DM2

DQS3DM3

DDR_DQS6

DDR_DQ51DDR_DQ50

DDR_DQ60DDR_DQ61

DDR_DQS7

DDR_DQ62DDR_DQ58DDR_DQ63DDR_DQ59

DQS6

DQS7

DQ3DQ7

DQ13DQ9

DQ2DQ6

DQ4

DQ15DQ10DQ11

DQ14

DQ1

DQ12DQ8

DQ18DQ22

DQ23

DQ25

DQ27DQ31

DQ26

DQ24DQ28

DQ19DQ29

DQ30

DQ33DQ36

DQ37

DQ40

DQ38

DQ35

DQ41

DQ43

DQ39

DQ44

DQ32

DQ34

DQ45

DQ42DQ47

DQ46

DQ50DQ51

DQ61DQ60

DQ53

DQ52

DQ54DQ55

DQ56DQ57

DQ62DQ58DQ63DQ59

DQ48DQ49

DM0DQS0

DQS1DM1

DQ4

DQ1

DQ2

DQ7

DQ6

DQ3

DQ8DQ12

DQ14

DQ10

DQ13DQ9

DQ11

DQ15

DQ19DQ23

DQ22

DQ21DQ17

DQ20DQ16DQ18

DQ24DQ28

DQ29

DQ26

DQ31

DQ30

DQ27DQ25

DQ32

DQ39

DQ35DQ36

DQ37

DQ34

DQ38

DQ33

DQ42

DQ44

DQ40

DQ43DQ46

DQ47

DQ41

DQ45

DQ50

DQ54DQ55

DQ48

DQ49DQ52

DQ51

DQ53

DQ61DQ60

DQ57DQ56DQ62DQ58

DQ59DQ63

DDR_DQ0

DDR_DQ5 DQ5

DQ0DQ0

DQ5

DDR_SMA[0..13]9,13,15,16

DDR_DQ[0..63]9,13,16

DDR_DQS[0..7]9,13,16

DDR_DM[0..7]9,13,16

DDR_SBA09,13,15,16

DDR_SRAS#9,13,15,16DDR_SCAS#9,13,15,16DDR_SWE#9,13,15,16

DDR_SCS#09,16

DDR_CLK09,15

DDR_CLK0#9,15

DDR_SCKE09,16

DQ[0..63] 15

DQS[0..7] 15

DM[0..7] 15

DDR_SBA19,13,15,16

DDR_CLK19,15DDR_CLK1#9,15

+DDR_VREF1+2.5V

+2.5V

+2.5V +2.5V

+DDR_VREF1 +DDR_VREF1

+DDR_VREF1 +DDR_VREF1

+2.5V

Title

Size Document Number Rev

Date: Sheet ofLA-2331 0.2

DDR(256Mb)X4-TOPB

14 47Thursday, April 08, 2004

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

1st Bank

Close pin49 Close

pin49

Close pin49Close

pin49

R176 10_0402_5%1 2

RP12

10_0804_8P4R_5%

18273645

R180 10_0402_5%1 2

RP13

10_0804_8P4R_5%

18273645

R168 10_0402_5%1 2

R163120_0402_5%

12

R174 10_0402_5%1 2

RP18

10_0804_8P4R_5%

18273645

R166 10_0402_5%1 2

C154 0.1U_0402_10V6K1 2RP3

10_0804_8P4R_5%

18273645

RP15

10_0804_8P4R_5%

18273645

U4

K4H561638F-TC/LB3_TSOPII66VSS2 66VSS1 48

VDD1 18VDD2 33

VDD0 1

VSS0 34

A029A130A231A332A435A536A637A738A839A940AP/A1028A1141A1242

VDDQ0 3VDDQ1 9VDDQ2 15VDDQ3 55VDDQ4 61

NC0 14NC1 17NC2 19NC3 25NC4 43NC5 50NC6 53

VSSQ0 6VSSQ1 12VSSQ2 52VSSQ3 58VSSQ4 64

LDQS016LDM120DQ02DQ14DQ25DQ37DQ48DQ510DQ611DQ713

CS# 24RAS# 23CAS# 22WE# 21

UDQS051UDM147DQ854DQ956DQ1057DQ1159DQ1260DQ1362DQ1463DQ1565

VREF49BA0 26BA1 27

CK 45CK# 46CKE 44

RP17

10_0804_8P4R_5%

18273645

RP11

10_0804_8P4R_5%

18273645

R175 10_0402_5%1 2

C153 0.1U_0402_10V6K1 2

C161 0.1U_0402_10V6K1 2

U6

K4H561638F-TC/LB3_TSOPII66VSS2 66VSS1 48

VDD1 18VDD2 33

VDD0 1

VSS0 34

A029A130A231A332A435A536A637A738A839A940AP/A1028A1141A1242

VDDQ0 3VDDQ1 9VDDQ2 15VDDQ3 55VDDQ4 61

NC0 14NC1 17NC2 19NC3 25NC4 43NC5 50NC6 53

VSSQ0 6VSSQ1 12VSSQ2 52VSSQ3 58VSSQ4 64

LDQS016LDM120DQ02DQ14DQ25DQ37DQ48DQ510DQ611DQ713

CS# 24RAS# 23CAS# 22WE# 21

UDQS051UDM147DQ854DQ956DQ1057DQ1159DQ1260DQ1362DQ1463DQ1565

VREF49BA0 26BA1 27

CK 45CK# 46CKE 44

R178 10_0402_5%1 2

R806 10_0402_5%1 2

RP16

10_0804_8P4R_5%

18273645

R173 10_0402_5%1 2

RP6

10_0804_8P4R_5%

18273645

RP10

10_0804_8P4R_5%

18273645

[email protected]_0402_16V7Z

1

2

C155 0.1U_0402_10V6K1 2

RP9

10_0804_8P4R_5%

18273645

RP5

10_0804_8P4R_5%

18273645

C1580.1U_0402_10V6K

1

2

U3

K4H561638F-TC/LB3_TSOPII66VSS2 66VSS1 48

VDD1 18VDD2 33

VDD0 1

VSS0 34

A029A130A231A332A435A536A637A738A839A940AP/A1028A1141A1242

VDDQ0 3VDDQ1 9VDDQ2 15VDDQ3 55VDDQ4 61

NC0 14NC1 17NC2 19NC3 25NC4 43NC5 50NC6 53

VSSQ0 6VSSQ1 12VSSQ2 52VSSQ3 58VSSQ4 64

LDQS016LDM120DQ02DQ14DQ25DQ37DQ48DQ510DQ611DQ713

CS# 24RAS# 23CAS# 22WE# 21

UDQS051UDM147DQ854DQ956DQ1057DQ1159DQ1260DQ1362DQ1463DQ1565

VREF49BA0 26BA1 27

CK 45CK# 46CKE 44

C775 0.1U_0402_10V6K1 2

C160 0.1U_0402_10V6K1 2

R177 10_0402_5%1 2

R805 10_0402_5%1 2

R172 10_0402_5%1 2

R167 10_0402_5%1 2

C780 0.1U_0402_10V6K1 2

R170 10_0402_5%1 2

C159 0.1U_0402_10V6K1 2

RP14

10_0804_8P4R_5%

18273645

C1640.1U_0402_10V6K

1

2

C776 0.1U_0402_10V6K1 2

C1570.1U_0402_10V6K

1

2

C779 0.1U_0402_10V6K1 2

C156 0.1U_0402_10V6K1 2

C162 0.1U_0402_10V6K1 2

U5

K4H561638F-TC/LB3_TSOPII66VSS2 66VSS1 48

VDD1 18VDD2 33

VDD0 1

VSS0 34

A029A130A231A332A435A536A637A738A839A940AP/A1028A1141A1242

VDDQ0 3VDDQ1 9VDDQ2 15VDDQ3 55VDDQ4 61

NC0 14NC1 17NC2 19NC3 25NC4 43NC5 50NC6 53

VSSQ0 6VSSQ1 12VSSQ2 52VSSQ3 58VSSQ4 64

LDQS016LDM120DQ02DQ14DQ25DQ37DQ48DQ510DQ611DQ713

CS# 24RAS# 23CAS# 22WE# 21

UDQS051UDM147DQ854DQ956DQ1057DQ1159DQ1260DQ1362DQ1463DQ1565

VREF49BA0 26BA1 27

CK 45CK# 46CKE 44

C778 0.1U_0402_10V6K1 2

C782 0.1U_0402_10V6K1 2

R171 10_0402_5%1 2

C777 0.1U_0402_10V6K1 2

C1520.1U_0402_10V6K

1

2

RP8

10_0804_8P4R_5%

18273645

RP7

10_0804_8P4R_5%

18273645

R179 10_0402_5%1 2

C781 0.1U_0402_10V6K1 2

C150 0.1U_0402_10V6K1 2

R165

1K_0603_1%

12

RP4

10_0804_8P4R_5%

18273645

R1641K_0603_1%

1 2

C1630.1U_0402_10V6K

1

2

R181 10_0402_5%1 2

R169 10_0402_5%1 2

-

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DQ[0..63]

DM[0..7]

DQS[0..7]

DDR_SBA1

DDR_CLK1#

DDR_CLK1

DDR_SBA0

DDR_CS#1

DDR_SBA0DDR_SBA1

DDR_CS#1

DDR_SBA0DDR_SBA1 DDR_CS#1

DDR_SBA0DDR_SBA1

DDR_CKE1

DDR_CKE1

DDR_CKE1

DDR_CLK1#DDR_CLK1

DDR_CLK1#DDR_CLK1

DDR_CLK0#DDR_CLK0

DDR_CKE1

DDR_SBA1

DDR_CS#1

DDR_CLK0#DDR_CLK0

DDR_SBA0

DDR_SMA13

DDR_SWE#

DDR_SRAS#DDR_SCAS#

DDR_SMA13

DDR_SWE#

DDR_SRAS#DDR_SCAS#

DDR_SMA13

DDR_SWE#

DDR_SRAS#DDR_SCAS#

DDR_SMA13

DDR_SWE#

DDR_SRAS#DDR_SCAS#

DDR_SMA8

DDR_SMA11

DDR_SMA9DDR_SMA10

DDR_SMA12

DDR_SMA5DDR_SMA6

DDR_SMA1

DDR_SMA3DDR_SMA2

DDR_SMA4

DDR_SMA7

DDR_SMA0

DDR_SMA8

DDR_SMA11

DDR_SMA9DDR_SMA10

DDR_SMA12

DDR_SMA5DDR_SMA6

DDR_SMA1

DDR_SMA3DDR_SMA2

DDR_SMA4

DDR_SMA7

DDR_SMA0

DDR_SMA8

DDR_SMA11

DDR_SMA9DDR_SMA10

DDR_SMA12

DDR_SMA5DDR_SMA6

DDR_SMA1

DDR_SMA3DDR_SMA2

DDR_SMA4

DDR_SMA7

DDR_SMA0

DDR_SMA8

DDR_SMA11

DDR_SMA9DDR_SMA10

DDR_SMA12

DDR_SMA5DDR_SMA6

DDR_SMA1

DDR_SMA3DDR_SMA2

DDR_SMA4

DDR_SMA7

DDR_SMA0

DDR_SMA[0..13]

DDR_SWE#

DDR_SRAS#DDR_SCAS#

DDR_CLK0

DDR_CLK0#

DDR_CLK0

DDR_CLK0#

DDR_CLK1

DDR_CLK1#

DDR_CLK1

DDR_CLK1#

DDR_CLK0DDR_CLK0#

DDR_CS#1

DDR_CKE1

DQS2DM2

DQS3DM3

DQS6DM6

DQS7DM7

DQS5DM5

DQS4DM4

DQS1DM1

DQS0DM0

DQ12

DQ14

DQ10

DQ13DQ9

DQ11

DQ15DQ8

DQ4

DQ1

DQ2

DQ7

DQ6

DQ3DQ19DQ23

DQ22

DQ17

DQ20

DQ21

DQ16DQ18

DQ24DQ28DQ26

DQ31

DQ30

DQ27DQ25DQ29

DQ50

DQ54DQ55DQ49DQ52

DQ51

DQ53DQ48

DQ61DQ60

DQ57DQ56DQ62DQ58

DQ59DQ63

DQ32

DQ39

DQ35DQ36

DQ37

DQ34

DQ38

DQ33

DQ42

DQ44

DQ40

DQ43DQ46

DQ47

DQ41

DQ45

DQ0

DQ5

DQ[0..63]14

DQS[0..7]14

DM[0..7]14

DDR_SBA19,13,14,16DDR_SCS#19,16

DDR_CLK1#9,14

DDR_CLK19,14

DDR_SCKE19,16

DDR_SBA09,13,14,16DDR_SMA[0..13]9,13,14,16

DDR_SRAS#9,13,14,16DDR_SCAS#9,13,14,16DDR_SWE#9,13,14,16

DDR_CLK09,14DDR_CLK0#9,14

+2.5V

+2.5V

+2.5V+2.5V

+DDR_VREF1

+DDR_VREF1

+DDR_VREF1

+DDR_VREF1

+2.5V

+2.5V

+2.5V

+2.5V

Title

Size Document Number Rev

Date: Sheet ofLA-2331 0.2

DDR(256Mb)X4-BTNB

15 47Thursday, April 08, 2004

Compal Electronics, Inc.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

2nd Bank

Close pin49

Close pin49

Close to U7 pin5 and 6.Close to U8 pin5 and 6.

Close to U10 pin5 and 6.Close to U9 pin5 and 6.

C784 0.1U_0402_10V6K1 2

C789 0.1U_0402_10V6K1 2

C167 0.1U_0402_10V6K1 2

C176 0.1U_0402_10V6K1 2

C783 0.1U_0402_10V6K1 2

[email protected]_0402_50V8C

1

2

C786 0.1U_0402_10V6K1 2

[email protected]_0402_50V8C

1

2

C785 0.1U_0402_10V6K1 2

[email protected]_0402_50V8C

1

2

U10

K4H561638F-TC/LB3_TSOPII66VSS2 66VSS1 48

VDD1 18VDD2 33

VDD0 1

VSS0 34

A029A130A231A332A435A536A637A738A839A940AP/A1028A1141A1242

VDDQ0 3VDDQ1 9VDDQ2 15VDDQ3 55VDDQ4 61

NC0 14NC1 17NC2 19NC3 25NC4 43NC5 50NC6 53

VSSQ0 6VSSQ1 12VSSQ2 52VSSQ3 58VSSQ4 64

LDQS016LDM120DQ02DQ14DQ25DQ37DQ48DQ510DQ611DQ713

CS# 24RAS# 23CAS# 22WE# 21

UDQS051UDM147DQ854DQ956DQ1057DQ1159DQ1260DQ1362DQ1463DQ1565

VREF49BA0 26BA1 27

CK 45CK# 46CKE 44

C166 0.1U_0402_10V6K1 2

U9

K4H561638F-TC/LB3_TSOPII66VSS2 66VSS1 48

VDD1 18VDD2 33

VDD0 1

VSS0 34

A029A130A231A332A435A536A637A738A839A940AP/A1028A1141A1242

VDDQ0 3VDDQ1 9VDDQ2 15VDDQ3 55VDDQ4 61

NC0 14NC1 17NC2 19NC3 25NC4 43NC5 50NC6 53

VSSQ0 6VSSQ1 12VSSQ2 52VSSQ3 58VSSQ4 64

LDQS016LDM120DQ02DQ14DQ25DQ37DQ48DQ510DQ611DQ713

CS# 24RAS# 23CAS# 22WE# 21

UDQS051UDM147DQ854DQ956DQ1057DQ1159DQ1260DQ1362DQ1463DQ1565

VREF49BA0 26BA1 27

CK 45CK# 46CKE 44

R807 10_0402_5%1 2 R182

120_0402_5%

12

C1800.1U_0402_10V6K 1

2

C168 0.1U_0402_10V6K1 2

C1710.1U_0402_10V6K 1

2

C788 0.1U_0402_10V6K1 2

U7

K4H561638F-TC/LB3_TSOPII66VSS2 66VSS1 48

VDD1 18VDD2 33

VDD0 1

VSS0 34

A029A130A231A332A435A536A637A738A839A940AP/A1028A1141A1242

VDDQ0 3VDDQ1 9VDDQ2 15VDDQ3 55VDDQ4 61

NC0 14NC1 17NC2 19NC3 25NC4 43NC5 50NC6 53

VSSQ0 6VSSQ1 12VSSQ2 52VSSQ3 58VSSQ4 64

LDQS016LDM120DQ02DQ14DQ25DQ37DQ48DQ510DQ611DQ713

CS# 24RAS# 23CAS# 22WE# 21

UDQS051UDM147DQ854DQ956DQ1057DQ1159DQ1260DQ1362DQ1463DQ1565

VREF49BA0 26BA1 27

CK 45CK# 46CKE 44

C173 0.1U_0402_10V6K1 2

R808 10_0402_5%1 2

[email protected]_0402_50V8C

1

2

C1780.1U_0402_10V6K 1

2

C165 0.1U_0402_10V6K1 2

C790 0.1U_0402_10V6K1 2

C1700.1U_0402_10V6K 1

2

C787 0.1U_0402_10V6K1 2

C175 0.1U_0402_10V6K1 2

C174 0.1U_0402_10V6K1 2

U8

K4H561638F-TC/LB3_TSOPII66VSS2 66VSS1 48

VDD1 18VDD2 33

VDD0 1

VSS0 34

A029A130A231A332A435A536A637A738A839A940AP/A1028A1141A1242

VDDQ0 3VDDQ1 9VDDQ2 15VDDQ3 55VDDQ4 61

NC0 14NC1 17NC2 19NC3 25NC4 43NC5 50NC6 53

VSSQ0 6VSSQ1 12VSSQ2 52VSSQ3 58VSSQ4 64

LDQS016LDM120DQ02DQ14DQ25DQ37DQ48DQ510DQ611DQ713

CS# 24RAS# 23CAS# 22WE# 21

UDQS051UDM147DQ854DQ956DQ1057DQ1159DQ1260DQ1362DQ1463DQ1565

VREF49BA0 26BA1 27

CK 45CK# 46CKE 44

-

5

5

4

4

3

3

2