Combinational Logic

description

Transcript of Combinational Logic

Chapter 4

Combinational Logic

2

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

4.1 Introduction

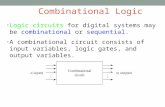

Logic circuits for digit systems maybecombinational or sequential.

A combinational circuit consists of logic gates whose outputs at any time are determend from only the presence combinations of inputs

2

A Sequential circuits contain memory elements with the logic gates the outputs are a function of the current inputs and the state of the memory elements the outputs also depend on past inputs. (chapter 5)

4

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

A combinational circuits 2 possible combinations of input valuesn

Combinational circuitsCombinatixnalxoxic Circuit

n input m outputvariables variables

4

Specific functions

Adders, subtractors, comparators, decoders, encoders,andmultiplexers

4.2 Combinational Circuits

6

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

4.3 Analysis Procedure

A combinational circuit

make sure that it is combinational not sequential

No feedback path or memory elements. derive its Boolean functions (truth table)

design verification

Example:

6

9 F2= AB+AC+BC T1= A+B+C T2= ABC T3= F2’. T1 F1= T3+T2

F1= T3+T2 = F2’. T1 +ABC = (AB+AC+BC)’.(A+B+C) +ABC = (A’+B’)(A’+C’)(B’+C’).(A+B+C) +ABC = (A’B’+A’B’C’+B’C’+A’C’). (A+B+C) +ABC = AB’C’+A’B’C+A’B’C+ABC

The truth table

8

11

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

4.4 Design Procedure

The design procedure ofcombinational circuits

From the scpecification of the circuit determine the required number of inputs and outputs.

For each input and output variables assign a symbol

Derive the truth table

Derive the simplified Boolan functions for each output as a function of the input variablesDraw the logic diagram and verify the correctness of the design

9

Example: code conversionBCD to excess-3 code

11

The maps

12

The simplified functions z = D'

y = CD +C'D‘x = B'C + B‘D+BC'D'w = A+BC+BD

z = D'y = CD +C'D' = CD + (C+D)'x = B'C + B'D+BC'D‘ = B'(C+D) +B(C+D)'w = A+B(C+D)

13

Another implementation

The logic diagram

14

17

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

4-5 Binary Adder-Subtractor

Half adder

0 + 0 = 0 ; 0 + 1 = 1 ; 1 + 0 = 1 ; 1 + 1 = 10

two input variables: x, y

two output variables: C (carry), S (sum)

truth table

15

S = x'y+xy‚ S=xÅy

C = xy

17

20

Full-Adder A full adder is similar to a half adder, but includes a

carry-in bit from lower stages. Like the half-adder, it computes a sum bit, S and a carry bit, C.For a carry-in (Z) of

0, it is the same as the half-adder:

For a carry- in(Z) of 1:

Z 0 0 0 0X 0 0 1 1 +Y +0 +1 +0 +1

C S 0 0 0 1 0 1 1 0

Z 1 1 1 1X 0 0 1 1 +Y +0 +1 +0 +1

C S 0 1 1 0 1 0 1 1

Full-Adder :

the arithmetic sum of three input bits

three input bits

x, y: two significant bitsz: the carry bit from the previous lower significant bit

Two output bits: C, S

18

19

S = x'y'z+x'yz'+ xy'z'+xyzC = xy + xz + yz

S = zÅ (xÅy)= z'(xy'+x‘y)+z(xy'+x'y)'= z‘xy'+z'x'y+z(xy+x‘y')= xy'z'+x'yz'+xyz+x'y'z

C = z(xy'+x'y)+xy= xy'z+x'yz+ xy

20

Binary adder

21

Note: n bit adder requires n full adders

Binary subtractor

A-B = A+(2’s complement of B)4-bit Adder-subtractor using M as mode of operation

M=0, A+B; M=1, A+B’+1

26

Overflow

The storage is limitedOverfow cases : 1.Add two positive numbers and obtain a negative number2. Add two negative numbers and obtain a positive numberV = 0, no overflow; V = 1, overflow

27

Example:

Note: XOR is used to detect overflow.

27

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

4-6 Decimal Adder

Add twoBCD's

9 inputs: two BCD's and one carry-in5 outputs: one BCD and one carry-out

A truth table with 2^9 entriesthe sum <= 9 + 9 + 1 = 19binary to BCD

28

BCD Adder: The truth Table29

In BCD modifications are needed if the sum > 9Must add 6 (0110) in case:

C = 1

K = 1Z8z4=1

Z =18 2Z

mo Ification when C=1 we add 6: mod

C = K +Z Z + Z Z8 4 8 2

30

Block diagram31

32

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

4.7 Binary Multiplier

Partial products–use AND operations with half adder.Note: A*B=1 only if A=B=1Oherwise 0.

fig. 4.15Two-bit by two-bit binary multiplier.

33

4-bit by 3-bit binary multiplier

Digital Circuits

Fig. 4.16Four-bit by three-bit binary

multiplier.

34

35

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

4-9 Decoder

We use here n-to-m decodera binary code of n bits = 2 distinct information

n

n input variables; up to 2 output linesonly one output can be active (high) at any time

n

36

A decoder is a combinational circute that converts n-input lines to 2^n output lines.

An implementation

Digital Circuits 38

Fig. 4.18Three-to-eight-line decoder.

37

Demultiplexers

a decoder with an enable inputreceive information in a single line and transmitsit in one of 2 possible output linesn

Fig. 4.19Two-to-four-line decoder with enable input

38

Decoder Examples

D0 = m0 = A2’A1’A0’

D1= m1 = A2’A1’A0

…etc

3-to-8-Line Decoder: example: Binary-to-octal conversion.

Expansion two 3-to-8 decoder: a 4-to-16 deocder

a 5-to-32 decoder?

Fig. 4.204 16 decoder

constructed with two3 x 8 decoders

40

Decoder Expansion - Example 2 Construct a 5-to-32-line decoder using four 3-8-line

decoders with enable inputs and a 2-to-4-line decoder.

D0 – D7

D8 – D15

D16 – D23

D24 – D31

A3

A4

A0

A1

A2

2-4-line Decoder

3-8-line Decoder

3-8-line Decoder

3-8-line Decoder

3-8-line Decoder

E

E

E

E

Combination Logic Implementation

each output = a mintermuse a decoder and an external OR gate toimplement any Boolean function of n inputvariables

A full-adder

S(x,y,z)=S(1,2,4,7)C(x,y,z)= S )3,5,6,7(C(x,y,z)= S )3,5,6,7(

Fig. 4.21Implementation of a full adder with 1 decoder

42

two possible approaches using decoder

OR(minterms of F): k inputsNOR(minterms of F'): 2 - k inputs

In general, it is not a practical implementation

n

43

44

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

4.10 Encoders The inverse function of decodera decoder

1357

2367

4567

z D D D D

y D D D D

x D D D D

=

=

=

+ + +

+ + +

+ + +

The encoder can be implementedwith three OR gates.

45

An implementation

limitations

illegal input: e.g. D 36

The output = 111 (¹3 and ¹6)=D x1

46

Priority Encoder

resolve the ambiguity of illegal inputsonly one of the input is encoded

DD

3

0

X: don't-care conditionsV: valid output indicator

has the highest priorityhas the lowest priority

47

■ The maps for simplifying outputs x and y

fig. 4.22Maps for a priority encoder

48

■ Implementation of priority

Fig. 4.23Four-input priority encoder

23

0123

x =y=

D DD D D

V D D D D

+¢+

= + + +

49

3 1 2

50

Outline :4.1 Introduction.4.2 Combinational Circuits.4.3 Analysis Procedure.4.4 Design Procedure. 4.5 Binary Adder-subtractor.4.6 Decimal Adder.4.7 Binary Multiplier.4.9 Decoders. 4.10 Encoders.4.11 Multiplexers.

4.11 Multiplexers

select binary information from one of many inputlines and direct it to a single output line

2 input lines, n selection lines and one output linee.g.: 2-to-1-line multiplexer

n

Fig. 4.24Two-to-one-line multiplexer

51

4-to-1-line multiplexer

Fig. 4.25Four-to-one-line multiplexer

52

Note

n-to- 2 decodern

add the 2 input lines to each AND gateOR(all AND gates)an enable input (an option)

n

53

Fig. 4.26Quadruple two-to-one-line multiplexer

54

Boolean function implementation

MUX: a decoders an OR gate2 -to-1 MUX can implement any Boolean functionof n input variable

n

n of these variables: the selection linesthe remaining variable: the inputs

a better solution: implement any Boolean function

of n+1 input variable

55

an example: F(A,B,C) = S(1,2,6,7)

Fig. 4.27Implementing a Boolean function with a multiplexer

56

Procedure:

Assign an ordering sequence of the input variablethe rightmost variable (D) will be used for the inputlinesassign the remaining n-1 variables to the selection

0

determine the input lines

lines w.r.t. their corresponding sequ

consider a pair of consecutive minterms startingfrom m

57

Lines with construct the truth table

Example: F(A, B, C, D) = S(1, 3, 4, 11, 12, 13, 14, 15)

Fig. 4.28 Implementing a four-input function with a multiplexer

58

Three-state gates

A multiplexer can be constructed with three-stategatesOutput state: 0, 1, and high-impedance (open ckts)

Fig. 4.29Graphic symbol for a three-state buffer

59

Example: Four-to-one-line multiplexer

Fig. 4.30Multiplexer with three-state gates

60