Characterization of a Flip-Flop Metastability Measurement Method

-

Upload

toby-daniel -

Category

Documents

-

view

213 -

download

0

Transcript of Characterization of a Flip-Flop Metastability Measurement Method

1032 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 54, NO. 5, MAY 2007

Characterization of a Flip-Flop MetastabilityMeasurement Method

Antonio Cantoni, Fellow, IEEE, Jacqueline Walker, Member, IEEE, and Toby-Daniel Tomlin, Member, IEEE

Abstract—We characterize a proposed metastability measure-ment system in which asynchronous data input and samplingclock frequencies trigger metastability. We develop an equationdescribing the time interval between data and clock inputs forpractical frequencies and show that it takes on discrete values inthe absence of jitter and that the presence of jitter perturbs thesevalues. Finally, we present experimental results supporting ourcharacterization.

Index Terms—Circuit reliability, digital system testing, flip-flops,metastability, synchronization.

I. INTRODUCTION

I N DIGITAL systems, the term metastability refers to theanomalous behavior of devices with memory that may

occur when input timing constraints are violated [1]–[5]. Theanomalous behavior is manifested in a number of ways includingequivocation of signal levels in between valid logic levels and ex-tended settling times. Typically, input timing constraints cannotbe guaranteed at the interface between sub-systems that operatewith independent clocks. When timing constraints cannot beguaranteed, metastability is unavoidable but the probability ofits occurrence can be managed by the use of synchronizers [4].Flip-flops are commonly used to realize synchronizers. Themean time between failure (MTBF) of synchronizers due tometastability is very sensitive to the metastability characteristicsof the flip-flops used. Over time, a number of methods formeasuring the metastability have been proposed [6]–[11]. Inthis paper, we are concerned with the method proposed in [11].

Given the high sensitivity of the probability of failure of syn-chronizers to the metastability characteristics of the flip-flops,it is crucial to have a very good characterization of the metasta-bility measurement system. In this paper we develop a completecharacterization of the method proposed in [11]. The key ele-ments of the measurement method proposed in [11] are shownin Fig. 1. The test setup shown makes use of the functionalityof modern oscilloscopes to produce the histograms required forcharacterization of the settling time of the device under test

Manuscript received May 18, 2006; revised November 1, 2006. The work ofJ. Walker was supported by Enterprise Ireland (IC/2005/05) and by the WesternAustralian Telecommunications Research Institute, Australian Telecommunica-tions Cooperative Research Centre. This paper was recommended by AssociateEditor K. Chakrabarty.

A. Cantoni is with the Western Australian Telecommunications Research In-stitute, Crawley, 6009 W.A., Australia (e-mail: [email protected]).

J. Walker is with the Electronic and Computer Engineering Department, Uni-versity of Limerick, Limerick, Ireland (e-mail: [email protected]).

T.-D. Tomlin was with the Western Australian Telecommunications ResearchInstitute, Crawley 6009, W.A., Australia. He is now with NEC Australia, Mul-gave, VIC 3170, Australia.

Digital Object Identifier 10.1109/TCSI.2007.895514

Fig. 1. (a) Metastability measurement system. (b) Corresponding timingdiagram.

(DUT) and also presented in this paper for validation of themodel developed for the test system. The delay line to the os-cilloscope input allows the clock edge that clocks the DUT tobe captured as an input to the oscilloscope on the same cycle asthat generated by the clock edge.

The measurement system involves the use of two pulse gener-ators whose frequencies are related in a specific way. One pulsegenerator drives the data and reset of the flip-flop under test andthe other drives the clock input. The rationale given in [11] for thechoice of frequencies is that they can be chosen such that the tran-sitions on the signal are uniformly distributed about the clock.However, this can be an inaccurate description of what happensdepending on the coherence between the two generators.

In this paper, we model the time interval between the datainput and clock in the flip-flop under test and develop an equa-tion that describes the evolution of this time interval. We developthe solution to the equation for pulse generator frequencies thatsatisfy the constraints used in practical metastability measure-ment systems. We show that in this case the time interval be-tween the clock and the data in fact takes on discrete values inthe absence of jitter in the pulse generators. Furthermore, weshow that the presence of jitter perturbs these discrete values.

In the literature, the question of whether the two pulse gener-ators should be locked to a common reference is not considered,or it is implicitly assumed that the generators are not locked. Ifthe synthesizers do not use a common reference the excitation ofmetastability is not well defined since it depends on the uncon-trolled coherence of the two synthesizers used. In the literature[11], concerns have been expressed about possible phase pullingor phase locking and various precautions have been taken in anattempt to ensure the uniform distribution of the data about the

1549-8328/$25.00 © 2007 IEEE

CANTONI et al.: CHARACTERIZATION OF FLIP-FLOP METASTABILITY MEASUREMENT METHOD 1033

clock. However, behavior of the test system under the prescribedprecautions is not well defined. On the other hand, if the twosynthesizers use a common reference then the behavior of thesystem can be controlled and well characterized. The level ofthe jitter, its probability density and the degree of coherence be-tween the two pulse generators affect the perturbation of the dis-crete values and determine how close to a uniform distributionthe signal is about the clock.

The new results presented in this paper shed light on the mea-surement system and how the parameters in the system affect theobserved metastability characteristics of the flip-flop under test.Beyond the analytical work noted above we also present simu-lation results and results obtained from an experimental system.The paper is organized as follows. In Section II we present thecharacterization of the metastability measurement method forthe case of ideal (unjittered) sources. In Section III we considerthe effect of applying jitter to the sources, and in Section IV, wepresent experimental results supporting our analysis.

II. ANALYSIS OF METASTABILITY

MEASUREMENT METHODOLOGY

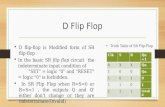

A. Flip-Flop Metastability Measurement Method

The flip-flop metastability measurement set-up described in[11] is illustrated in Fig. 1, together with a corresponding timingdiagram. The D-type flip-flop is the device whose metastabilitycharacteristics are being measured. By setting the frequencies ofsignal generators 1 and 2 appropriately, we can arrange for therising edge of the clock signal to sample the signal at variousinstances. If the oscilloscope is triggered with , the positionof the clock edge that triggered the output transition can be de-termined. The specific frequencies of the two pulse generatorsdetermine if the flip-flop enters a metastable region of operationthat results in a significantly longer output transition time. Nooutput transition is detected if the clock pulse moves past theregion where goes low.

For example, consider a clock frequency, , of 10.3 MHz(97-ns period) and a data pulse generator frequency, , of10 MHz (100-ns period). From Fig. 1(b) it is clear we can mea-sure delays up to about 35-ns long, assuming to is about 17ns. The rationale given for the choice of frequencies is that the re-sulting transitions on the input are uniformly distributed aboutthe clock [11], implying that the clock continuously sweeps pastthe at a frequency of MHz. However, this isnot the case when the frequencies are chosen such that

(1)

where and are integers.In the next section, we develop an equation that describes

the evolution of the time interval between the positive edge ofthe clock and the positive edge of D. We then show that thesolution to this equation assumes only a finite number of valueswhen (1) is valid. Specifically, we show that the time betweenthe D transition and the clock edge repeatedly visits differentdiscrete values over one period and these values are visited at arate equal to .

Fig. 2. (a) Synchronization of asynchronous pulse stream; (b) correspondingtiming diagram.

B. Characterization of the Measurement Method

Consider the synchronization of an asynchronous pulsestream of period as shown in Fig. 2(a). The pulse streamis asynchronous with respect to the clock in thatwhere is a real number. The nature of the synchronismdepends critically on . For example is rational, irrational oran integer? From the timing diagram for the synchronizationprocess for the rising edge of the asynchronous stream shownin Fig. 2(b), we obtain the following:

(2)

where can take on only two possible values, or, and is the floor (greatest integer) function,

i.e., is the largest integer such that .Why are we interested in ? Because for the purpose of

studying metastability, describes the evolution of the posi-tion of the asynchronous data transition edge with respect to theclock edges that synchronize the transition.

Defining

(3)

and rewriting (2) for the two possible values of we obtain

(4a)

(4b)

With the step function defined as

then (4a) and (4b) can be represented by the one equation

(5)

where , , is the fractional part of .Following some algebraic manipulation [12], we can express

the solution to (5) as

(6)

1034 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 54, NO. 5, MAY 2007

Fig. 3. Monotonic decreasing sub-sequences.

It turns out that (6) has been studied extensively in the con-text of the analysis of rate adaptation in communication systems[12]–[14] for when is irrational.

C. Frequencies Related by Rational Numbers

Consider the case that corresponds to a frequencyratio in (1) for which the two pulse generator frequencies arerelated by a rational number . It can be shownthat for this case the data edges visit a finite set of discrete pointswith respect to the clock edge. In fact, the sequence isperiodic, with period , since, from (6)

(7)

Furthermore, noting from (5) that either

(8a)

or

(8b)

i.e., the difference between successive values of is eitheror . In the Appendix we show that while

(8a) holds until, at ,when (8b) applies such that the subsequent value of

is , which restores the con-dition of (8a). In the Appendix, we develop a set of equations(A.6)–(A.9) for recursively calculating the sequence of values of

and show that, in general, it is made up of a set of mono-tonic decreasing sub-sequences. Within the sub-sequences, thestep between successive values of is , whereas the stepbetween successive sub-sequences is as illustratedin Fig. 3. When , then there is a single monotonicallydecreasing sequence of length , the step between successivevalues of is and the step between successive itera-tions of the sequence is .

TABLE ITIMING PARAMETERS FOR TYPICAL VALUES f = 1 MHz

TABLE IITIMING PARAMETERS FOR TYPICAL VALUES f = 10 MHz

1) Examples With Typical Frequencies: In (1), letand

(9)

then

(10)

where SF is a frequency scaling factor. We present the param-eters for an illustrative range of values of and SF in Tables Iand II. Note that is the step (denominated in sec-onds) between successive values.

2) Simulation: To validate the mathematical model we simu-lated it in Matlab. Fig. 4 shows a plot from a Matlab simulationof (6) for the case illustrated in row 1 of Table I. The top graph il-lustrates the normalized steps, , while the lower graph showsthe steps in real time. As can be seen, the sequence is periodicwith period 10, although the absolute positions of the edges de-pend on the initial phasing of . It can be clearly seen thattakes on only discrete values within the clock period

ns. The 10 values are spaced out by an amountns over a total span

of ns (on the y axisof the plot) and over a total time duration of .

D. Relationship to Metastability Triggering

As our analysis in the preceding sections has shown, in theproposed metastability test setup [11] for clock and data fre-quencies related by a rational number as in Table II, the dataedge will take on only possible positions relative to the clockedge and it will not be uniformly distributed across a smallwindow near the clock edge as suggested in [11]. Thus, it isimportant to consider the effect on metastability triggering soas to allow accurate characterization of metastable failure.

In previous studies of metastability in flip-flops, a model ofmetastability triggering using the concept of the metastablewindow has been developed [4], [5], [7], [8]. In this model, ametastable window

(11)

CANTONI et al.: CHARACTERIZATION OF FLIP-FLOP METASTABILITY MEASUREMENT METHOD 1035

Fig. 4. Matlab simulation: P=Q = 1=10. (a) Normalized: values of x forQ = 10, P = 1, SF = 1e + 005, f = 1 MHz, f = 1:1 MHz andx = 0:0. (b) Real-time: values of for Q = 10, P = 1, SF = 1e + 005,f = 1 MHz and f = 1:1 MHz.

describes the region around the sampling clock edge such thata transition within this region will trigger a metastable eventwhich requires seconds to resolve where is thenormal propagation time of the device with a metastability res-olution time constant and a maximum metastable window atnormal propagation delay .

If, in the metastability test setup described above, we assumeideal (unjittered) clock and data signals, then, with equal toone of the possible states, one of the positions visited willalways be . Thus, there is one potentially metastabletransition in every cycles of the sampling clock, since for

, the transition must be inside the metastable windowgiving an average rate of potential metastable transitions [andthus a potential mean failure rate (MFR)] of

(12)

However, if , i.e., the metastable window islarger than the increment between successive edge positions,then the number of potential transitions in the metastablewindow is given by

(13)

and the average rate of potential metastable transitions is

(14)

In a real system, due to noise and the fact that we may nothave controlled the initial phasing of the data signal and thesampling clock, may not equal one of the possible statesexactly, but instead differ from it by some small amount, ,

, where represents a window of uncertaintyaround the position of , and so we would not expect such ahigh rate of potentially metastable transitions. Now, as long as

Fig. 5. Synchronization process timing diagram with perturbation by jitter.

there will still be potential transi-tions in the metastable window. However, ifthen the likelihood of a transition in the metastable window de-pends on the relative size and positioning of and , andit is possible that there will be no metastable triggering at all.Thus, for a given value of , use of higher clock and data fre-quencies will improve the likelihood of metastable triggering;alternatively, for given clock and data frequencies, larger valuesof optimize the possibility of metastable triggering.

III. SOURCES WITH JITTER

A. Signals With Bounded Jitter

Although in our analysis we considered ideal signals, thereare a number of sources of jitter affecting the test system in-cluding jitter inherent to the clock and data signals, as well asjitter in the delay circuit and in the test setup, including the op-eration of the flip-flop under test. In the following we modelthese as bounded jitter affecting the timing of the clock and/ordata edges. The period of the ideal asynchronous input signalis still considered to be related to the ideal sampling clock fre-quency by a rational number as described in (1) and so the anal-ysis in Section II can be applied. Consider now the jittered asyn-chronous input signal shown in Fig. 5. The sequence de-scribes the evolution of the position of the positive edge of thejittered asynchronous input signal with respect to the ideal posi-tive sampling clock edges that synchronize the transition. It fol-lows from Fig. 5 that

(15)

where is the jitter between the ideal asynchronous inputsignal and the jittered asynchronous input signal. Thus, thesequence is the sequence perturbed by the corre-sponding element of the jitter sequence.

Next, we consider when the clock is also jittered. Again inthis case the jittered clock can be described in terms of the idealunjittered clock as shown in Fig. 5. We are now interested in ,the relative position of the jittered asynchronous input signalpositive edge relative to the positive edge of the jittered clock.We see that

(16)

1036 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 54, NO. 5, MAY 2007

Fig. 6. Experimental test setup.

Thus, is the perturbation of the periodic variable by thejitter term , i.e., the sum of the jitter on the clock andon the asynchronous input signal.

In the above, if is modeled as having a zero mean, sta-tionary, Gaussian distribution, then has mean and stan-dard deviation . Also, if is modeled as having a zero mean,stationary, Gaussian distribution with standard deviation ,then has mean and standard deviation .

B. Effect on Metastability Triggering

The effect of source jitter on metastability triggering will bediscussed in full in a future paper. Here it is sufficient to notethat the separation of the jittered low frequency data edge fromthe jittered clock can be expressed in terms of a deviation, ,from the ideal edge position, , as

(17)

where is the probability of the ideal edge position, sincethere are possible locations, each equally likely, and thus theprobability for a known can in principle be determined [15].For the case of Gaussian jitter the probability can be determinedfrom the Gaussian probability distribution function.

IV. EXPERIMENTS

Our simulations show that may take on only discretevalues within the clock period, . In a real system, the posi-tion of the edges may be altered by timing jitter on the sourcesand within the timing distribution system. The experimentalsetup shown in Fig. 6 was used. Two precision signal generators,locked via their 10-MHz reference system, drive an emitter-cou-pled logic (ECL) to transistor–transistor logic (TTL) translatorboard to generate two digital signals, suitable for driving TTL orCMOS devices. Initial measurements were made of the jitter af-fecting the two sources as shown in Fig. 6(a). Time interval error(TIE) histograms were collected using the Agilent 20 Gsa/s54855A oscilloscope and curves were fitted to the data using a3-parameter Gaussian distribution. At 1 MHz, the rms jitter was134 ps for the HP ESGD-4000A and 43 ps for the HP8644B. The

Fig. 7. Time interval histograms for the sources with no added jitter. (a) TIAhistogram for Q = 10, P = 1, f = 1 MHz, f = 1:1 MHz. (b) TIAhistogram for Q = 100, P = 1, f = 1 MHz, f = 1:01 MHz.

TIE between the output of the HP8644B and the ESGD-4000Awas found to be 379-ps rms jitter. This represents the spread tobe expected at each of the discrete positions due to the in-herent jitter in the generators. At 10 MHz, the rms jitter was 40ps for the HP ESGD-4000A and 30 ps for the HP8644B withthe TIE measured between the output of the HP8644B and theHP ESGD-4000A as 65.3-ps rms jitter. As shown in Fig. 6(b),the distribution of was measured using the HP5372A TimeInterval Analyser. The Agilent 20 Gsa/s 54855A oscilloscopewas used to measure the to delay at the D-flip-flop andthus construct metastability failure histograms.

The HP5372A Time Interval Analyser was used to measurethe position of the asynchronous signal edge with respect tothe clock edge. In Fig. 7(a), a time interval histogram is shownfor the case of MHz, MHz, and

, which clearly shows the ten discrete positions of theasynchronous signal edge, where the gap between each positionis ns. Measuring directly from the TIE histogramdata, a single peak is actually spread across a number of 800-psbins, such that the average spread for a peak is 6.0 ns. Thisspread is much larger than the expected TIE error (379 ps) dueto inherent source jitter, but the measured spread is due to themapping of the inherently jittered clock and data edges onto theHP5372A bin width of 800 ps. However, it is noticeable that at1 MHz and with , the spread due to the inherent jitter inthe sources is very small compared with the separation betweenthe peaks. The mapping of the clock and data edge measure-ment across the 800-ps bins of the HP5372A is also the reasonwhy the peaks do not appear to be of equal height, however eachpeak does contain the same number of data points.

As the value of increases, the number of possible posi-tions for the asynchronous signal edge increases and de-creases so that the potential for metastability triggering will in-crease. This effect can be seen in Fig. 7(b), where the one hun-dred discrete positions are shown for the case of MHz,

CANTONI et al.: CHARACTERIZATION OF FLIP-FLOP METASTABILITY MEASUREMENT METHOD 1037

Fig. 8. Metastability failure histograms for 1-MHz data frequency and sourceswith no added jitter. (a) Delay histogram for Q = 10, P = 1, f = 1 MHz,f = 1:1 MHz. (b) Delay histogram for Q = 100, P = 1, f = 1 MHz,f = 1:01 MHz.

MHz, and , and the gap between theposition of each peak is now ns. Once again, dueto the interaction between the HP5372A bin width of 800 ps andthe inherent jitter in the sources, the peaks are spread across anumber of bins. In this case, the average spread around the peaksis 4.44 ns reflecting the smaller TIE as predicted from the ini-tial measurements on the signals. However, the peaks are stillvisibly separate, i.e., there are regions where the asynchronousdata edge does not occur. Note that there are approximately 50%fewer samples collected in the last 200 ns of the clock period,due to the real-time processing limitations of the HP5372A.

In Fig. 8(a), the metastability failure histogram for anCD74HC74 flip-flop is shown for the case of MHz,

MHz, and . Note, that this does notrepresent the same data collecting run as the TIE histogram inFig. 7(a). However, the instrument settings used to generatethe data are identical. The peak number of events occurs at aclock to delay of 11.3 ns. The dip due to the Miller effectas noted by [11] is visible at 11.5 ns. Note that as in [11],delay times shorter than the “normal” delay of 11.3 ns occurdue to measurement noise. Noise from the inherent jitter onthe sources and from within the test setup may also accountfor the increased scattering of the longer delay times which isincreasingly visible from about 17 ns.

According to [11], metastable failure histograms show anelbow where two distinctly different slopes meet: the first slopeis considered to represent “deterministic metastability” becausethe delay time, although extended, is still determined by thesetup time [11]; the second less steep slope is said to be the re-gion of “true metastability” [11]. In the plots illustrated in Fig. 8,these two different slopes can be seen. Approximate breakpointscan be determined by fitting first-order logarithmic models tothe data. For the plot in Fig. 8(a), the exponential decline beginsat 12.5 ns, and the region of true metastability begins at 16 ns.In the plot, a third region can be distinguished from about 22.5ns where there are far fewer occurrences of very long delayscausing the slope to flatten out: this would appear to represent

a limit arising from the duration of data collection. Fitting theequation

(18)

where is the number of hits and is the intercept, to the re-gion of true metastability from 16 ns to 22.5 ns gives a metasta-bility resolution time constant of ns. In Fig. 8(b),the metastability failure histogram is shown for MHz,

MHz, and , , corresponding to thesame frequency settings as for the TIE histogram of Fig. 7(b)but note that, once again, it does not represent the same datacollecting run. The elbow in the metastability histogram is nowless obvious. However, the fitting of the first-order logarithmicequation as in (18) separately to each segment still gives a betterresult than fitting the equation over the whole of the exponentialdecline region. The start of the exponential decline was foundto be at 12.3 ns and the region of true metastability was found tobegin at approximately 15 ns until 22 ns, where the plateau ofthe third region of unreliable data begins. The value nsis obtained for the true metastability region.

The MTBF of the device may be calculated from the MFR in(14) as

(19)

is the metastable window of the device at the normal prop-agation delay [11]. As pointed out in [11], it must be notedthat is not a physical parameter, although it is related to thesetup-hold window of the flip-flop (see for example the deriva-tion in [5]). In principle, may be found from the interceptof (18), but it is first necessary to convert the vertical axis fromnumbers of metastable events to a time scale representing theeffective size of the metastable window for a given propagationdelay. In order to make this conversion, it is necessary to locatea point on the vertical axis which can be mapped to a time delayparameter on the x-axis. Following the procedure in [11], thiswas done by assigning the setup time of 12 ns to the measurednormal propagation delay of 11.3 ns which may then be usedwhen fitting the least squares line to the data in the determin-istic region. The propagation delay corresponding to the inflec-tion point, where the line fitted to the deterministic region inter-sects the line fitted to the true metastability region, can then beused to determine the intercept on the vertical time axis whichis . Applying this procedure to the metastability histogramsin Fig. 8 produced values of of 0.3 ns and 0.1 ns respectivelyas shown in Fig. 9. We note that the value of so determinedis strongly dependent on the slope of the line fitted to the regionof true metastability and the assumptions made when convertingthe vertical axis from numbers of events to a time axis.

An alternative approach to determining the metastablewindow is by using the number of metastable triggerings fromthe raw histogram data for both the deterministic and truemetastability regions. Clearly, the exact value depends on thelocation of the breakpoints in the metastability histogram.The proportion of hits which are metastable can be used toestimate the rate of metastable triggerings which can thenbe used to estimate based on (12)–(14). For the case

1038 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 54, NO. 5, MAY 2007

Fig. 9. Metastability failure histograms as in Fig. 8 showing determination ofT . (a) Determination of T for Q = 10, P = 1, f = 1 MHz, f =

1:1 MHz; (b) Determination of T for Q = 100, P = 1, f = 1 MHz,f = 1:01 MHz.

shown in Fig. 8(a), the resulting size of , based on the truemetastability region only, is 3.2 ns; whereas for the case shownin Fig. 8(b), it is 5.3 ns. Note that this represents the size ofthe metastable window for greater than or equal to the delayat the start of the metastable region [i.e., 16 ns in the case ofFig. 8(a), 15 ns in the case of Fig. 8(b)].

As noted in Section II, depending on the initial phasing ofthe two signals, it is possible that there will be no transitionsof the asynchronous data input which trigger metastability,particularly for a relatively small . Fig. 10 shows the mea-sured metastability failure histogram for such a case with

MHz, MHz, and . Note that theclock to delay time measured here is 11.3 ns as before.

As expected, an increase in the frequencies to the 10-MHzlevel resulted in an increase in metastable triggering as seen inFig. 11 for MHz, MHz, and .The elbow between the two different regions of metastability isdifficult to see, but curve fitting confirms that there are two re-gions of different slopes. The resolution time constant for the

Fig. 10. Metastability failure histogram with no metastable triggering.

Fig. 11. Metastability failure histogram for sources with no added jitter at10 MHz.

region of true metastability from approximately 19 to 27.5 nswas found to be ns. It is also noticeable that the gapbetween the so-called Miller Effect dip [11] and the start of theexponential decline has become much more pronounced and hasbecome a region where very few hits are found. Calculationsto determine the approximate width of gave 1.5 ns. Therate of metastable failure in the “true metastability” region ishigher than the rate at , MHz but the ap-parent window is smaller because the clock period is smaller.We note here that the metastable window size is an indicationof metastable failure probability rather than a realistic physicalparameter and that the result depends strongly on the definitionof the true metastability region.

Finally, we reproduced the frequency ratio used in [11], using MHz and MHz. The

results are shown in Fig. 12. Fig. 12(a) clearly shows how theasynchronous data edge is not completely uniformly distributedwith respect to the clock edge as very clear separation is vis-ible between the peaks representing the 100 discrete locations.In this case the resolution time constant for the region of true

CANTONI et al.: CHARACTERIZATION OF FLIP-FLOP METASTABILITY MEASUREMENT METHOD 1039

Fig. 12. TIE histogram and metastability failure histogram for frequencies fea-tured in [11]. (a) TIA Histogram for Q = 100, P = 3, f = 10 MHz,f = 10:3 MHz. (b) Delay histogram for Q = 100, P = 1, f = 10 MHz,f = 10:3 MHz.

metastability from approximately 14 to 17 ns was found to bens and was found to be about 0.18 ns reflecting

a reduced rate of metastable failure with this frequency config-uration even compared to experiments at the 1-MHz frequencylevel. This reduced rate of metastable triggering might be relatedto the more complicated sub-sequence structure of the discreteedge positions taken on in this case.

V. CONCLUSION

In this paper, we have characterized the metastability mea-surement system proposed in [11] where an asynchronousdata input and clock are used to trigger metastable failure in abistable device. Our analysis shows that the asynchronous inputis not uniformly distributed around the clock edge but insteadoccupies discrete time instants. In particular, for frequenciesrelated by rational numbers, as in (1), it has been shown that theasynchronous data input visits a finite set of discrete points withrespect to the clock edge. We have verified experimentally thediscrete nature of the time interval between the asynchronousdata input and the clock.

Although the asynchronous data input occurs only at discretetime instants with respect to the clock, metastable triggering willstill occur, since, one of these is, in the ideal system, alwaysco-incident with the clock edge. However, in a real system, dueto noise and the fact that we may not be able to control the initialphasing of the data signal and the sampling clock, initializationof the system will mean that there is a random initial offset be-tween the asynchronous data input edge and the clock. We notedthen that it is entirely possible, that due to the effect of initial-ization conditions, metastable triggering will not occur and weverified this experimentally.

In this paper, we also analyzed the effect of source jitter onthe discrete distribution of the asynchronous data input edgesand showed that the effect of jitter is to perturb the position ofthe data edges. The detailed analysis of the impact of this edge

perturbation due to source jitter on the metastability measure-ment system is a challenging problem and the subject of currentresearch and experimental validation to be presenetd in a futurepaper. The design of controlled jitter waveforms is also beinginvestigated.

APPENDIX

We assume that and consider an initial valuesuch that . Then from (8a) and infact while

(A.1)

Now we determine when (8b) holds. Let be the smallestinteger such that , then

implies that

(A.2)

Thus, the sub-sequence is a strictly de-creasing sequence of steps each equal to . At

, from (8b)

(A.3)

We check that this is the start of a new strictly monotonicallydecreasing sub-sequence by checking that (8a) holds. Using(A.1) in (A.3) and substituting for the limits of the possiblevalues of from to , it can be shown that

for (A.4)

We extend the above and we will prove that the sequenceconsists of sub-sequences denoted by

(A.5)

where . Each sub-sequence is strictly monotonicallydecreasing and has elements thus

with (A.6)

Applying the analysis above to the sub-sequencesand supposing that , then

(A.7)

where is the smallest integer such that

and so

(A.8)

1040 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 54, NO. 5, MAY 2007

Since , the element after, is given by. But using (A.7) this becomes

(A.9)

Equations (A.6)–(A.9) form a recursive procedure for com-puting all the parameters of the sub-sequences, with initial con-dition .

Note that from (A.9), we can write

(A.10)

and suppose that starting from the following sub-se-quences span exactly one period then from (A.6)

with (A.11)

then since , from (A.10) and (A.11) weobtain

(A.12)

That is, there are monotonic decreasing sub-sequences ineach period and there are uniformly spaced discrete pointsvisited. Thus, it follows for the simple case when , i.e.,

, there is a single monotonically decreasing sequenceof length .

REFERENCES

[1] I. Catt, “Time loss through gating of asynchronous logic signal pulses,”IEEE Trans. Electron. Comput., vol. EC-15, no. 2, pp. 108–111, Feb.1966.

[2] T. J. Chaney and C. E. Molnar, “Anomalous behavior of synchronizerand arbiter circuits,” IEEE Trans. Comput., vol. C-22, no. 4, pp.421–422, Apr. 1973.

[3] D. J. Kinniment and J. V. Woods, “Synchronization and arbitration cir-cuits in digital systems,” Proc. Inst. Elect. Eng., vol. 123, pp. 961–966,Oct. 1976.

[4] L. Kleeman and A. Cantoni, “Metastable behavior in digital systems,”IEEE Design Test, pp. 4–19, Dec. 1987.

[5] A. Pfister, Metastability in Digital Circuits With Emphasis on CMOSTechnology. Konstanz, Germany: Hartung-Gorre, 1989.

[6] L.-S. Kim and R. W. Dutton, “Metastability of CMOS latch/flip-flop,”IEEE J. Solid-State Circuits, vol. 25, no. 8, pp. 942–951, Aug. 1990.

[7] H. J. M. Veendrick, “The behavior of flip-flops used as synchronizersand prediction of their failure rate,” IEEE J. Solid-State Circuits, vol.15, no. 4, pp. 169–176, Apr. 1980.

[8] F. Rosenberger and T. J. Chaney, “Flip-flop resolving time test circuit,”IEEE J. Solid-State Circuits, vol. 17, no. 8, pp. 731–738, Aug. 1982.

[9] J. U. Horstmann, H. W. Eichel, and R. L. Coates, “Metastability be-havior of CMOS ASIC flip-flops in theory and test,” IEEE J. Solid-StateCircuits, vol. 24, no. 2, pp. 146–157, Feb. 1989.

[10] T. C. Tang, “Experimental studies of metastability behaviors of sub-micron CMOS ASIC flip flops,” in Proc. 4th Annu. IEEE Int. ASICConf. and Exhibition, 1991, pp. 7-4.1–7-4.4.

[11] C. Dike and E. Burton, “Miller and noise effects in a synchronizingflip-flop,” IEEE J. Solid-State Circuits, vol. 34, no. 6, pp. 849–855,Jun. 1999.

[12] J. Walker and A. Cantoni, “Jitter analysis for two methods of synchro-nization for external timing injection,” IEEE Trans. Commun., vol. 44,no. 2, pp. 269–276, Feb. 1996.

[13] G. F. Pierobon and R. P. Valussi, “Jitter analysis of a double modulatedthreshold pulse stuffing synchronizer,” IEEE Trans. Commun., vol. 39,no. 4, pp. 594–602, Apr. 1991.

[14] R. C. Lau and P. E. Fleischer, “Synchronous techniques for timingrecovery in BISDN,” IEEE Trans. Commun., vol. 43, no. 4, pp.1810–1818, Apr. 1995.

[15] I. Shankar, S. A. Morris, and C. G. Hutchens, “Characterizing metasta-bility and jitter in CMOS latch/flip-flop used as a digital mixer,” in Proc.45th Midwest Symp. Circuits Syst., 2002, vol. 3, pp. III-560–III-563.

Antonio Cantoni (M’74–SM’83–F’98) was born inSoliera, Italy, on 30 October, 1946. He received theB.E. (first class honors) and Ph.D. degrees from theUniversity of Western Australia, Nedlands, WA, Aus-tralia, in 1968 and 1972, respectively.

He was a Lecturer in Computer Science at theAustralian National University, Canberra, Australia,in 1972. He joined the Department of Electrical andElectronic Engineering at the University of New-castle, Shortland, NSW, Australia, in 1973, wherehe held the Chair of Computer Engineering until

1986. In 1987, he joined QPSX Communications Ltd, Perth, WA, Australia, asDirector of the Digital and Computer Systems Design Section for the develop-ment of the DQDB Metropolitan Area Network. From 1987 to 1990, he wasalso a Visiting Professor in the Department of Electrical and Electronic Engi-neering at the University of Western Australia. From 1992 to 1997, he was theDirector of the Western Australian Telecommunications Research Institute andProfessor of Telecommunications at Curtin University of Technology, Perth,WA, Australia. During this period, he was also the Director of the CooperativeResearch Centre for BroadBand Telecommunications and Networking. From1997 to 2000 he was Chief Technology Officer of Atmosphere Networks anoptical networks startup that he co-founded. Since 2000, he has been ResearchDirector of the Western Australian Telecommunications Research Institute andProfessor of Telecommunications at the University of Western Australia. He iscurrently a Consultant to Sensear Pty Ltd and Ispire Networks Pty Ltd startupsthat he co-founded. His research interests include adaptive signal processing,electronic system design, phase locked loops, and networking.

Dr Cantoni is a Fellow of the IEEE and a Fellow of the Australian Academyof Technological Sciences and Engineering. He has been an Associate Editor ofthe IEEE TRANSACTIONS ON SIGNAL PROCESSING.

Jacqueline Walker (M’93) was born in London,U.K. She received the B.A. and the B.E. degrees(first class honours), both from the University ofWestern Australia, Nedlands, WA, Australia, in1987 and 1992 respectively, and the Ph.D. degreefrom Curtin University of Technology, Perth, WA,Australia, in 1997.

During 1996–1997, she worked as a ResearchEngineer at the Australian TelecommunicationsResearch Institute (ATRI), Crawley, WA, Australia.In November 1997, she joined the Department of

Electronic and Computer Engineering at the University of Limerick, Limerick,Ireland as a Lecturer. Her research interests include signal processing applied tobiomedical, speech and music signals, higher order statistics, and metastability.

Toby-Daniel Tomlin (M’96) received the B.E. de-gree (first class honours) and Ph.D. degree from TheUniversity of Western Australia, Nedlands, WA, Aus-tralia, in 1996 and 2004, respectively.

After graduating in 1996, he worked on soft-ware defined radio as a Research Engineer at theAustralian Telecommunication Research Institute(ATRI), Crawley, WA, Australia. His Ph.D. studyinvestigated timing impairments in electronic sys-tems. He has lectured in electronic systems andnetworking at The University of Western Australia.

During his time at the Australian Telecommunications Cooperative ResearchCentre, he researched timing impairments and metastability in electronicsystems. In 2005, he was appointed a Design Engineer with NEC Australia,Mulgrave, VIC, Australia, within the 3G Mobile Research and Development.His interests include low-phase-noise amplifiers and electronic system design.