8086 architecture ppt

-

Upload

swapnil-patil -

Category

Documents

-

view

2.143 -

download

1

Transcript of 8086 architecture ppt

8086 ARCHITECTURE8085 VS 8086

The main limitation of 8-bit(8085) microprocessor were their low speed of execution , low memory,

addressing capability limited number of General purpose register and a less powerful instruction set .

All these limitations of 8-bit microprocessor tempted the designers to go for more powerful processors in terms of advance architecture more processing

capability and more powerful instruction set . 8086 was a result of such a development design efforts.

*Intel 8086 is a 16-bit microprocessor is intended to be used as a CPU in microprocessor

*8086 has a 16-bit Data bus so it can Read data from or Write data to memory and ports either 16-bit or 8-bit at a time.

INTEL ARCHITECTURE

REGISTERS OF 8086

CATEGORY BITS REGISTER NAMES

GENERAL 16 AX,BX,CX,DX

8 AH,AL,BH,BL,CH,CL,DH,DL

POINTER 16 SP(STACK POINTER), BS(BASE POINTER)

INDEX 16 SI(SOURCE INDEX), DI(DESTINATION INDEX)

SEGMENT 16 CS(CODE SEGMENT)DS(DATA SEG)SS(STACK SEGMENT)ES(EXTRA SEGMENT)

INSTRUTION 16 IP(INSTRUCTION POINTER)

PIN DAIGRAM

8086 PIN DAIGRAM DESCRIPTION

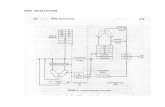

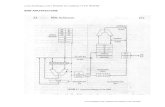

AD15-AD0 ADDRESS DATA BUS: These lines constitute the time multiplexed memory

or i/o address and data bus . ALE (ADDRESS LATCH ENABLE): A HIGH on this line causes the lower

orders 16-bit address bus can be used as data bus. READY: READY is the acknowledgement from the addressed memory or

i/o device that will be complete the data transfer . INTR : INTERRUPT REQUEST is a level triggered input which is sample

during the last clock cycle of each instruction to determine if the processor should enter into interrupt acknowledgment operation .

INTA : INTERRUPT ACKNOWLEDGEMENT from the mp. RESET : It causes the processor to immediately terminate its present

activity.