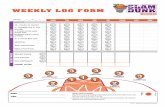

Weekly Report Form

-

Upload

pronadeep-bora -

Category

Documents

-

view

217 -

download

0

description

Transcript of Weekly Report Form

Department of Electronics and Communication Engineering

NIT Nagaland

Project Phase-I

WEEKLY REPORT

Name: - Pronadeep Bora Registration No.2014346006

From Date 25-08-15 to Date 28-08-15

Tentative Title-

FPGA Implementation for Temperature Monitoring System

Abstract-

The project idea is to design a hardware and implementation of a temperature monitoring

system in real time. The design based on hardware implementation of controller circuit, the

controller circuit will be designed using Verilog HDL (Hardware Description Language).The

design will be implemented using Xilinx Software tools (Vivado or ISE depending on the

FPGA board used).The Temperature sensing circuit and Temperature measurement unit will

be designed and feed to the controller. The monitoring system will be a LCD (Liquid Crystal

Display) and a RS232 communication port to connect with other monitoring devices.

Tentative System Architecture:

Tentative Block Diagram of System Board

TMU-Temperature Measurement unit

The Control unit, ROM memory, LCD module, RS 232 communication port will be designed

using Verilog HDL in Xilinx software tool and the Bit Stream generated will be implemented

in FPGA board.

CONTROL

UNIT

ROM

LCD TMU Temp.

Sensor

RS 232

The Temperature Measurement unit will comprise of Temperature Sensing Circuit, Signal

Conditioning Circuit and ADC (Analog to Digital Converter) will be designed and

implemented on hardware.

Available FPGA boards:

Zed Board Zynq 7000 Development Board

Genesys Virtex5 FPGA Development Board

Nexys 4 Artix-7 FPGA Board

Atlys™ Spartan-6 FPGA Development Board

Guide

(Name and Signature)

Remarks from Guide:-