VLSI-SoC, Atlanta J. Dalmasso, ML Flottes, B. Rouzeyre CNRS/ Univ. Montpellier II France 1...

-

Upload

justine-lowrance -

Category

Documents

-

view

212 -

download

0

Transcript of VLSI-SoC, Atlanta J. Dalmasso, ML Flottes, B. Rouzeyre CNRS/ Univ. Montpellier II France 1...

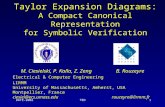

VLSI-SoC, Atlanta

J. Dalmasso, ML Flottes, B. RouzeyreCNRS/ Univ. Montpellier II

France

117/10/2007

17/10/2007 2

Introduction

T1, W1 T2 = T1/10, W2 = 10xW1

T3 = T1/10, W3 = W1

DUT DUT DUT

3 30 330

... ...

decompression

17/10/2007 3

Introduction

T1, W1 T2 = T1/10, W2 = 10xW1

T3 ≥ T1/10, W3 = W1

DUT DUT DUT

3 30 330

... ...

decompression

17/10/2007 4

Test Data

Horizontal Compression

CompressedTest Data

N

W<<N

On-Chip Decompression

N

W

DUT

00

Scan enable

Control

CLKFSM

W ATE Channels

N Scan Chains

SR SR SR SR

Compression method independent of the circuit netlist independent of the test data no specific test tool is needed No impact on fault coverage

XXXXX0XXXX1X

17/10/2007 5

Test Data

Horizontal Compression

CompressedTest Data

N

W<<N

On-Chip Decompression

N

W

DUT

00

Scan enable

Control

CLKFSM

W ATE Channels

N Scan Chains

SR SR SR SR

Compression method independent of the circuit netlist independent of the test data no specific test tool is needed No impact on fault coverage core test time may be affected

Compression at system levelProblem Statement (test time optimization)AlgorithmExperimental Results

17/10/2007 6

Outline

17/10/2007 7

Test Access Mechanism = Test bus1500 ready coresPartitioned test buses

WTam1

WTam2

C5

C1 C2 C3

C4

WTam1

WTam2

C5WATE

C4 C2 C3

C1

17/10/2007 8

WTam1

WTam2

WATE

C1 C2 C3

C4 C5

Solution space

C4 C2 C3

C1WTam1

WTam2

C5WATE

17/10/2007 9

WTam1 WATE1

WTam3 WATE3

WTam2 WATE2

C1 C4

C2

C3 C5

C1 C2 C3

C4 C5WTam1

WTam2

WATE

Solution space

17/10/2007 10

Inputs WATE channels, WTAM bit width n Cores Ci

Problem Determine optimal number of sub-buses Determine compression ratio on every bus Core assignment/scheduling for minimal test time

compression increases test parallelism but may increase individual test time

WTam1WATE1

WTam3WATE3

WTam2WATE2

C1 C4

C2

C3 C5

AlgorithmOuter loopFor each ATE channel

partitionFor each compatible TAM

partition Find best core assignment

(the lowest total test time)

If this assignment decreases global test time memorize architecture and its

associated scheduling

17/10/2007 11

AlgorithmOuter loop Inner loopFor each ATE channel

partitionFor each compatible TAM

partition Find best core assignment

(the lowest total test time)

If this assignment decreases global test time memorize architecture and its

associated scheduling

Initial Solution Put each core on the smallest

possible bus Compute test time

Improvement Find bus Bi which has the

longest test time For each core on Bi,

For all other bus Bj ( j ≠ i ) move core from Bi to Bj Compute test time

Move core C from Bi to Bj so that test time is smallest

17/10/2007 12

17/10/2007 13

s38417 wi =16 chaînes de scan

0

10000

20000

30000

40000

50000

60000

70000

80000

90000

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16WATE: #de cannaux testeurs

cy

cle

s

Compression Identification

WATE

103

cycl

es

Compression

Identification

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

10

20

30

40

50

60

70

80

90

Indentification: Test Time = ( / compression ratio) +

17/10/2007 14

s38417 wi =16 chaînes de scan

0

10000

20000

30000

40000

50000

60000

70000

80000

90000

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16WATE: #de cannaux testeurs

cy

cle

s

Compression Identification

WATE

103

cycl

es

Compression

Identification

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

10

20

30

40

50

60

70

80

90

Indentification: Test Time = ( / compression ratio) +

17/10/2007 15

C5 C6 C7 C8

C1 C2 C3 C4

C13 C14 C15 C16

C9 C10 C11 C12

64 TAM

32 ATE

17/10/2007 16

p # conf. TATLines' parameters

(WATE-i / WTAM-i)

2 522 127413 (16,16) / (16, 48)

3 44639 90457 (8,9,15) / (14,16,34)

4 1345142 68361 (5,7,8,12) / (7,14,16,27)

5 18605924 57941 (5,5,7,7,8) / (6,12,14,16,16)

17/10/2007 17

C9 C10 C7 C6

C1 C2 C3 C4

C16 C14

C12 C5 C11

5

C15 C13

C8

6

12

14

16

16

5

7

7

8

ATE=32TAM=64T3=57941

ATE=TAM=64T1=55738

No CompressionATE=TAM=32T2=127413

Data Compression for System testingTest width reduction is the primary goal

higher test parallelism without ATE cost

Method for exploring architectural solutions one compressor for all cores, one compressor per core, no

compressor... independant of the compression technique

Test time reduction > 50%

17/10/2007 18

Conclusion

17/10/2007 19