Unit I Testing and Fault Modelling. Syllabus Introduction to testing – Faults in Digital Circuits...

-

Upload

paul-warner -

Category

Documents

-

view

223 -

download

4

Transcript of Unit I Testing and Fault Modelling. Syllabus Introduction to testing – Faults in Digital Circuits...

Unit I Testing and Fault Modelling

Syllabus

Introduction to testing – Faults in Digital

Circuits – Modelling of faults – Logical Fault Models

– Fault detection – Fault Location – Fault dominance

– Logic simulation – Types of simulation – Delay

models – Gate Level Event – driven simulation.

Basic Concept of Testing

Related fields Verification: To verify the correctness of a design

Diagnosis: To tell the faulty site Reliability: To tell whether a good system will work

correctly or not after some time. Debug: To find the faulty site and try to eliminate the

fault

VDD

0/10

000

0

Testing: To tell whether a circuit is good or bad

Why Studying Testing?

• Economics!– Reduce test cost (enhance profit)

• Automatic test equipment (ATE) is extremely expensive

– Shorten time-to-market• Market dominating or sharing

– Guarantee IC quality and reliabilityDefects detected in CostWafer 0.01 – 0.1Packaged chip 0.1 – 1Board 1 – 10System 10 – 100Field 100 – 1000

Rule of Ten: Cost to detect faulty IC increases by an order of magnitude

Principle of Testing

• Testing typically consists of– Applying set of test stimuli (input patterns, test vectors)

to inputs of circuit under test (CUT), and– Analyzing output responses

• The quality of the tested circuits will depend upon the thoroughness of the test vectors

Circuit under Test(CUT)

-101111-00-0-1-01--00-101

1-0010011--11011001-01-11

ComparatorStoredCorrectResponse

Test Result

Input Patterns Output Response

Introduction• Integrated Circuits (ICs) have

grown in size and complexity since the late 1950’s– Small Scale Integration (SSI)– Medium Scale Integration (MSI)– Large Scale Integration (LSI) – Very Large Scale Integration (VLSI)

• Moore’s Law: scale of ICs doubles every 18 months– Growing size and complexity poses

many and new testing challenges

VLSI

LSIMSI

SSI

Importance of Testing• Moore’s Law results from decreasing feature size

(dimensions)– from 10s of m to 10s of nm for transistors and

interconnecting wires

• Operating frequencies have increased from 100KHz to several GHz

• Decreasing feature size increases probability of defects during manufacturing process– A single faulty transistor or wire results in faulty IC– Testing required to guarantee fault-free products

N = # transistors in a chipp = prob. (a transistor is faulty)Pf = prob. (the chip is faulty)

Pf = 1- (1- p) N

If p = 10-6

N = 106

Pf = 63.2%

Importance of Testing (contd.)

Difficulties in Testing• Fault may occur anytime - Design - Process - Package - Field

• Fault may occur at any place

• VLSI circuit are large

- Most problems encountered in testing are NP- complete • I/O access is limited

Vss

Vdd

How to do testing

• Circuit modeling• Fault modeling

• Logic simulation• Fault simulation• Test generation

• Design for test• Built-in self test

• Synthesis for testability

Modeling

ATPG

Testable design

From designer’s point of view:

Levels of Structural Description

• Switch level

• Higher/ System level

• Circuit level

• Gate level

B

E

C

1

C2C3

C

4

C

E

CD F

G

AB

VDD VDD VDD

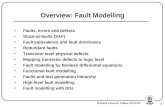

Why We Need Fault Models?

• Fault models are needed for – test generation, – test quality evaluation and – fault diagnosis

• To handle real physical defects is too difficult• The fault model should

– reflect accurately the behaviour of defects, and– be computationably efficient

• Usually combination of different fault models is used• Fault model free approaches (!)

12

Fault Modeling• The effects of physical defects• Most commonly used fault model: Single stuck-at

fault

AB

CD

E

F

G

A s-a-1A s-a-0

E s-a-1E s-a-0

D s-a-1D s-a-0

C s-a-1C s-a-0

B s-a-1B s-a-0

F s-a-1F s-a-0

G s-a-1G s-a-0

14 faults• Other fault models: - Break faults, Bridging faults, Transistor stuck-open faults, Transistor stuck-on faults, Delay faults

Fault Modeling• The effects of physical defects• Most commonly used fault model: Single stuck-at

fault

AB

CD

E

F

G

A s-a-1A s-a-0

E s-a-1E s-a-0

D s-a-1D s-a-0

C s-a-1C s-a-0

B s-a-1B s-a-0

F s-a-1F s-a-0

G s-a-1G s-a-0

14 faults• Other fault models: - Break faults, Bridging faults, Transistor stuck-open faults, Transistor stuck-on faults, Delay faults

Fault Modeling

• Fault modeling levels – Transistor level faults– Logic level faults

» stuck-at fault model » bridging fault model» open fault model » delay fault model

– Register transfer level faults– ISA level faults (MP faults)– SW level faults

• Hierarchical fault handling• Functional fault modeling

Low-Level models

High-Level models

15

Faults and their Detection

• Physical failures are manifested as electrical failures and are interpreted as faults on the logic level

• Several physical defects may be mapped into few fault types

• The main fault type is Stuck-at Fault• A fault is detected by a test pattern• Test pattern is an input combination that confirms

the presence of the fault

ZB

A R1

R 2

RL

BA Z

ZA

A Z

(a) (b)

Possible Defects

• Two technologies, two physical defects map into the same stuck-at zero fault

• Notation used - A SA0, A@0, or A/0

Inputs FF Faulty ResponseAB Response A/0 B/0 Z/0 A/1 B/1 Z/100 0 0 0 0 101 0 0 0 0 110 0 0 0 1 111 1 0 0 1 1

A

BZ

Detecting Stuck-at Faults

Fill in the blanks in faulty response A/0 and A/1

Inputs FF Faulty ResponseAB Response A/0 B/0 Z/0 A/1 B/1 Z/100 0 0 0 0 0 0 101 0 0 0 0 1 0 110 0 0 0 0 0 1 111 1 0 0 0 1 1 1

A

BZ

Detecting Stuck-at Faults

Detecting Stuck-at Faults

A

BZ

Inputs Fault Free Faulty ResponsesAB Response A/0 B/0 Z/0 A/1 B/1 Z/100 0 0 0 0 0 0 101 0 0 0 0 1 0 110 0 0 0 0 0 1 111 1 0 0 0 1 1 1

Structural and Functional Fault Modeling

Fault models are: explicit and implicit· explicit faults may be enumerated· implicit faults are given by some

characterizing properties

Fault models are: structural and functional:· structural faults are related to

structural models, they modify interconnections between components

· functional faults are related to functional models, they modify functions of components

1

&

&x1

x2

x3

x21

x22y

a

b

Structural faults:- line a is broken- short between x2 and x3

Functional fault:

Instead of 3221 xxxxy

32xxy

Classification of fault models

21

Structural Logic Level Fault ModelingWhy logic fault models?• complexity of simulation

reduces (many physical faults may be modeled by the same logic fault)

• one logic fault model is applicable to many technologies

• logic fault tests may be used for physical faults whose effect is not completely understood

• they give a possibility to move from the lower physical level to the higher logic level

1x2

x1

Broken line

1x2

x1

Bridge to ground

0VSingle model: Stuck-at-0

Two defects:

Stuck-at fault model:

Stuck-at Fault PropertiesFault equivalence and fault dominance:

&

&ABC

D

A B C D Fault class

1 1 1 0 A/0, B/0, C/0, D/1 Equivalence class0 1 1 1 A/1, D/01 0 1 1 B/1, D/0 Dominance classes1 1 0 1 C/1, D/0

Fault collapsing:

&1

1

1

0

1&

&1

0

1

1

0

DominanceDominanceEquivalence

Equivalence

Fault Redundancy

1

&

&

&

1

1

01

10

01

1

1

Hazard control circuitry:

Redundant AND-gateFault 0 is not testable

0

Error control circuitry:

Decoder

1

E 1 if decoder is fault-free Fault 0 is not testable

E

24

Fault Redundancy

0

)(

2

434211

x

y

xxxxxxy

Faults at x2 are not testable, the

node is redundant

1

&

&

&

1&

x1

x2

&x4

x3

y

Redundant gates (bad design):

1

&

&

&

x1

&x4

x3

y

142

423411211

x

y

xxxxxy

if 04 x

Fault x42 0 is not testable

x41

x42

x11

x12

25

Fault RedundancyRedundant gates (bad design):

341 xxxy

1

&

&

&

x1

&x4

x3

y

142

423411211

x

y

xxxxxy

if 04 x

Fault x42 0 is not testable

x41

x42

x11

x12

1

&

&

x1

x3

y

112

3411211

x

y

xxxxy

Fault x12 1 is not testable

x4

x11

x12

if 11 x

Final result of optimization:

1

x3

y

x1

x4

26

Fault Coverage (FC)

FC =# faults detected# faults in fault list

ab

c 6 stuck-at faults( a0,a1,b0,b1,c0,c1 )

Test faults detected FC{(0,0)}{(0,1)}{(1,1)}{(0,0),(1,1)}{(1,0),(0,1),(1,1)}

c1

a1,c1

a0,b0,c0

a0,b0,c0,c1

all

16.67%33.33%50.00%66.67%

100.00%

Example:0 00

1 11

1 00

Wafer Yield (Chip Yield, Yield)

Wafer yield = 12/22 = 0.55 Wafer yield = 17/22 = 0.77

Wafer

Defects

Good Chip

Faulty Chip

Testing and Quality

• Quality of shipped parts is a function of yield Y and the test (fault) coverage T

• Defect level (DL, reject rate in textbook): fraction of shipped parts that are defective

ICFabrication Testing

Yield:Fraction of good parts

Rejects

Shipped Parts

Quality:Defective partsper million (DPM)

Fault Equivalence• Number of fault sites in a Boolean gate circuit = #PI +

#gates + # (fanout branches).• Fault equivalence: Two faults f1 and f2 are equivalent

if all tests that detect f1 also detect f2.• If faults f1 and f2 are equivalent then the

corresponding faulty functions are identical.• Fault collapsing: All single faults of a logic circuit can

be divided into disjoint equivalence subsets, where all faults in a subset are mutually equivalent. A collapsed fault set contains one fault from each equivalence subset.

Equivalence Rules

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0

sa1

sa0

sa1

sa0sa0sa1

sa1

sa0

sa0

sa0sa1

sa1

sa1

AND

NAND

OR

NOR

WIRE

NOT

FANOUT

Equivalence Example

sa0 sa1sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

Faults in redremoved byequivalencecollapsing

20Collapse ratio = ----- = 0.625 32

Fault Dominance• If all tests of some fault F1 detect another fault F2, then F2

is said to dominate F1.• Dominance fault collapsing: If fault F2 dominates F1, then

F2 is removed from the fault list.• When dominance fault collapsing is used, it is sufficient to

consider only the input faults of Boolean gates. See the next example.

• In a tree circuit (without fanouts) PI faults form a dominance collapsed fault set.

• If two faults dominate each other then they are equivalent.

Dominance Example

s-a-1F1

s-a-1F2 001

110 010 000101 100

011

All tests of F2

Only test of F1s-a-1

s-a-1

s-a-1s-a-0

A dominance collapsed fault set

Dominance Example

sa0 sa1sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

sa0 sa1

Faults in redremoved byequivalencecollapsing

15Collapse ratio = ----- = 0.47 32

Faults in yellowremoved bydominancecollapsing

Classes of Stuck-at Faults• Following classes of single stuck-at faults are

identified by fault simulators:• Potentially-detectable fault – Test produces an unknown

(X) state at primary output (PO); detection is probabilistic, usually with 50% probability.

• Initialization fault – Fault prevents initialization of the faulty circuit; can be detected as a potentially-detectable fault.

• Hyperactive fault – Fault induces much internal signal activity without reaching PO.

• Redundant fault – No test exists for the fault.• Untestable fault – Test generator is unable to find a test.

Transistor (Switch) Faults

• MOS transistor is considered an ideal switch and two types of faults are modeled:

• Stuck-open -- a single transistor is permanently stuck in the open state.

• Stuck-short -- a single transistor is permanently shorted irrespective of its gate voltage.

• Detection of a stuck-open fault requires two vectors.

• Detection of a stuck-short fault requires the measurement of quiescent current (IDDQ).

Stuck-Open Example

Two-vector s-op testcan be constructed byordering two s-at testsA

B

VDD

C

pMOSFETs

nMOSFETs

Stuck-open

1

0

0

0

0 1(Z)

Good circuit states

Faulty circuit states

Vector 1: test for A s-a-0(Initialization vector)

Vector 2 (test for A s-a-1)

Stuck-Short Example

A

B

VDD

C

pMOSFETs

nMOSFETs

Stuck-short

1

0

0 (X)

Good circuit state

Faulty circuit state

Test vector for A s-a-0

IDDQ path infaulty circuit

Types of Simulation

• Compiler driven simulation• Activity-directed simulation• Event-driven simulation

Delay Model

• Delay modeling for gates– Transport delay– Inertial delay

• Delay modeling for functional elements• Delay modeling in RTLs• Other aspects of Delay modeling

Gate level Event driven simulation

• Transition-Independent Nominal Transport delay

• Other logic values• Other delay models