System design and evaluation of a large modular photonic ATM switch

-

Upload

jean-baptiste-jacob -

Category

Documents

-

view

213 -

download

0

Transcript of System design and evaluation of a large modular photonic ATM switch

Communication Networks

System Design and Evaluation of a Large Modular Photonic ATM Switch

Jean-Baptiste Jacob Alcatel CIT - Direction Technique 4, Rue Louis de Broglie ,22304 Lannion - France Maurizio Casoni, Giorgio Corazza, Carla Raffaelli Dipartimento di Elettronica, Informatica e Sistemistica, Universith di Bologna Viale Risorgimento 2,40136 Bologna - Italy Francesco Masetti Alcatel Alsthom Recherche - Unite Fibres et Systemes Photoniques Route de Nozay, 91460 Marcoussis - France Pierre Parmentier Alcatel CIT - Direction Technique - 10, Rue Latbcobre, 78141 Vblizy Cedex - France

Abstract. A photonic ATM switching node based on the Fibre Delay Line switching element de- veloped in the framework of the RACE project ATMOS (ATM Optical Switching) is described. The feasibility of this switching element has been proved within the physical limitation of present- day technology to support up to 16 input and 16 output lines and a buffer capacity of at least 16 cells for each output. In this paper various interconnection options are discussed with the aim of a large, high throughput switch implementation. In particular a Clos architecture is chosen for the design of a 256 x 256 switching fabric operating at 2.5 Gbit/s and its performance is evaluated by means of simulation in a random and bursty traffic environment. It is demonstrated that a multi- plane configuration of optical matrices followed by an efficient concentration strategy is capable of meeting the target ATM requirements, that is cell loss probability less than 10” with load up to 0.8. A detailed design of the switch and its complexity evaluation are also given.

1. WTRODUCTION

Emerging multimedia, high-speed data and imaging applications are going to generate huge aggregate traffic and demand for the public network to be able to deal with a wide spectrum of data rates [I , 2, 31. To meet these requirements the international standard bodies have proposed the new telecommunication standard known as Asynchronous Transfer Mode (ATM) [4]. ATM provides a multiplexing and switching method common to all kinds of services and based on the fast packet switching technique. Thus many research activ- ities have been developed in recent years on the imple- mentation and performance evaluation of multiplexers and switches that support the new transfer mode [4, 5, 61. In particular as regards switching, many architectures have been proposed mainly for electronic implementa- tion 14, 5 , 6, 71, where main limitations to the switching element size are imposed by pin count, memory speed, power dissipation, depending on the particular solution adopted [8]. So, large ATM switches (10000 - 100000 access lines), required in the future B-ISDN core net- work for switching about 1 Tbiu‘s of traffic [7, 8, 91,

hardly will be implemented by means of a single, mono- lithic switching element and thus switching fabric archi- tectures based on the interconnection of basic limited- size building blocks must be investigated.

The implementation of high performance switches ex- ploiting the large amount of bandwidth available in the optical domain has gained increasing interest in the re- cent literature [lo]. In this environment, due to the high capacity of optical links, a large switch is one with some hundreds of input and output links operating at very high speed, so that the required 1 Tbit/s can be supported. However, such a switch will not be implemented with a single, monolithic, photonic switching element either.

In general, a broadband switching node consists of a set of link interfaces, which perform signal regeneration, clock synchronization and cell delineation, and of the switching fabric itself, which is responsible for the rout- ing functions. In particular, on one hand it appears fea- sible to implement high speed switching fabrics with state of the art optical technology to increase performance and simultaneously to remove critical limits of large electron- ic systems, such as problems caused by dense intercon- nections, electromagnetic interference and power con-

Vol. 7. No. 6 November - December 1996 565

Jean-Baptiste Jacob, Maurizio Casoni, Giorgio Corazza, Carla Raffaelli, Francesco Masetti, Pierre Pamentier

sumption. On the other hand, purely high speed photonic switching is today limited by the difficulty of synchronis- ing, decoding and buffering cells directly in the photonic domain. The buffering function, necessary in a packet switch, can be provided in several ways using optical equipments, even if capacity is somewhat limited because optical memories capable of large data storage have not yet been realised. Cell processing on inputs, including header reading and decoding, can be partially realised with state of the art optical technology. However, the cur- rent electronic-oriented ATM cell format requires neces- sarily electronic interfaces, especially for ATM cells transported within SDH frames, whilst the core of the ATM switch may be electronic or optical. This suggest that ATM switching fabrics could evolve to become all- optical switches, but a substantial amount of electronics will remain in the short term to perform complex func- tionalities usually required, such as traffk concentration, multiplexing and bit rate increase, packet header process- ing. Photonic memories and processors, when available, will bridge this discontinuity finally providing real cus- tomer-to-customer all-optical transport.

Implicitly, it is assumed in the following that the switch internal operating mode is synchronous and time-slotted, with the time slot duration at most equal to the external link cell transmission time. At the link interface an elec- tronic cell processor handles the incoming cells perform- ing synchronisation and link level protocol functions. Memory can be added within these electronic interfaces in order to relax some buffering constraints of the switching fabric. Thus, different internal dimensionings can be ob- tained, depending on further buffering and concentration at the output of the fabric are realised whether electrically (with electrical buffers) or optically (with optical buffers).

As regards the interconnection of switching elements, regardless of the technology adopted, several options are available [6], mainly based on the organization of switching elements in multistage configurations [4, 8, 11, 121. Unfortunately an interconnected ATM switch- ing fabric tends to show a worse cell loss rate than a single ATM switching element of the same size because of its internal congestion. In order to prevent the in- crease in cell loss some additional features might be added to the interconnected switch, such as interstage flow control and internal speed-up.

In this paper we refer in particular to the Fibre Delay Line switching element [13], developed in the frame- work of the RACE project ATMOS, which consists of a photonic switching element capable of supporting at present-day 16 inputs and 16 outputs and operating at 2.5 Gbit/s [13, 14, 15, 161. Output queuing is provided inside the switching element, with a queue size up to 16 cells for each output, growable to 32 cells in the near future. By assuming such an element as a building block, multi-stage, multi-plane interconnection net- works based on the Clos topology [ 121 are investigated and several design options are discussed with the aim to meet ATM switching requirements [4].

The design of a 256 x 256 switching fabric is described and its performance evaluation obtained by simulation, under the assumption of uniform traffic, taking mainly into account cell loss probability as a performance figure. The assumption of Bernoulli input traffic can be regarded as a good approximation for the superposition of a large number of individual constant bit rate traffic streams on an optical link [17]. Moreover, bursty traffic is considered to evaluate its effect on switching performance. The tar- get ATM requirement to be obtained is a cell loss in the range of 10-9 tol0-10 with an average load up to 0.8 on external links. The influence of different architectural op tions on performance is discussed and the matching with the target proved as much within the constraints imposed by present-day photonic technology as possible.

This paper is organised as follows. Section 2 deals with the description of the photonic switching element with output queuing, presenting first a description of the implementation and then a brief review of output queuing performance. In section 3 the interconnection of switching elements is discussed and the solutions adopted for our proposal outlined. In section 4 the traf- fic analysis, obtained by simulation, of a 256 x 256 switch is presented as a function of the available design options and within the present-day technological con- straints. A switch design is then given in section 5 . Con- clusions of the paper are presented in section 6 .

2. A PHOTONIC SWITCHING ELEMENT WITH OUTPUT QUEUEING: THE FIBRE DELAY LINE SWITCH

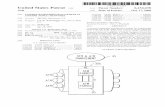

The Fibre Delay Line (FDL) switching element (SE) [2, 14, 161 is illustrated in Fig. 1 for N inputs and N out- puts. It consists of an all-opticaI, high-speed routing network electrically controlled, realised with state-of- the-art photonic technology.

The internal operating mode of the whole switch is assumed to be synchronous and time-slotted, with the time slot duration at most equal to the external link cell transmission time. Thus, at the link interface a cell pro- cessor is required to perform the synchronisation and the link level protocol functions on incoming cells: a n

Gated-Access Call Encoder Shufne Network

B o p t i c a l Gate Opt. Filter Fibre Delay Detector

Fig. 1 - Schematic diagram of the N x N photonic switching element.

566 E?T

System Design and Evaluation of a Large Modular Photonic ATM Switch

bit tag is generated for internal routing purposes and added to the cell, to be used by the SE electronic control logic to select the requested outgoing link.

The main system design parameters of the SE are the number N of inputs and the buffer capacity Q per out- put. The SE consists of three different functional units:

- the wavelength routing unit, located at both ends of the SE, which in turn can be split into a set of wavelength converters (which assign to each in- coming cell the wavelength associated with its tar- get outlet), one star coupler (which mixes all the wavelength-encoded cells); one demultiplexing stage, based on a set of N fixed-wavelength band- pass optical filters (which enable each outlet to se- lect only the cells addressed to it);

- the optical buffer, located at the centre of the SE, based on a set of Q optical fibres and accessible via an optical splitting-combining gated network composed of N splitters, N . Q electro-optic gates and Q combiners. Cells are shifted by an appropri- ate number of time slots, to avoid output colli- sions, the delay introduced by the q-th fibre being equal to q time-slots [0 5 q 5 (Q - 1) TI [18];

- the routing and control logic, essentially based on an electronic command memory, drives the wave- length converters (routing function) and the N . Q optical gates (queuing function) using informa- tions contained in the cell internal tags, processed all simultaneously at each time slot.

As we assumed, the incoming cells arrive in phase at the N inlets, with their associated n bit tags already add- ed. While the tag is being read, each cell is delayed in a suitable length of fiber, with a transit delay duration of less than a time slot. The routing information resulting from the electronic analysis of the tag is used to tune the converter on the appropriate wavelength. Thus at the output of the converters the cells have been encoded at the wavelength corresponding to their destination.

Collisions between synchronous cells with identical wavelength are resolved by means of the optical buffer. It consists of a set of Q optical fibers used as delay lines, with increasing lengths corresponding to relative propa- gation times of 0 x T up to (Q - 1) x T, where T is the time slot duration at a given speed. The output of each wavelength converter is connected to all the Q fibers via a 1-to-Q splitter and a set of Q electro-optical gates, interconnected to form a gated splitting-combining net- work, since each fiber can support up to N cells at differ- ent wavelengths in the same time slot. Wavelength divi- sion multiplexing is used to physically share the fibers between the logical queues, in order to minimise the re- quired amount of optical hardware. On the other hand, one wavelength-encoded cell only must enter one delay line at each time-slot and, for this purpose, a contention resolution logic is implemented to determine the queuing order between the contending cells. Out-of-sequence of

the cells within the buffer is impossible, if we assume that only cells belonging to different connections enter the switching fabric in the same time slot.

The buffer management is quite simple: one cell queue is logically associated with one SE outlet. This realises a pure output queuing architecture, where Q is determined on the basis of quality of service considerations, given N and the load. The electronic control logic manages the queues with a FIFO discipline using pointers assigned to each outlet, scanning and serving sequentially the inlets. Each pointer is then incremented by one when a cell en- ters its queue, and decreased by one when a cell leaves it. The pointer register gives the number i (0 S i S Q - 1) of the fiber to which each cell must be transferred, which al- so identifies the gate to be activated. If i 2 Q, the cell(s) exceeding the buffer capacity is (are) lost.

Finally, the time-switched cells can propagate to- wards the different SE outlets, because the outputs of the delay lines are combined and broadcast to all the outlets, by means of an optical star coupler. Each outlet is equipped with a fixed-wavelength optical bandpass filter, whose transmission peak is tuned to one of the N possible cell wavelengths. Thus each filter receives all the cells, but selects only the appropriately encoded cell stream destined to its outlet.

The SE feasibility has been demonstrated with state- of-the-art photonic technology: a rack-mounted, re- duced size demonstrator has been realised and operated error-free at 2.5 Gbitk [14]. However, physical limita- tions of current optoelectronic devices introduce imple- mentation constraints, thus limiting the practical SE size and performance [ 13, 14, 15,201. The maximum size of the SE must be determined on the basis of power budget considerations, to avoid degradation of optical signals leading to remarkable penalties at the detection side. Basically these impairments result from: the combined effect of non-ideal wavelength conversion, gating and filtering, (leading to degradation of the signal extinction ratio); the accumulated noise (coming from amplified spontaneous emission of the amplifiers); the non-ideal synchronisation of the output signals (resulting from the internal differential path delays) [13, 151.

A fully-equipped demonstrator of a 4 x 4 FDL switch- ing matrix with 4 memory positions, has been imple- mented and mounted in a rack [14]. The different all-op tical components were integrated on separate boards and special care was paid to balance the optical paths of the matrix so that a11 signals were synchronized to within i 4 0 ps. The key functionalities of routing and time- switching of 2.5 Gbit/s cells were demonstrated with ex- cellent overall system performance while exploiting the full 4 x 4 matrix and running error-free (bit error rates < 10-13). We present in Fig. 2 the results obtained in a switching configuration exploiting the four All Optical Wavelength Converters (AOWCs), the four FDLs and the four outputs. It can be seen, first, that the minimum sensitivity is about 2 dB with respect to back-to-back (BtB), and second, that the sensitivity variations from

Vol. 7 , No. 6 November - December 1996 567

Jean-Baptiste Jacob, Maurizio Casoni, Giorgio Corazza, Carla Raftaelli, Francesco Masetti, Pierre Parmentier

I 0-5

106

10-7

; lo-8

2 : 10'9 5

10-10

lo-"

10-'2

1

1 ' 1 3 I ' I ' I ' I ' I

-35 -30 -25 -20 -15 -10 -5 5 Received Power (dBm)

Fig. 2 - Fibre Delay Line matrix demonstrator EER curves in a 4 x 4 cell-switching experiment at 2.488 Gbir/s (using all-optical converters).

one output to the other are contained within less than 5 dB. These sensitivity variations are due mainly to the power discrepancies recorded at one output between con- secutive cells originated from different sources and expe- riencing different optical paths throughout the ma- trix.The demonstrator (Fig. 3) was presented for the first time at the ECOC '93 exhibition in Montreux.

Using the first generation components (current tech- nology) from this 4 x 4 demonstrator, modelling on the basis of experimental results has shown that the optical signal-to-noise ratio in a 16 x 16 configuration could be close to unacceptable limits, due mainly to the accumu- lation of spontaneous emission noise from the all-opti- cal gates. With new gates capable of operating at a higher output level [21] it is possible to overcome this limitation, especially when, in addition, interferometric all-optical wavelength converters capable of signal ex- tinction ratio regeneration are used [22].

Fig. 4 summarises the influence of the main expected technological improvements on the overall system per-

Fig. 3 - The fibre delay line matrix demonstrator.

568

-40 -35 -30 -25 -20 Received Power (dBm)

Fig. 4 - Influence of the main expected technological improvements on the overall EER performances for a 16 x 16 matrix.

formances of a 16 x 16 switching matrix, giving the BER curves for both currently used technology and improved one. In particular, adopting optimised all-optical wave- length converters [22] the output extinction ratio can be enhanced from 10 to 13 dB while it is foreseen that the coupled noise factor of the semiconductor optical ampli- fier gate could be reduced from 10 to 6 dB. The figure shows that this translates into both the reduction of the sensitivity penalty and the suppression of any measur- able BER floor, thereby yielding larger operating mar- gins of the system, especially needed when several ma- trixes are cascaded in multistage architectures.

To realise a large, high throughput switching fabric in a modular way, the effect of cascading and interconnect- ing several SEs must be evaluated with care, from both the optical and the traffic performance point of view. The cascadability of elementary modules has been phys- ically investigated and shown to be technologically fea- sible, in particular as regards signal regeneration with re- spect to optical noise and extinction ratio. Numerical calculations have been performed, based on the charac- teristics of existing optoelectronic components, thereby following a somewhat conservative approach [ 151. These calculations show that the cascadability of SEs ar- ranged in a multi-stage configuration seems feasible without great sensitivity penalty, provided that extinc- tion ratio regeneration is performed at each stage.

Concerning the optical buffer, 16 positions is the opti- mal trade-off. However, from the FDL standpoint, no particular constraints or drawbacks appear in large buf- fers (e.g. 32-64 positions), except the volume of a large fiber amount. However, the required fiber amount can be considerably reduced by adopting a binary tree-shape as- sembly [ 191. The major constraint is instead the buffer flexible operation, since the signal optical power is af- fected by the shuffle network design and characteristics, thus resulting in a global limitation of N . Q or in a large number of active components. A serial cascade of buffer

E-IT

System Design and Evaluation of a Large Modular Photonic ATM Switch

modules could be a possible solution to this problem. Fi- nally, if the buffer temperature is carefully controlled, ex- perimental results have shown path equalisation differ- ences less than 20 ps (modulo r ) which correspond to less than 1/20 of the bit duration at 2.5 Gbit/s [19].

Performance of SEs with output queuing have been widely studied for random traffic [23, 241. As regards cell loss, it has been shown that a weak dependence on switching element size exists, while load and buffer length show significant influence on cell loss. Evalua- tions have been made using [24] as analytical model, showing that the present-day queue size limitation makes the switching element not suitable to match ATM switching requirements. Thus, some additional strategies have been investigated together with SE interconnec- tions to satisfy switch size and traffic requirements.

3. INTERCONNECTION OPTIONS

Different options are available in the organization and operation of interconnected modules to form a large switching fabric [ 5 ] . The main issues concern the switch- ing fabric topology, the routing policy, the introduction of interstage flow control and are discussed in the following:

- fabric topology: the organization of SEs may allow single or multiple paths for each input/output pair. A well known example of single path interconnec- tion is represented by the r-delta banyan network that has been widely considered in broadband switching architectures for its nice self routing prop erty which made it suitable for fast switching. How- ever, this banyan network has poor performance by itself, so that practical solutions for ATM switching adopt additional strategies involving queueing and redundancy [5] . An example of multiple path inter- connection is represented by the CIos interconnec- tion, widely used in the past for circuit switching applications [12]. Design freedom degrees are here represented by the number of stages and by the number of switching elements at each stage, which may be exploited for performance tuning of the interconnected SEs. In order to match ATM traffic requirements, parallel organization of interconnect- ed matrices may be considered, regardless of the

Output i Plane # 1

Output i Plane # 2

Output i Plane # 3

Output i Plane # 4

Fig. 5 - Concentration with 2-stages.

particular interconnection strategy adopted for each matrix [25]. Let us refer to each interconnection ma- trix as plane. When multiple parallel planes are adopted a concentration function is necessary on output to collect cells for the same destination com- ing from different planes. This concentration may be also organised in a multi-stage configuration both for easier implementation and for performance enhancement. For instance, Fig. 5 shows a logical diagram of a multistage concentration for 4 planes.

- routing policy: when multiple paths are available, due to the interconnection strategy and to parallel planes, the policy for the choice of a particular one may influence switch performance. It is assumed that this choice is made at the call level and then all cells belonging to the same call follow the same path. Since our evaluations are focused on the cell level, a random choice of alternative routes is per- formed, being sufficiently representative of the highly multiplexed streams we deal with.

- interstage flow control: cell flow throughout the switch from stage to stage can be controlled in or- der to decrease or to avoid the cell loss in the SEs due to buffer overflow. The ideal back-pressure mechanism may consist, for instance, in a signal backwarded by a full buffer to all SEs in the pre- ceding stage in order to stop cell transfers: thus, cell loss may occur only at the first stage. This technique has been shown to remarkably improve the overall switch performance [26]. However, it is worthwhile noting that this interstage flow control is not supported by the FDL SE implementation yet. In fact, since a cell is given a fixed delay (i.e. it is assigned to a specific FDL) on its arrival at the SE, it cannot be further delayed as required by interstage flow control. However, the next genera- tion SE will be able to support this technique [27].

A 3-stage Clos organization is here considered to take advantage from multiple paths. A design freedom degree is thus represented by the number of SEs at the second stage. This architecture is also expanded in a multiplane configuration in order to improve switching fabric perfor- mance [26]. The overall switch organization is sketched in Fig. 6 . Both the number H of intermediate stage switching elements and the number R of planes are limit- ed by technological constraints and complexity criteria. Feasible values are H up to 16 and R up to 4. Different concentration strategies are considered as an extension of [26]. For example in the case of R = 4 two-stage concen- tration is expected to obtain better performance.

In the architecture of Fig. 6 cells arriving at each in- put link are randomly distributed onto the R planes. In- side each plane multiple paths are available for each in- put/output cell transfer: a random choice of one of them is performed inside the switching elements at the first stage and that is an acceptable assumption for perfor- mance evaluation at the cell level.

Voi. 7. No. 6 November - December 1996 569

Jean-Baptiste Jacob, Maurizio Casoni, Giorgio Corazza, Carla Raffaelli, Francesco Masetti, Pierre Pamentier

Fig. 6 - Replicated networks with Clos configuration on each plane.

4. TRAFFIC ANALYSIS

This analysis is mainly developed assuming Bernoul- li traffic on all input links, with the aim to dimension the switch and, in particular, the optical buffers in the SEs and in the concentrator to satisfy ATM require- ments. Evaluations are performed by simulation in or- der to obtain sufficiently accurate results. In fact, output buffers introduce correlation in traffic thus making ana- lytical models inexact, due to the approximation re- quired to limit their complexity. Moreover, the flexibil- ity offered by the simulation program developed allows quite easy evaluation of the introduction of new strate- gies for system organization and operations. Statistics are performed on about lo8 cell durations and have been collected on a 20 MIPS workstation to evaluate cell loss probability in the range of 10-6 - lo-' in a rea- sonable computing time, with a 95% confidence inter- val calculated with the t-distribution method. Linear ex- trapolation of results is considered, when possible, to evaluate probabilities in the range of 10-9 - 10-lo.

The study of the single plane performance is the first step for the design of large switches. The output queue length Q is extended to 20 cells, being this value ex- pected in a very near future. A Clos interconnection of SEs is considered on each plane. For the sake of this discussion, let us define as interconnection without ex- pansion a 3-stage Clos organization of SEs with the same number of SEs at each stage. On the other hand an interconnection with expansion provides at the interme- diate stage a greater number of SEs than at the first

1 e+CQ

le-01

18-02

18-03

le-04

8 le-05

3 le-06

1 e-07

1 e-08

1 e-09

2. 3

YI

-1

3 5 7 9 11 13 15 17 20 SE Buffer Size Q

Fig. 7 - Cell loss probability as a function of Q varying the input load as a parameter for a switch without expansion, with 16 x 16 SEs at the tint stage.

stage. Moreover let us consider, as acceptable perfor- mance, cell loss probability less than 10-9 with load up to 0.8. Switch sizes up to 256 x 256 are here consid- ered. It has been demonstrated that no relevant differ- ence exists among 32 x 32, 64 x 64 and 256 x 256 switches, so that most of the following considerations are independent on the switch size [28].

Fig. 7 shows the performance of a 32 x 32 switch with 16 x 16 elements at the first stage, no expansion and so sixteen 2 x 2 SEs in the second stage, without flow control mechanisms. In order to have an efficient implementation, 2 x 2 SEs may be physically mapped within 16 x 16 modules. Under these conditions, ac- ceptable performance can be obtained within the fea- sible output buffer length Q only by limiting the traffic (average load < 0.5).

Fig. 8 shows a 32 x 32 switch with expansion com- pared with the previous one. Here four 8 x 16 SEs are at the first stage, sixteen 4 x 4 SEs at the second stage and four 16 x 8 SEs at the third stage. In this case, expansion does not decrease significantly the cell loss probability.

1 a-01

10-02 0

le-03 8 .I e-04

8 16-05 a

..... ......... ..... ......... ......... ....... I , ; I -;...- ....................

-1 le-06 ... ...-....................-.-......,.....-..-.....,......-..

le-07 . 1 e-09

.___ ..__ _ _ _ _ _ _ _ _ . 1 __._______ . _._ ....._. i ._.___._. :...- .____ ;..-. _____.____ _ _ _ ____.. I ,

, I I ,

0

._ .._... . ......._....__.__._.____.____ ................. -..L.... .......... ~ .._.._.. : : , , . ,

, , * . : : ,

3 5 7 9 11 13 15 17 20 SE f3uffer Size Q

Fig. 8 - Effect of expansion on cell loss probability as a function of Q. for a 32 x 32 plane, load = 0.8.

Fig. 9 shows the contribution to cell loss given by different stages for different Clos configurations. It can be seen that congestion is shifted from the first to the last stage by increasing the internal expansion. This ob- servation lead to the conclusion that a technique to bal- ance load throughout stages might improve buffer util- isation and so switch performance in the presence of

&WE-02

8.40E-02

o' ! 4.80E-02

4 3.20502

3 1.60E-02 0

O.OOE+M) 2 3 1

Stage

First Stage SE 16x1 6 0 First Stage SE 8x16 Erst Stage SE 4x16

Fig. 9 - Cell loss distribution throughout stages without back-pres- sure, for a 32 x 32 plane, load = 0.8, Q = 3.

570 ETT

System Design and Evaluation of a Large Modular Photonic ATM Switch

le+W , 1 Load = 0.8 + Load = 0.5 +

.......... .......... ........................................ 8 , I ,

I . ........ ....... i ) b - le.O1

........................ ...................................................... . 1 e-07 ......... i _ _ _ _ _ _ _ _ _ _ ~ .......... .......................................... 1 eJ-J8 ......... ..........................................

I 2 4 6 8 18

SE Buffer Size Q

Fig. 10 - Cell loss probability as a function of Q for different values of load, for a 256 x 256 switch, buffer size equal to 16 in the concen- tration stage and R = 2.

internal expansion. This can be achieved by the intro- duction of interstage flow control [261.

Fig. 10 shows the sensitivity to the SE buffer size of cell loss probability for a 256 x 256 switch and two dif- ferent traffic load values in the case of R = 2 parallel planes; 16 x 16 SEs are considered as basic building blocks. A saturation effect limits the switch performance with heavy load because of the combined effect of speed- up introduced by replication and limited size of the con- centration buffer. Cell loss as a function of the buffer length in the concentration stage is then studied and plot- ted in Fig. 11. Evaluations for R = 2 and R = 4 are pre- sented, showing that the former is better when no inter- stage flow control is applied. The performance target can be reached only for concentration buffer sizes that over- come the present-day technology constraints unless limi- tation on load is introduced. For instance, with load equal to 0.8, the concentration buffer size required is about 45 cells, if the curve is extrapolated down to 10-9.

1 ; Load=O.8 +

4 6 8 TO 12 14 16 18 20 22 24 26 Buffer Size in the Concentration Stage

Fig. 11 - Cell loss probability as a function of the buffer size in the concentration stage for Q = 16, different values of load and R.

Another design option that has been investigated is the multistage concentration of Fig. 5 made up of 2 to 1 hierarchical optical concentrators that can be applied starting from R = 4. The multistage structure for concen- tration is expected to give better performance due to the greater amount of storage available for each cell path. In Fig. 12, two stage concentration is introduced and the

- .- H le-03

E le-06

n g le-04 a

le-05 J

1 e-07

1 e-08

1 e-09 ~~~

1 2 4 6 8 10 12 14 16 18 20 22 24 26 Second Stage Buffer Size

Fig. 12 - Cell loss probability as a function of the second stage buffer size, 256 x 256 switch, 16 x 16 SEs, different first concentration stage buffer sizes, Q = 16, load = 0.8 and R = 4.

cell loss is evaluated as a function of the second stage buffer length varying first stage buffer length as a pa- rameter. A saturation effect is still present if the first stage buffer is not large enough, because loss occurs mainly in the first stage. In the range of our performance target, it can be reasonably assumed that this effect is no more present when the first stage buffer size is 16 cells. Fig. 13 shows the cells loss probability as a function of the buffer size in the second stage of the concentration stage, once the buffer size in the first stage is fixed equal to 16 cells. The basic result here is that with a load equal to 0.8 a second stage buffer size equal to 22 cells is enough to obtain a cell loss equal to l e 9 and this buffer length is optically feasible in the very near future. On the other hand, loads up to about 0.7 can be supported with present-day 16 cell buffers. It is worthwhile noting that the buffer size required for second stage buffer with four parallel planes is about half the buffer size required with one stage concentration and two parallel planes. This reduction may appear surprising, being the average load at the input of last concentration stage the same in the two compared situations. The reason of this reduc- tion lies in the different traffic patterns that load the last concentration stage: in fact, as a consequence of higher plane loading for two parallel planes, traffic on the out- put links results more bursty in the latter case. The eval-

l*oO

le-01 3 le-02 3 le-03 2 le-04 8 le-05

le-06 le-07

.-

, I , . ,

1 ................................................................. , * * , * * . I , , , . . , , . , , , . I : : I : I I : , , , I , , , , le-09 : I * ' I

2 4 6 8 10 12 14 16 18 20 22 24 26 Second Stage Buffer Size

Fig. 13 - Cell loss probability as a function of the buffer size in the second stage. for a 256 x 256 switch, 16 x 16 SEs. Q = 16. first con- centration stage buffer size=16. R = 4 and different load values.

Vol. 7. No. 6 November - December 1996 57 1

Jean-Baptiste Jacob, Mauriaio Casoni, Giorgio Corazza, Carla Raffaelli, Franceseo Masetti, Pierre Parmentier

uation of the traffic variance at the input of last concen- tration stage confirms this consideration.

Evaluations have also been made for bursty traffic, modelled by means of OdOff markovian sources. Two kinds of this traffic have been considered: multiplex bursty traffic, that during On periods carries cells uni- formly addressed to switch outputs, and source bursty traffic where cells carried during the same On period have the same address. The first one is the results of sev- eral multiplexing stages and is more realistic in the envi- ronment considered in this paper, that is transit exchang- es. Source bursty traffic on the other hand is typically present at access mulitplexers or local exchanges. Bursty traffic has been charactensed by means of the average load and the average burst length A. Fig. 14 shows the switch performance for 0.8 average load. It can be seen that performance is significantly worse in the case of source burst but, for multiplex burst, does not signifi- cantly differs from random traffic. This can be explained as a consequence of the demultiplexing effect that takes place throughout the first stages of the switch and that tends to smooth traffic burstiness inside the switch.

1 e-01 .- 2. .- le-02

le-03

8 lep4

P 3

, , * , . , le-05 : ; : I , , I I I

1 2 4 6 8 I0 12 14 16 18 20 SE Buffer Size Q

Fig. 14 - CeII loss probability as a function of Q for 256 x 256 single plane switch, average load = 0.8, different traffic patterns.

5. EXAMPLE OF DESIGN OF A 256 x 256 SWITCHING FABRIC

The design of the switching fabric is here developed in order to match ATM requirements within the fore- seen photonic limitations in the near future. The follow- ing assumptions hold:

- maximum SE size: 16 x 16, - maximum output queue size: 32 cells, - optical concentration of cells on switching fabric

output.

The performance target is:

- cell loss probability less than lP9 , - random input load: up to 0.8.

The switch architecture chosen for the design is com-

posed of four parallel planes with a two-stage concen- tration (Fig. 15). Referring to the results of Fig. 13, the switching fabric design is developed by assuming for the concentration stage the scheme of figure 5, where the corresponding outputs of the 4 planes are coupled in two series of 2 to 1 concentrators, realised by means of 16 x 8 SEs. The computation of the number of 16 x 16 SEs and of the total memory amount is made. As re- gards the former, the first stage of the interconnection network is made of sixteen 16 x 16 SEs to support 256 input links. Being the proposed architecture composed of a 3-stage Clos network on each plane and 4 replicat- ed planes, 192 SEs are needed.

Fig. 15 - Design of a 256 x 256 switch with 2-stage concentration.

As regards the concentration stage, sixty-four 16 x 8 SEs at the first stage and thirty-two 16 x 8 SEs at the second one are necessary. Summarising. the total num- ber of SEs required in the design is 288 .

As for memory requirements, output buffers with 16 cell places have been used in the SEs of each plane so that 12288 cells for each plane and 49152 cells as total for the planes are required. Also, in the first stage of the concentrator output buffers with 16 cell places have been placed, while in the second stage output buffers with 22 cell places are necessary to satisfy the given tar- get, as it has been shown in the previous section. Thus for the 2-stages concentrator 13824 cells are needed. To summarise. 62976 cell places are necessary for the whole switching fabric, which corresponds to about 246 cell places per switch input and 219 cell places per SE.

As a comment to the buffer requirements, it is worth pointing out that a redundant dimensioning has been performed concerning the SE buffer size on planes. Op- timisation can be reached according to the performance target. However, this redundancy may allow a good switch behaviour also in the case of moderate bursty traffic or load fluctuations.

6. CONCLUSIONS

Implementation and performance evaluation of a large photonic switching fabric built up by small-size switch-

572 ETT

System Design and Evaluation of a Large Modular Photonic ATM Switch

ing elements has been presented and the influence of the design freedom degrees available in the parallel Clos ar- chitecture outlined. According to the present-day tech- nology, a detailed design solution is presented for ATM performance matching, consisting of four parallel planes with a two-stage output concentration.

The detailed system design described together with complexity evaluation, further prove the feasibility, from an architectural point of view, of large photonic switching fabrics, which preserve the continuity of the optical path adopting all-optical buffers.

Simulations have shown that parallel multistage system organizations may satisfy ATM cell loss performance tar- get within present-day technology constraints, thus mak- ing these photonic switching fabrics suitable for the imple- mentation of future high-speed ATM all-optical networks.

Acknowledgements

The authors wish to acknowledge the support of the European Economic Community under the contract RACE 2039 ATMOS.

ManuscriDt received on Januarv 17. 199.5.

REFERENCES

M. N. Ransom, D. R. Spears: Application of public gigabit net- works. “IEEE Network Magazine”, Vo1.6, March 1992, p. 30-40.

J . M. Gabriagues, J. B. Jacob: Exploitation of the wavelengrh domain for photonic switching in the IBCN. Proc. ECOC ‘91, Paris, France, Sep. 1991. p. 59-66.

L. Bermeio. P. Parmentier. G. H. Petit: Service characteristics and trafii models in a broadband ISDN. “Electrical Communi- cation”, Vol. 64. No. Z3. 1990. p. 132-138.

M. De Prycker: Asynchronous transfer mode: solution for broad- band ISDN. Ellis-Howood. London (United Kingdom), 199 1.

F. A. Tobagi: Fast packet switch architectures for broadband integrated services digital networks. “Proc. of IEEE”. Vol. 78, No. 1, January 1990, p. 133-167.

W. E. Stephens, M. DePrycker. F. A. Tobagi, T. Yamaguchi: Large scale ATM switching sysrems for B-ISDN- Guest Editori- al. “IEEE Journal on Selected Areas in Communications”, Vol. 9. No. 8. October 1991, p. 1157-1159.

Large scale ATM switching systems for B-ISDN. “IEEE Journal on Selected Areas in Communications”, Vol. 9, No. 8. October 1991.

K. I. Yukimatsu, Y. Shimazu, A. Hiramatsu: A photonic ATM backbone nerwork. Proc. ICC’ 94, New Orleans, LA, USA, May

Special Issue on Broadband Oprical Networks. “IEEE Journal of LightwaveTechnology”. Vol. 1 I , No. 516, May-June 1993.

1994, p. 1346-1351.

[I21 C . Clos: A study of non-blocking switching networks. “Bell Systems Technical Journal”, March 1953, p. 406-424.

[I31 J. M. Gabriagues, J. Benoit, D. Chiaroni, D. De Bouard, P. Doussikre, T. Durhuus, P. Gavignet-Morin, E. Grard, J. B. Ja- cob, J. Jacquet, C. G. Jorgensen, D. Leclerc, F. Masetti, P. A. Pemer, K. E. Stubkjaer: Design, modelling and implementation of the ATMOS project fibre delay line photonic switching ma- trix. “Optical and Quantum Electronics”, Vol. 26, No. 5 , May

[14] D. Chiaroni, P. Gavignet-Morin, P. A. Pemer, S. Ruggeri, S. Gauchard, D. De Bouard, J. C .Jacquinot, C. Chauzat. J. Jacquet, P. Doussibre, M. Monnot, E. Grard, D. Leclerc, M. Sotom, J. M. Gabriagues, J. Benoit, J. B. Jacob: Rack-mounted 2.5 Gbit‘s ATM photonic switch demonstrator. Proc. ECOC ‘93, Sep. 1993, Montreux, Switzerland, Post-deadline paper, ThP 12.7.

[I51 D. Chiaroni. P. Gavignet-Morin, J. B. Jacob, J. M. Gabriagues, J. Jacquet, D. De Bouard, G. Da Loura, C. Chauzat: Feasibiliq dem- onstration of a 2.5 Gbids 16 X 16ATMphotonic switching matrix. Roc. OFCAOOC ‘93, Feb. 1993, San Josb, CA. USA, pap. WD2.

[ 161 J. B. Jacob, J. M . Gabriagues: Commutafeur optique a tris haut debit pour applications ATM. “Commutation & Transmission”.

[I71 J. W. Roberts, J. T. Virtamo:. The superposition of periodic ceIl arrival streams in an ATM multiplexer. “IEEE Transactions on Communications”, Vol. 39. NO. 2. February 1991, p. 298-303.

[IS] F. Masetti, P. Gavignet-Morin: Optical Fibre buffer for high- performance broadband switching. “European Transaction on Telecommunications”, Vol. 4, No.6, November-December

[I91 P. Gavignet, F. Masetti, D. Chiaroni, J. B. Jacob: Design and implementation of a fiber delay line optical buffer for multi- Gigabit photonic switching fabrics. To appear on European Transaction on Telecommunications.

[20] D. Chiaroni, P. Gavignet. A. Jourdan: Theoretical feasibility analysis of a 256 x 256 ATM optical switch for broadband ap- plications. Proc. ECOC ‘93, Montreaux, Switzerland. Sep. 1993, p. 485-488.

[21] D. Chiaroni. D De Bouard. P. Doussiere, C. Chauzat, M. Sotom: High performance semiconductor optical amplifier gate for fast WDM packer switching. Proc. ECOC ‘95, Brussels, Belgium, September 1995, p. 115-1 18

[22] C. Braagaard. S. L. Danielsen, P. Doussiere, T. Durhuus, M. Er- man. G. Garabedian, C. Graver, J. Jacquet. C. Joergensen, A. Jourdan, D. Leclerc, B. Mikkelsen, R. J. Pedersen, K. E. Stubk- jaer. M. Vaa: Optical wavelength converters. “Proceedings o f ECOC ‘94”, Firenze, Italy, September 1994, Vol. 2. p.635-642 .

[23] A. Gravey, J. R. Louvion, P. Boyer: On the Geo/D/l and Geo/D/l/n queues. “Performance Evaluation”, VoI. 1 I , No. 2,

[24] M. G. Hluchyj. M. J. Karol: Queueing in high-performance packet switching. “IEEE Journal on Selected Areas in Commu- nications”, Vol. 6, No. 9. December 1988, p. 1587-1597

[25] G. Corazza, C. Raffaelli: Input‘output buffered replicated ban- van networks for broadband switchinp aoolications. “Eurowan

1994, p. 497-516.

N. 2, 1994, p 5-14.

1993. p. 671-679.

1990.~. 117-125.

iransactions in Telecommunicationsz, qol. 4, No. 1, Jan.-‘Feb. 1993, p.95-115.

[26] M. Casoni, D. Chiaroni, G. Corazza, I. B. Jacob, F. Masetti, P. Parmentier, C. Raffaelli: Performunce analysis of a 256 x 256 ATM photonic modular switching fabric. “IEEE BSS ‘95, Poz- nan. Poland,” Apr. 19-21. 1995, p. 101-107.

[27] J. M. Gabriagues. F. Masetti, D. Chiaroni. D. De Bouard. D. Chiaroni, P. Parmentier, M. Casoni. F. Callegati, G. Coraua, C. Raffaelli: Performance evaluation of a new photonic ATM switching architecture based on WDM. Australian Telecommu- nication Networks and Aoolications Conference. Svdnev. Aus- .. - ,

I. Y. Huy: Switching and traflc theory for integrated broad- band networks. Kluver Academic, 1990, cap. 3.

A. K. Gupta. L. 0. Barbosa, N. D. Georganas: Switching modules for ATM swifching and their interconnection networks. “Comput-

tralia, Dec. 11-13, 1995.

[28] M. Casoni, G. Corazza. J . B. Jacob, F. Masetti, C. Raffaelli: Clos architecture for the design of large photonic ATM switch- es. Proc. EFOC&N ‘94, Heidelberg, Germany, June 1994,

er Networks and ISDN Systems”, No 26, 1993. p. 433-445. p.106-110.

Vol. 7, No. 6 November - December 1996 573