SOGANG UNIVERSITY SOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB. Power MOSFETs 2013.01.15 SD Lab....

-

Upload

magdalen-bates -

Category

Documents

-

view

227 -

download

4

Transcript of SOGANG UNIVERSITY SOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB. Power MOSFETs 2013.01.15 SD Lab....

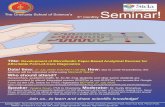

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

Power MOSFETs

2013.01.15SD Lab. SOGANG Univ.

Doohyung Cho

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

Contents

6.6 Power VD-MOSFET On-Resistance• 6.6.1 Source Contact Resistance• 6.6.2 Source Region Resistance• 6.6.3 Channel Resistance• 6.6.4 Accumulation Resistance• 6.6.5 JFET Resistance• 6.6.6 Drift Region Resistance• 6.6.7 N+ Substrate Resistance• 6.6.8 Drain Contact Resistance• 6.6.9 Total On-Resistance• Simulation Example

6.7 Power VD-MOSFET Cell Optimization• 6.7.1 Optimization of Gate Electrode Width• 6.7.2 Impact of Breakdown Voltage• 6.7.3 Impact of Design Rules• 6.7.4 Impact of Cell Topology

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6 Power VD-MOSFET On-Resistance

WCell : pitch for the linear cell geometry WG : width of the gate electrode WPW : width of the polysilicon windowWC : width of the contact window to the N+ source and Pbase regions WS : width of the photoresist mask used during the N+ source ion implantation

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6.1 Source Contact Resistance

• Size of the window in the polysilicon must be minimized to obtain the lowest possible specific on-resistance

• contact resistance (ρC)

WCell : 20um WG : 10umWPW : 10umWC : 8umWS : 4umSource contact = 2um

Amplified by a factor of 5times.

WCell : 15um WG : 10umWPW : 5umWC : 4umWS : 3umSource contact = 1um

Amplified by a factor of 7.5-times.

Increased Source contact resis-tance

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6.2 Source Region Resistance

• Entering the N+ source region from the contact, the current must flow along the source region until it reaches the channel. The resis-tance contributed by the source region is determined by the sheet resistance of the N+ diffusion (ρSQN+) and its length (LN+)

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6.3 Channel Resistance

• Channel length is defined by the difference in the depth of the P-base and N+ source junctions

WCell : 20um Gate bias of 10 V Channel length is 1 μmGate oxide thickness is 500 Å

0.92 mΩ cm2

• Channel resistance can be reduced by decreasing the gate oxide thickness but this is accompanied by a proportionate increase in the input capacitance, which can slow down the switching speed of the power MOSFET structure.

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6.4 Accumulation Resistance

• Threshold voltage in this expression is for the on-set of formation of the accumulation layer

• The accumulation layer resistance can be re-duced by decreasing the gate width

• However, this increases the JFET and drift re-gion resistances

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6.5 JFET Resistance

• If the JFET region is assumed to extend to the bottom the P-base junction, the resistance of the JFET region can be obtained

• The JFET region resistance can be reduced by in-creasing the gate width (WG). however, this in-creases the channel and accumulation layer re-sistances.

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6.6 Drift Region Resistance

Model A Model B

• The drift region resistance can be reduced by increas-ing the gate width (WG). However, this increases the channel and accumu-lation layer resistances.

• Model B predicts a smaller value for the drift region resistance when compared with model A with the 45° distribution angle due to greater current spreading in the drift region.

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6.6 Drift Region Resistance

• The resistance of the drift region is now de-termined by two portions: a first portion with a cross-sectional area that increases with the depth and a second portion with a uniform cross-sectional area for the current flow

Model C

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6.7 N+ Substrate Resistance & 6.6.8 Drain Contact Resis-tance

N+ Substrate Resistance

• Substrate wafer thickness : 500um• typical phosphorus-doped silicon wafer is 0.003 Ω cm• specific resistance contributed by this wafer is 0.15 mΩ

cm2.

Drain Contact Resistance• Before entering the drain electrode, the current flows

through the contact resistance between the drain metal and the N+ substrate

• resistance is not amplified unlike in the case of the source contact.

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.6.9 Total On-Resistance

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

Simulation Example

N-Drift Thickness : 3um(concentration : 1.3x10e16 cm-3)P-base Thickness : 3umN+source thickness : 1umJFET : 1x10e16 cm-3(depth : 3um)

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

Simulation Example

• Additional JFET doping : 2.1x10e16cm-3• Channel length of 1.6um• P-base doping : 1.5x10e17cm-3• Gate oxide Thickness : 50nm• Vth : 3.5V

• The depletion layer width (W0) in the JFET region is 0.24 μm

• constant with a width (a/2) of 3.4 μm. From the JFET region width of 3.4 μm

• current spreads to a width of 6.5 μm at a depth of 6 μm

• current travels a distance of 3 μm

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.7 Power VD-MOSFET Cell Opimization

• It was demonstrated that the JFET and drift region specific resis-tance contributions can be reduced by increasing the width of the gate electrode. Unfortunately, the specific resistance contributions from the channel and accumulation regions increase when the gate width is increased. Consequently, it is necessary to optimize the width (WG) of the gate electrode to obtain the lowest possible specific on-resistance

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.7.1 Optimization of Gate Electrode Width

• analytical model predicts a minimum in the total specific on-resistance for a gate electrode width of 9.5 μm with a value of 1.54 mΩ cm2

• All the major components of the inter-nal resistance within the power VD-MOSFET structure are dependent on the cell pitch.

• drastic increase in the JFET and drift region contributions at gate electrode widths of less than 6 μm

• minimum specific on-resistance occurs at a gate width of 9.5 μm.

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.7.2 Impact of Breakdown Voltage

• it can be seen that the minimum specific on-re-sistance increases and the optimum gate elec-trode width shifts to a larger value when the blocking voltage is increased

• channel resistance becomes dominant in the low voltage power VD-MOSFET structure

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.7.3 Impact of Design Rules

• desirable to reduce the size of the poly silicon window to improve the current distribution within the drift region

• In addition, a reduction of the polysilicon window decreases the cell pitch

• smaller design rules require investment in photolithographic technology with higher resolution

• N+source contact large =>poor contact of P-bacs => drastically diminish the dynamic performance of the device due to creation of an open-base N–P–N transistor

• specific onresistance is reduced from 1.54 to 1.36 to 1.21 mΩ cm2 as the polysilicon win-dow is reduced from 8 to 6 to 4 μm.

SOGANG UNIVERSITYSOGANG UNIVERSITY. SEMICONDUCTOR DEVICE LAB.

6.7.4 Impact of Cell Topology