MOHD. YAMANI IDRIS/ NOORZAILY MOHAMED NOOR1 Sequential Circuit Latch & Flip-flop.

Sequential logic circuits flip-flop pt 1

-

Upload

sarah-sue-calbio -

Category

Education

-

view

1.410 -

download

2

Transcript of Sequential logic circuits flip-flop pt 1

Flip Flops

Sequential logic circuitsCombinational logic circuitSequential logic circuitFlip-flopBuild flip-flop using logic gates1

1

Objectives:Define sequential logic circuit. Differentiate between combinational logic circuit and sequential logic circuit.Describe flip - flop. Identify various types of flip-flops.Build SR and T flip flop using logic gates.Draw the symbol and truth table of SR and T flip flop.

1234562

Sequential & Combinationallogic circuitDefine sequential logic circuit. Differentiate between combinational logic circuit and sequential logic circuit.

123

Difference between Combinational & Sequential logic circuit2Objective

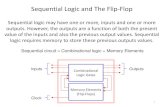

Basic buildingblocks include:Basic building blocksinclude FLIP-FLOPS:Combinational Logic CircuitsSequential Logic Circuits4

Sequentiallogic circuitSequential logic is the type of digital system that does not only depend on current input, but also the previous history of the system.For that reason sequential logic requires memory elements to function.The building blocks used to construct devices that store data are called flip-flops.1Objective

S CRQ

Q'

5

Sequentiallogic circuitThe output of circuit depends on the previous output and the present inputs.The inputs must follow a specific sequence to produce a required output.In order to follow a sequence of inputs the circuits must contain some form of memory to retain knowledge of those inputs, which have already occurred.This memory is obtained by feedback connections, which are made so that history of the previous inputs is maintained.Most sequential circuit elements are known as Bistables or Flip Flops.1Objective

S CRQ

Q'

6

Sequential circuit have loops these enable circuits to receive feedback1Objective

Sequential logic circuit7

Combinationallogic circuitCombinational logic is an interconnection of logic gates to generate a specific logic function where the inputs result in an immediate output, having no memory or storage capabilities.They function only based on their inputs, and NOT based on clocks. 2Objective8

Combinational circuit is combinationof various logic gates

Combinational logic circuit

2Objective9

Flip-Flop

Describe flip - flop.

310

Flip-Flop"Flip-flop" is the common name given to two-state devices which offer basic memory for sequential logic operations. Flip-flops are heavily used for digital data storage and transfer and are commonly used in banks called "registers" for the storage of binary numerical data. 3Objective11

Flip-FlopThey have two stable conditions and can be switched from one to the other by appropriate inputs. These stable conditions are usually called the states of the circuit.They are 1 (HIGH) or 0 (LOW).Whenever we refer to the state of flip flop, we refer to the state of its normal output (Q).More complicated Flip-Flop use a clock as the control input. These clocked flip-flops are used whenever the input and output signals must occur within a particular sequence3Objective12

This is the general flip-flop symbol.

Flip-FlopFlip-flop are basic storage/memory elements.Flip-flop are essentially 1-bit storage devices.Types of flip-flops are:1. SR Flip-flop2. JK Flip-flop3. D Flip-flop4. T Flip-flopApplication of flip-flop:1. Counter4. Logic controller2. Register5. Frequency Divider3. Memory3Objective13

SR Flip-Flop

Identify various types of flip-flops.Build SR and T flip flop using logic gates.Draw the symbol and truth table of SR and T flip flop.

45614

SRFlip-FlopThe simplest binary storage device.SR Flip-flop have 2 inputs (SET & RESET) and 2 outputs (Q & Q).NOTE: Q & Q are complements of each otherThe SR flip flop is sometimes referred to as an SR latch. The term latch refers to its use as a temporary memory storage device.

4Objective

S

RQ

Q'15

SRFlip-FlopThe SR Flip-flop have two inputs, SET (S) and RESET (R)The SR Flip Flop has two outputs, Q and Q.The Q output is considered the normal output and is the one most used.The other output Q is simply the complement of output Q.

4Objective

S

RQ

Q'16

SRFlip-FlopThe most basic Flip-Flop.The basic RS flip flop is an asynchronous device.In asynchronous devices, the outputs are immediately changed anytime one or more of the inputs change just as in combinational logic circuits.It does not operate in step with a clock or timing.These basic Flip Flop circuit can b constructed using two NAND gate latch or two NOR gates latch.SR Flip Flop Active Low = NAND gatesSR Flip Flop Active High = NOR gates

4Objective

S

RQ

Q'17

4Objective

S

RQ

Q'18SRFlip-FlopConstruction:

SRFlip-FlopSymbol:45Objective6

SR Flip-flop (Active HIGH)NOR gateSR Flip-flop (Active HIGH)Symbol19

SRFlip-FlopSymbol:45Objective6

SR Flip-flop (Active LOW)NAND gateSR Flip-flop (Active LOW)Symbol

20

SRFlip-FlopTruth Table:45Objective6SR Flip-flop(Active HIGH)

S

RQ

Q'

S

RQ

Q'

SR Flip-flop(Active LOW)21

Quick RevisionNOR gate & Truth Table:22

SR Flip-FlopCircuit: HOLD/LATCH Mode45Objective623The analysis of a SR Flip Flop NOR:S = 0, R = 0; This is the normal resting state of the circuit and it has no effect on the output states. Q and Q will remain in whatever state they were in prior to the occurrence of this input condition. It works in HOLD (no change) mode operation.

SR Flip-FlopTruth Table: HOLD/LATCH Mode45Objective624

SR Flip-FlopCircuit: SET Mode45Objective625

Consider the input S = 1. Any time the input of a NOR gate is 1 the output is 0. So, the output of the second NOR gate is 0, i.e. Q = 0.Q = 0 is fed back into the input of the first NOR gate. So, with R = 0, the output of the first NOR gate is 1, i.e. Q=1.

SR Flip-FlopTruth Table: SET Mode45Objective626

SR Flip-FlopCircuit: RESET Mode45Objective627Consider the input R = 1. Any time the input of a NOR gate is 1 the output is 0. So, the output of the first NOR gate is 0, i.e. Q = 0.Q = 0 is fed back into the input of the second NOR gate. So, with S = 0, the output of the second NOR gate is 1, i.e. Q=1.

SRFlip-FlopTruth Table: RESET Mode45Objective628

SR Flip-FlopCircuit: INVALID Mode45Objective629S = 1, R = 1; This condition tries to set and reset the NOR gate latch at the same time, it produces Q = Q = 0. This is an unexpected condition and is not used.The two outputs should be the inverse of each other.

SR Flip-FlopCircuit: INVALID Mode45Objective630If the inputs are returned to 1 simultaneously, the output states are unpredictable.This input condition should not be used and when circuits are constructed, the design should make this condition SET=RESET=1 never arises.

SR Flip-FlopCircuit: INVALID Mode45Objective631

4Objective

S

RQ

Q'32SRFlip-FlopOperation:

4Objective33SRFlip-FlopOperation:

AN ANIMATION OF THE FLIP-FLOP PROCESS FOR THE NOR-GATE.

IN THIS ANIMATION, RED SIGNIFIES TRUE AND BLACK SIGNIFIES FALSE. (SOURCE)

SR NOR gate latchTruth Table:45Objective6SR Flip-flop(Active HIGH)

S

RQ

Q'34From the description of the NOR gate latch operation, it shows that the SET and RESET inputs are Active HIGH.The SET input will set Q=1 when SET is 1 (HIGH). RESET input will reset Q when RESET is 1 (HIGH).

SR NOR gate latchTiming Diagram45Objective635Exercise: Determine the output of NOR gate latch with Q initially 1 for the given input waveforms.Example: Determine the output of NOR gate latch with Q initially 0 for the given input waveforms.

SRFlip-FlopTiming Diagram:45Objective6

36

Quick RevisionNAND gate & Truth Table:37

SR Flip-FlopCircuit: INVALID Mode45Objective638The analysis of a SR Flip Flop NAND:S = 0, R = 0; This condition tries to set and reset the NAND gate latch at the same time.It produces Q = Q =1

SR Flip-FlopCircuit: INVALID Mode45Objective639This is an unexpected condition, since the two outputs should be inverses of each other.If the inputs are returned to 1 simultaneously, the output states are unpredictable.This input condition should not be used and when circuits are constructed, the design should make sue this condition.S=R=0 never arises.It is called INVALID/ PROHIBITED

SR Flip-FlopCircuit: INVALID Mode45Objective640

45Objective641The analysis of a SR Flip Flop NAND:S = 1, R = 0; This will reset Q = 0.

SR Flip-FlopCircuit: RESET Mode

45Objective642

SR Flip-FlopTruth Table: RESET Mode

SR Flip-FlopCircuit: SET Mode45Objective643Input, S = 0, R = 1This will set Q = 1.

SR Flip-FlopTruth Table: SET Mode45Objective644

SR Flip-FlopCircuit: HOLD/LATCH Mode45Objective645The analysis of a SR Flip Flop NOR:S = 1, R = 1; This is the normal resting state of the circuit and it has no effect on the output states. Q and Q will remain in whatever state they were in prior to the occurrence of this input condition. It works in HOLD (no change) mode operation.

SR Flip-FlopTruth Table: HOLD/LATCH Mode45Objective646

SRFlip-FlopTruth Table:45Objective6

S

RQ

Q'

SR Flip-flop(Active LOW)47From the description of the NAND gate latch operation, it shows that the SET and RESET inputs are Active LOW.The SET input will set Q=1 when SET is 0 (LOW). RESET input will reset Q=0 when RESET is 0 (LOW).

SRFlip-FlopTruth Table:45Objective6

S

RQ

Q'

SR Flip-flop(Active LOW)48In the prohibited/INVALID state both outputs are 1. This condition is not used on the RS flip-flop. The set condition means setting the output Q to 1.Likewise, the reset condition means resetting (clearing) the output Q to 0. The first row shows the disabled, or hold, condition of the RS flip-flop. The outputs remain as they were before the hold condition existed. There is no change in the outputs from the previous states.The flip-flop memorizes the previous condition.

SR NAND gate latchTiming Diagram45Objective649Exercise: Determine the output of NAND gate latch with Q initially 1 for the given input waveforms.Example: Determine the output of NAND gate latch with Q initially 0 for the given input waveforms.

SRQQ'

00NCNCNo change. Latch

remained in present state.

1010Latch SET.

0101Latch RESET.

1100Invalid condition.

S'R'QQ'

11NCNCNo change. Latch

remained in present state.

0110Latch SET.

1001Latch RESET.

0011Invalid condition.

SRQQ'

00NCNCNo change. Latch

remained in present state.

1010Latch SET.

0101Latch RESET.

1100Invalid condition.

S'R'QQ'

11NCNCNo change. Latch

remained in present state.

0110Latch SET.

1001Latch RESET.

0011Invalid condition.

S'R'QQ'

11NCNCNo change. Latch

remained in present state.

0110Latch SET.

1001Latch RESET.

0011Invalid condition.