Physical Design Arnab

-

Upload

prasanna810243 -

Category

Documents

-

view

226 -

download

0

Transcript of Physical Design Arnab

-

8/11/2019 Physical Design Arnab

1/49

VLSI Physical Design AutomationIntroduction, Partitioning, Floor-planning

VLSI Physical Design AutomationVLSI Physical Design AutomationIntroduction, Partitioning, Floor Introduction, Partitioning, Floor --planningplanning

Arnab Arnab Sarkar Sarkar Dept. of Computer Sc. &Dept. of Computer Sc. &EnggEngg.,.,Indian Institute of Technology Kharagpur Indian Institute of Technology Kharagpur

Advanced VLSI Design Lab., IIT Kgp

-

8/11/2019 Physical Design Arnab

2/49

2 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

VLSI Design CycleVLSI Design Cycle

System SpecificationSystem Specification

Architectural DesignArchitectural Design

Functional DesignFunctional Design

Logic DesignLogic Design

Circuit DesignCircuit Design

Physical DesignPhysical Design

FabricationFabrication

Packaging, Testing andPackaging, Testing and

DebuggingDebugging

X=(AB*CD)+(A+D)+(A(B+C)) Y=(A(B+C))+AC+D+A(BC+D))

-

8/11/2019 Physical Design Arnab

3/49

3 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Physical DesignPhysical Design

Physical design processPhysical design process The process of converting the specification of an electricalThe process of converting the specification of an electrical

circuit calledcircuit called netlistnetlist into a geometric representation called layout.into a geometric representation called layout.

Physical Design AutomationPhysical Design Automation Deals with the research and development of algorithms and dataDeals with the research and development of algorithms and data

structures related to physical design process.structures related to physical design process.

-

8/11/2019 Physical Design Arnab

4/49

4 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

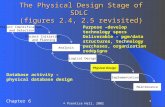

Physical Design CyclePhysical Design Cycle

Stages:Stages:

PartitioningPartitioning

Floor Floor --PlanningPlanning

PlacementPlacement

RoutingRouting

CompactionCompaction

Physical DesignCircuitDesign

(a)

(b)

(c)

(d)

Partitioning

Floorplanning&

Placement

Routing

Compaction

Fabrication

cutline 2

cutline 1

-

8/11/2019 Physical Design Arnab

5/49

5 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Design StylesDesign Styles

FullFull --Custom DesignCustom Design

Standard CellStandard Cell

Gate ArrayGate ArrayFPGAFPGA

-

8/11/2019 Physical Design Arnab

6/49

6 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

FullFull --Custom Design StyleCustom Design Style

Designers can control the shape of all mask patternsDesigners can control the shape of all mask patterns

Designers can specify the design up to the level ofDesigners can specify the design up to the level of

individual transistorsindividual transistors

-

8/11/2019 Physical Design Arnab

7/49

7 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Standard Cell Design StyleStandard Cell Design Style

Selects preSelects pre --designed cells (of same height) todesigned cells (of same height) to

implement logic.implement logic.

-

8/11/2019 Physical Design Arnab

8/49

8 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Gate Array Design StyleGate Array Design Style

Prefabricates a transistor array.Prefabricates a transistor array.

Needs wiring customization to implement logic.Needs wiring customization to implement logic.

-

8/11/2019 Physical Design Arnab

9/49

9 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

FPGA Design StyleFPGA Design Style

Logic and interconnects are both prefabricated.Logic and interconnects are both prefabricated.

Illustrated by a symmetric arrayIllustrated by a symmetric array --based FPGAbased FPGA

-

8/11/2019 Physical Design Arnab

10/49

10 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Comparison of Design StylesComparison of Design Styles

-

8/11/2019 Physical Design Arnab

11/49

11 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Comparison of Design StylesComparison of Design Styles

-

8/11/2019 Physical Design Arnab

12/49

12 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Layout RepresentationLayout Representation

Layout Editor Layout Editor A CAD tool that allows a human designer to createA CAD tool that allows a human designer to create

and edit a VLSI layout.and edit a VLSI layout.

A layout is a collection of tilesA layout is a collection of tiles A tile is a rectangular section within a single layer.A tile is a rectangular section within a single layer. Tiles are not allowed to overlap within a layer.Tiles are not allowed to overlap within a layer. The elements of a layout are referred to as blockThe elements of a layout are referred to as block

tiles.tiles. The area of a block that does not contain a block isThe area of a block that does not contain a block is

referred to as vacant space.referred to as vacant space. Vacant space can be partitioned into a series ofVacant space can be partitioned into a series of

vacant tiles.vacant tiles.

-

8/11/2019 Physical Design Arnab

13/49

13 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Layout Representation ExamplesLayout Representation Examples

-

8/11/2019 Physical Design Arnab

14/49

14 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Data Structures for Layout RepresentationData Structures for Layout Representation

-

8/11/2019 Physical Design Arnab

15/49

-

8/11/2019 Physical Design Arnab

16/49

16 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Atomic Operations for layout EditorsAtomic Operations for layout Editors

Basic Atomic Operations (Contd.)Basic Atomic Operations (Contd.) Directed Area EnumerationDirected Area Enumeration : Given a fixed area: Given a fixed area A A ,,

visit each block intersectingvisit each block intersecting A A exactly once in aexactly once in a

sorted order.sorted order. Block InsertionBlock Insertion : Insert a new block B such that it: Insert a new block B such that it

does not intersect with any existing block.does not intersect with any existing block. Block DeletionBlock Deletion :: Remove blockRemove block BB from layout.from layout. Plowing Plowing : Given an area: Given an area A A and directionand direction d d , remove, remove

all blocksall blocks BB i i fromfrom A A by shifting them in directionby shifting them in direction d d while preserving their order.while preserving their order.

CompactionCompaction : Plowing or compressing the entire: Plowing or compressing the entirelayout.layout. Channel GenerationChannel Generation : Determining vacant space in: Determining vacant space in

layout and partitioning it into tiles.layout and partitioning it into tiles.

-

8/11/2019 Physical Design Arnab

17/49

17 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Corner Stitching Data Structure

A floor with some solid tiles (blocks) are given.

Partition the floor with maximal horizontal strips to define blank orvacant tiles.

For each tile, store its position, size description, and otherattributes.

Insert corner stitches (pointers), 4 per tile (for both solid andvacant) pointing to the appropriate neighboring tiles.

-

8/11/2019 Physical Design Arnab

18/49

18 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Point Finding using Corner StitchesPoint Finding using Corner Stitches

Given a point pGiven a point p 22 , find a path through the corner, find a path through the cornerstitches from the current point pstitches from the current point p 11 to pto p 22 traversing thetraversing theminimum number of tiles.minimum number of tiles.

StepsSteps1.1. Move up or down using theMove up or down using the rtrt or lb pointers until aor lb pointers until a

tile is found whose vertical range contains thetile is found whose vertical range contains the

destination point.destination point.2.2. Move left or right usingMove left or right using tr tr oror blbl pointers until a tilepointers until a tile

is found whose horizontal range contains theis found whose horizontal range contains thedestination point.destination point.

3.3. Whenever there is a misalignment (search goesWhenever there is a misalignment (search goesout of the horizontal range of the tile that containsout of the horizontal range of the tile that containsthe destination point) due to the abovethe destination point) due to the above

operations, repeat steps 1 and 2.operations, repeat steps 1 and 2.

-

8/11/2019 Physical Design Arnab

19/49

19 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Point Finding using Corner StitchesPoint Finding using Corner Stitches

-

8/11/2019 Physical Design Arnab

20/49

20 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

PartitioningPartitioning

The process of decomposition of a large system into independentmanageable subsystems which can be designed independently andconcurrently

Input a set of components or modules a netlist

in the form of a weighted graph or hypergraph: nodesrepresenting modules; edge or hyperedge representing a net

Output a set of subcircuits that when connected, function as the original

circuit terminals required for each subcircuit to be connected to othersubcircuits

-

8/11/2019 Physical Design Arnab

21/49

21 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Levels of PartitioningLevels of Partitioning

-

8/11/2019 Physical Design Arnab

22/49

22 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Partitioning ExamplePartitioning Example

-

8/11/2019 Physical Design Arnab

23/49

23 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

PartitioningPartitioning Problem FormulationProblem Formulation

Given aGiven a hypergraphhypergraph G G = (= ( V V ,, E E )) Vertex = a component.Vertex = a component. HyperedgeHyperedge = a= a net net -- a connection between two components.a connection between two components.

NetNet -- a set of electrically equivalent terminalsa set of electrically equivalent terminals a(v a(v i i ) ) = area of a component= area of a component A(V A(V i i ) ) == a(v a(v ) ) ,, vv V V ii (Area of partition(Area of partition V V i i )) P = {pP = {p 11 ,, , p, p mm } } (set of(set of hyperpathshyperpaths ).).

H(pH(p i i ) = ) = number of timesnumber of times p p i i is cut; affects delay due to partitioning.is cut; affects delay due to partitioning.ObjectiveObjective

PartitionPartition V V into disjoint clusters Vinto disjoint clusters V 11 ,, ,, VVk k , such that cut, such that cut --size andsize andmax(max( H(pH(p i i ) ) ) are minimized.) are minimized.

ConstraintsConstraints Number of terminals in a partition has an upper boundNumber of terminals in a partition has an upper bound Area of each partitionArea of each partition

Number of partitions must be within a rangeNumber of partitions must be within a range

-

8/11/2019 Physical Design Arnab

24/49

24 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

KernighanKernighan --Lin (KL) Partitioning AlgorithmLin (KL) Partitioning Algorithm

A groupA group --migration based algorithmmigration based algorithm starts with an initial partition, generated randomly moves components between partitions to improve

Problem FormulationProblem Formulation Input

An undirected graph G(V,E), |V| = 2n and |E| = m Cost or weight d(a,b) for each edge (a,b) in E

Output Two partitions X and Y such that the total cost of the

cut is minimized, and each partition has n vertices

-

8/11/2019 Physical Design Arnab

25/49

25 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

BipartitionBipartition -- Without HeuristicsWithout Heuristics

Try all possible bisections. Find the best one.

For 2n vertices, # of possibilities = ( 2n Cn) = nO(n)

For 100 vertices, there are 5 10 28 possibilities.

Take 1.59 x 1013

years if one can try 100M possibilitiesper second.

-

8/11/2019 Physical Design Arnab

26/49

26 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

KL AlgorithmKL Algorithm

Start with an initial bisection P = {X, Y};

Repeat repeat

Choose a pair of free cells a X, b Y s.t.exchanging a and b gives the highest gain,gain(a,b);

Tentatively exchange a and b, and lock a and b; Let g i = gain(a,b);

until all pairs are locked; Unlock all vertices; Find k s.t. G = g 1 + g 2 + .. + g k is maximized and

actually exchange cell pairs up to this k th step;

Until G = 0;

-

8/11/2019 Physical Design Arnab

27/49

27 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

KL AlgorithmKL Algorithm -- GainGain

gain( a,b ) = D( a ) + D( b ) - 2 d( a,b ), where d(a,b) = weight between a and b D(a ) = Out( a ) - In( a ) Out( a ) = total weight of all edges of a that cross the bisection In( a ) = total weight of all edges of a that do not cross the

bisection

-

8/11/2019 Physical Design Arnab

28/49

28 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

KL AlgorithmKL Algorithm -- ExampleExample

-

8/11/2019 Physical Design Arnab

29/49

29 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

KL AlgorithmKL Algorithm Complexity & DrawbacksComplexity & Drawbacks

ComplexityComplexity O(cnO(cn 33 ), n ), n is the no. of verticesis the no. of vertices ,, andand cc is no. ofis no. of

passespasses Initial computation ofInitial computation of DD ss O(nO(n ). ). Within a pass, computation of gain for all freeWithin a pass, computation of gain for all free

pairspairs O(nO(n 2 2 ). ).

No. of passes is usually small.No. of passes is usually small.DrawbacksDrawbacks

considers unit vertex weights onlyconsiders unit vertex weights only not applicable tonot applicable to hypergraphshypergraphs partition sizes have to be prepartition sizes have to be pre --specifiedspecified high time complexityhigh time complexity

-

8/11/2019 Physical Design Arnab

30/49

30 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Partitioning OutcomePartitioning Outcome

Output of Partitioning PhaseOutput of Partitioning Phase A set of blocksA set of blocks Area of each blockArea of each block Possible shapes of each blockPossible shapes of each block No. of terminals in each blockNo. of terminals in each block NetlistNetlist specifying the connections between blocksspecifying the connections between blocks

Fixed BlockFixed Block Layout of circuit within block is knownLayout of circuit within block is known hencehence

fixed dimension (shape).fixed dimension (shape).

Flexible BlockFlexible Block Exact dimensions not yet determinedExact dimensions not yet determined

-

8/11/2019 Physical Design Arnab

31/49

31 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

FloorplanningFloorplanning

Input to the floorplanning problem:Input to the floorplanning problem: A set of blocks, both fixed and flexible.A set of blocks, both fixed and flexible. Pin locations of fixed blocks.Pin locations of fixed blocks.

AA netlistnetlist ..

Requirements:Requirements: Find locations for each block so that no twoFind locations for each block so that no two

blocks overlap.blocks overlap. Determine shapes of flexible blocks.Determine shapes of flexible blocks.

Objectives:Objectives: Minimize area.Minimize area. Reduce netReduce net --length for critical nets.length for critical nets.

-

8/11/2019 Physical Design Arnab

32/49

32 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Pin AssignmentPin Assignment

Input to the pin assignment problem:Input to the pin assignment problem:1.1. A placement of blocks.A placement of blocks.

2.2. Number of pins on each block, possibly anNumber of pins on each block, possibly anordering.ordering.

3.3. AA netlistnetlist ..

Requirements:Requirements:1.1. To determine the pin locations on the blocks.To determine the pin locations on the blocks.

Objectives:Objectives:1.1. To minimize netTo minimize net --length.length.

-

8/11/2019 Physical Design Arnab

33/49

33 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

A Slicing FloorplanA Slicing Floorplan

IH

GFED

C

BA

V

H

VVV

V

HH

CB

EDIHGF A

-

8/11/2019 Physical Design Arnab

34/49

34 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

A NonA Non --Slicing FloorplanSlicing Floorplan

E

D

C

B

A

-

8/11/2019 Physical Design Arnab

35/49

35 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

A Hierarchical FloorplanA Hierarchical Floorplan

-

8/11/2019 Physical Design Arnab

36/49

36 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Floorplanning AlgorithmsFloorplanning Algorithms

Floorplanning Algorithms

Rectangular Dual-GraphApproach

HierarchicalApproach

SimulatedAnnealing

-

8/11/2019 Physical Design Arnab

37/49

37 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Rectangular DualRectangular Dual --Graph ApproachGraph Approach

Output of partitioning algorithms represented byOutput of partitioning algorithms represented bya graph.a graph.

Floorplans can be obtained by converting theFloorplans can be obtained by converting thegraph into its rectangular dual.graph into its rectangular dual.

The rectangular dual of a graph satisfies theThe rectangular dual of a graph satisfies thefollowing properties:following properties:

Each vertex corresponds to a distinctEach vertex corresponds to a distinctrectangle.rectangle.

For every edge, the corresponding rectanglesFor every edge, the corresponding rectanglesare adjacent.are adjacent.

-

8/11/2019 Physical Design Arnab

38/49

38 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Rectangular Floorplan & its Dual GraphRectangular Floorplan & its Dual GraphWithout loss of generality, weWithout loss of generality, weassume that a rectangularassume that a rectangularfloorplan contains no crossfloorplan contains no cross

junctions. junctions.

Under this assumption, theUnder this assumption, thedual graph of a rectangulardual graph of a rectangularfloorplan is afloorplan is a planarplanar

triangulated graph (PTG).triangulated graph (PTG).

543

21

543

21

-

8/11/2019 Physical Design Arnab

39/49

39 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

RectangularRectangular FloorplanFloorplan & its Dual Graph& its Dual Graph

Every dual graph of a rectangular floorplan (withoutEvery dual graph of a rectangular floorplan (withoutcross junction) is a PTG.cross junction) is a PTG.

However, not every PTG corresponds to a rectangularHowever, not every PTG corresponds to a rectangular

floorplan.floorplan.

4 3

21

32

Complextriangle

34

21

41

Replace by

-

8/11/2019 Physical Design Arnab

40/49

40 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

DrawbacksDrawbacks

A new approach to floorplanning, in which manyA new approach to floorplanning, in which manysubsub --problems are still unsolved.problems are still unsolved.The main problem concerns the existence of theThe main problem concerns the existence of therectangular dual, i.e. the elimination of complexrectangular dual, i.e. the elimination of complextriangles.triangles.

Select a minimum set E of edges such that eachSelect a minimum set E of edges such that eachcomplex triangle has at least one edge in E.complex triangle has at least one edge in E.

A vertex can be added to each edge of E toA vertex can be added to each edge of E toeliminate all complex triangles.eliminate all complex triangles.

The weighted complex triangle eliminationThe weighted complex triangle eliminationproblem has been shown to be NPproblem has been shown to be NP --complete.complete.

Some heuristics are available.Some heuristics are available.

h l h

-

8/11/2019 Physical Design Arnab

41/49

41 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Hierarchical ApproachHierarchical Approach

Widely used approach to floorplanning.Widely used approach to floorplanning. Based on a divideBased on a divide --andand --conquer paradigm.conquer paradigm.

At each level of the hierarchy, only a small number ofAt each level of the hierarchy, only a small number ofrectangles are considered.rectangles are considered.

A small circuit C, ant all possible floorplans.A small circuit C, ant all possible floorplans.

After an optimal configuration for the three modules hasAfter an optimal configuration for the three modules hasbeen determined, they are merged into a larger module.been determined, they are merged into a larger module. The verticesThe vertices aa ,, bb ,, cc are merged into a super vertex atare merged into a super vertex at

the next levelthe next level

c

c b

a

b aa

a

c b

b

c

dC d

-

8/11/2019 Physical Design Arnab

42/49

42 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Contd.Contd.

The number of floorplans increases exponentiallyThe number of floorplans increases exponentiallywith the number of moduleswith the number of modules dd considered at eachconsidered at eachlevel.level.

dd is thus limited to a small number (typically d

-

8/11/2019 Physical Design Arnab

43/49

43 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Hierarchical Approach :: BottomHierarchical Approach :: Bottom --UpUp

Hierarchical approach works best in bottomHierarchical approach works best in bottom --upupfashion.fashion.Modules are represented as vertices of a graph,Modules are represented as vertices of a graph,while edges represent connectivity.while edges represent connectivity.

Modules with high connectivity are clusteredModules with high connectivity are clustered

together.together. Number of modules in each clusterNumber of modules in each cluster d.d.

An optimal floorplan for each cluster isAn optimal floorplan for each cluster is

determined by exhaustive enumeration.determined by exhaustive enumeration. The cluster is merged into a larger module forThe cluster is merged into a larger module for

highhigh --level processing.level processing.

Hi hi l A h BHi hi l A h B tt UU

-

8/11/2019 Physical Design Arnab

44/49

44 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Hierarchical Approach :: BottomHierarchical Approach :: Bottom --UpUp

A Greedy ProcedureA Greedy Procedure

Sort the edges in decreasing weights.Sort the edges in decreasing weights.

The heaviest edge is chosen, and the two modules ofThe heaviest edge is chosen, and the two modules ofthe edge are clustered in a greedy fashion.the edge are clustered in a greedy fashion.

Restriction: number of modules in each clusterRestriction: number of modules in each cluster d.d.

In the next higher level, vertices in a cluster areIn the next higher level, vertices in a cluster are

merged, and edge weights are summed upmerged, and edge weights are summed upaccordingly.accordingly.

Hi hi l A h B ttHierarchical Approach :: Bottom UUp

-

8/11/2019 Physical Design Arnab

45/49

45 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Hierarchical Approach :: BottomHierarchical Approach :: Bottom --UpUp

ProblemProblem Some lightweight edges may be chosen at higherSome lightweight edges may be chosen at higher

levels in the hierarchy, resulting in adjacency oflevels in the hierarchy, resulting in adjacency oftwo clusters of highly incompatible areas.two clusters of highly incompatible areas.

Possible solutionPossible solution Arbitrarily assign a small cluster to a neighboringArbitrarily assign a small cluster to a neighboring

cluster when their sizes will be too small forcluster when their sizes will be too small forprocessing at a higher level of the hierarchy.processing at a higher level of the hierarchy.

Hierarchical Approach :: BottomHierarchical Approach :: Bottom --UpUp

-

8/11/2019 Physical Design Arnab

46/49

46 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Hierarchical Approach :: BottomHierarchical Approach :: Bottom --UpUp

bb

b

aa

a

dd

d

cc

c

e

e

e

1

1010 3

3

32

Greedy clustering Merging small clusters

Estimating Cost of a FloorplanEstimating Cost of a Floorplan

-

8/11/2019 Physical Design Arnab

47/49

47 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Estimating Cost of a FloorplanEstimating Cost of a Floorplan

The cost of a floorplan is usually estimated from theThe cost of a floorplan is usually estimated from theconnections and the area of theconnections and the area of the floorplanfloorplan ..

The area can be easily estimated because theThe area can be easily estimated because thedimensions of each cluster can be passed up fromdimensions of each cluster can be passed up fromthe bottomthe bottom --up clustering.up clustering.

The area of a particular choice can thus beThe area of a particular choice can thus becomputed for each candidatecomputed for each candidate floorplanfloorplan ..

The cost can be estimated by summing up the edgeThe cost can be estimated by summing up the edgeweights multiplied by the distance between the centersweights multiplied by the distance between the centersof the clusters.of the clusters.

Hierarchical Approach :: TopHierarchical Approach :: Top --DownDown

-

8/11/2019 Physical Design Arnab

48/49

48 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP

Hierarchical Approach :: TopHierarchical Approach :: Top -DownDown

The fundamental step is the partitioning of modules.The fundamental step is the partitioning of modules. Each partition is assigned to a child floorplan.Each partition is assigned to a child floorplan. Partitioning is recursively applied to the childPartitioning is recursively applied to the child

floorplans.floorplans.Major issue here is to obtain balanced graphMajor issue here is to obtain balanced graphpartitioning.partitioning.

kk --way partitioning, in general.way partitioning, in general.Not very widely used due to the difficulty of obtainingNot very widely used due to the difficulty of obtainingbalanced partitions.balanced partitions.One can combine topOne can combine top --down and bottomdown and bottom --up approaches.up approaches.

Apply bottomApply bottom --up technique to obtain a set of clusters.up technique to obtain a set of clusters. Apply topApply top --down approach to these clusters.down approach to these clusters.

-

8/11/2019 Physical Design Arnab

49/49

49 Advanced VLSI Design Lab, IIT KGP Advanced VLSI Design Lab, IIT KGP