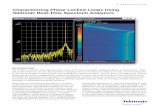

Phase-Locked Loops with Applications

Transcript of Phase-Locked Loops with Applications

Chapter 1Course

Introduction/Overview©2017 Mark Wickert

Contents

1.1 Lecture Outline . . . . . . . . . . . . . . . . . . . . 11.2 This Course and the Phase-Locked Loop Landscape . 2

1.2.1 General PLL Perspective . . . . . . . . . . . 21.2.2 Course Topics . . . . . . . . . . . . . . . . . 3

1.3 Course Perspective in the Comm/DSP Area of ECE . 51.4 Computer Analysis/Simulation Tools . . . . . . . . . 61.5 Instructor Policies . . . . . . . . . . . . . . . . . . . 71.6 Course Syllabus . . . . . . . . . . . . . . . . . . . . 81.7 Required Student Background . . . . . . . . . . . . 91.8 References . . . . . . . . . . . . . . . . . . . . . . . 10

1.8.1 General PLL . . . . . . . . . . . . . . . . . 101.8.2 Synchronization . . . . . . . . . . . . . . . 111.8.3 Journals . . . . . . . . . . . . . . . . . . . . 11

1.9 PLL Highlevel Model . . . . . . . . . . . . . . . . . 121.10 Four Case Studies . . . . . . . . . . . . . . . . . . . 15

i

Chapter 1 Introduction and Overview

1.1 Lecture Outline

� This Course and the phase-locked loop (PLL) Landscape

– General PLL perspective

– Course Topics

� Course perspective in the comm/DSP area of ECE

� The role of computer analysis/simulation tools

� Instructor policies

� Course syllabus

� Required student background

� References

– Books

– Reports

– Journals

� PLL introduction and synchronization applications overview

ECE 5675 Phase-Lock Loops and Synchronization 1–1

Chapter 1 Introduction and Overview

1.2 This Course and the Phase-LockedLoop Landscape

1.2.1 General PLL Perspective

� The focus of this course is phase-lock loops (PLLs) and syn-chronization applications

� At first this may seem like a very narrow course of study, butthe PLL has many applications and many implementation vari-ations

� The use of PLLs for frequency synthesis, i.e., creating a stableyet tunable local oscillator for radio transmitters and receiversis one traditional application area

� In communication systems in general the PLL is widely usedfor synchronization:

– Carrier phase and frequency tracking

– Symbol (bit) synchronization

– Chip synchronization is spread-spectrum systems (this in-cludes GPS receivers)

� Clock recovery is another related topic (same class of problemsas symbol sync)

� The implementation may be:

– All analog electronics (microwave/RF/baseband)

– A hybrid of analog and digital electronics

1–2 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

– A hybrid of analog and software

– Pure software

� The implementation technology may be:

– Board level using RF and baseband devices

– Single chip with a few off-chip or maybe no off-chip parts

– Custom ASIC or FPGA

– A combination of RF and baseband analog with the re-mainder in software via a real-time digital signal process-ing

– Entirely real-time DSP approach if signal samples are ac-quired say using an asynchronous sampling clock; this isthe current state of technology

1.2.2 Course Topics

� PLL fundamentals

– Loop components

– Loop response

– Loop stability

– Transient response

– Modulation response

� Discrete-Time PLL’s

� Performance in noise

– Input noise

ECE 5675 Phase-Lock Loops and Synchronization 1–3

Chapter 1 Introduction and Overview

– Phase noise

– Nonlinear behavior and cycle slipping

� Acquisition

– Unaided

– Aided

� Analog PLL lab experiment (is there interest?)

� Communication applications

– DSP-based carrier phase tracking algorithms

– DSP-based symbol timing tracking algorithms

– Spread Spectrum chip tracking as found in GPS and else-where

1–4 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

1.3 Course Perspective in the Comm/DSPArea of ECE

Sign

als

&

Syst

ems

Mod

ern

DSP

C

omm

Sy

s I

Rea

l-Tim

e D

SP

Com

m

Sys

II

Wire

less

N

etw

orki

ng

Prob

&

Stat

istic

s C

omm

La

b Si

gnal

Pr

oces

s La

b

Stat

istic

al

Sign

al

Proc

ess

Und

ergr

adua

te

Eng

inee

ring

Cur

ricul

um

Sen

ior/1

st Y

ear

Gra

duat

e S

igna

ls &

S

yste

ms

Cou

rses

Ran

dom

Si

gnal

s Sp

read

Sp

ectr

um

Wire

less

&

Mob

il C

om

Opt

ical

C

omm

PLL

&

Freq

Syn

R

adar

Sy

stem

s

Com

m

Net

wor

ks

Sate

llite

C

omm

D

etec

t/ Es

timat

ion

Estim

&

Ada

p Fi

lt

Info

rm/

Cod

ing

Spec

tral

Es

timat

ion

Imag

e Pr

oces

sing

Oth

er G

radu

ate

Sig

nals

& S

yste

ms

Cou

rses

Offe

red

on

Dem

and/

Inde

p. S

tudy

Sp

Sp

Sp

Fa

Fa

Fa(o

dd)

(odd

)

(eve

n)

ECE 5675 Phase-Lock Loops and Synchronization 1–5

Chapter 1 Introduction and Overview

1.4 Computer Analysis/Simulation Tools

� Pencil and paper will work for many problems

� The use of Python (version 3.6 or 2.7 if you insist) and thescipy stack will be emphasized for:

– Analysis and plotting

– Symbolic solutions using sympy

– Simulation

� The new Python package scikit-dsp-comm will be used,and hopefully by the end of the semester more functions willbe added to the synchronization module

– The project can be found on GitHub at https://github.com/mwickert/scikit-dsp-comm

– Installation instructions and tutorial material from Scipy2017avn be found at https://github.com/mwickert/SP-Comm-Tutorial-using-scikit-dsp-comm

– Documetentation is being build on readthedocs at http://scikit-dsp-comm.readthedocs.io/en/latest/?badge=latest

– A set of example Jupyter notebooks is under constructionat https://mwickert.github.io/scikit-dsp-comm/

1–6 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

1.5 Instructor Policies

� Working homework problems will be a very important aspectof this course

� Each student is to his/her own work and be diligent in keepingup with problem assignments

� If work travel keeps you from attending class on some evening,please inform me ahead of time so I can plan accordingly, andyou can make arrangements for turning in papers

� The course web site:

http://www.eas.uccs.edu/~mwickert/ece5675/

will serve as an information source in between weekly classmeetings

� Please check the web site updated course notes, assignments,hints pages, and other important course news

ECE 5675 Phase-Lock Loops and Synchronization 1–7

Chapter 1 Introduction and Overview

1.6 Course Syllabus

ECE 5675/4675 Phase-Locked Loops andDigital Communication Synchronization

Fall Semester 2017

Instructor: Dr. Mark Wickert Office: EN-292 Phone: [email protected] Fax: 255-3589http://www.eas.uccs.edu/~mwickert/ece5675

Office Hrs: Monday 8:00 – 10:40 am and after class as needed, others by appointment.Note: These hours may be adjusted if needed.

Required Texts:

F. Ling, Synchronization in Digital Communication Systems, Cambridge Uni-versity Press, 2017. (ISBN: 978-1-107-11473-9 hardback; e-book available)

Optional Texts:

M. Rice, Digital Communications A Discrete-Time Approach, Prentice Hall,New Jersey, 2009. (ISBN: 978-0-13-030497-1)F. M. Gardner, Phaselock Techniques, third edition, John Wiley, New York,2005. (ISBN: 0-471-43063-3)

Required Software:

Open source Python 3.6 using the Jupyter Notebook (Lab when available). Isuggest Anaconda (https://www.continuum.io/downloads) then install thepackage scikit-dsp-comm using pip or conda see https://github.com/mwickert/SP-Comm-Tutorial-using-scikit-dsp-comm.

Grading: 1.) Graded homework assignments including computer tools totaling 40%.2.) Mid-term Exam worth 25%.3.) Analog and/or DSP-based PLL Laboratory 10%.4.) Final Project/Exam worth 25%.

Requirements: A background in basic communication theory, probability and random variables, and basic digitalsignal processing, i.e. sampling theory is desired. Please contact Dr. Wickert if you are considering this course, butare in doubt as to whether you have adequate background. Items with * will be selected by class interest.

Topics Text Chaptersand Notes

Session (weeks)

1. Introduction/Overview 1 & notes 1.5

2. Initial acquisition and frame synchronization 2 & 3 & notes 1.5

3. Phase-locked loop fundamentals; analog & digital 4 & notes 3.0

4. Analog PLL lab experiment* Handout 1.5

5. PLL tracking performance in noise & phase noise 4 & notes 2.0

6. Unaided and aided acquisition Notes 1.0

7. Carrier synchronization8. Timing synchronization9. Timing control with digital resampling

5 & notes6 & notes7 & notes

1.00.51.0

10. RTL-SDR DSP-based PLL/synchronization experiment* Handout 2.0

1–8 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

1.7 Required Student Background

� Basic linear systems theory is a must

� Random variables is needed for noise analysis

– A brief introduction to random processes will be providedif needed

� Basic modulation theory is also assumed

� A knowledge of digital communication systems is desirable

� A basic understanding of digital signal processing is required

� Knowledge of sampling theory is needed for digital loop con-cepts

� Knowledge of z-domain concepts is required

� The ability to program using Python, particularly the JupyterNotebook (http://jupyter.org) is important for all com-putational aspects of the course; sample notebooks will be postedon the course Web Site

ECE 5675 Phase-Lock Loops and Synchronization 1–9

Chapter 1 Introduction and Overview

1.8 References

The following list of references is not exhaustive by any means, butis a list of core books I have in my library or have been recommendedto me. Some of these books are hard to find since they are now out-of-print.

1.8.1 General PLL1. Heinrich Meyr and Gerd Ascheid, Synchronization in Digital Communica-

tions, Volume 1, John Wiley, 1990.

� This text is basically concerned with analog PLLs (including charge-pump) starting from the very basic concepts all the way through verydetailed nonlinear analysis with noise

� The text also includes material on automatic frequency control (AFC)and automatic gain control (AGC)

� The book is clearly telecommunications based since PLL synthesiz-ers are not considered at all

� Used as the course text in earlier (1990’s offering’s of the course)

2. Alain Blanchard, Phase-Locked Loops: Application to Coherent ReceiverDesign, Wiley, New York,1976. Original course text Dr. Wickert used inhis first PLL course.

3. William F. Egan, Phase-Lock Basics, second edition, John Wiley, 2008.First edition used in 2004 offering of the course.

4. Roland E. Best, Phase-Locked Loops, Theory Design, and Applications,fifth edition, McGraw Hill, 2003.

5. Dan Wolaver, Phase-Locked Loop Circuit Design, Prentice Hall, New Jer-sey, 1991.

6. James A. Crawford, Advanced Phase-Lock Techniques, Artech House, Boston,MA, 2008.

7. Jack K. Holmes, Coherent Spread Spectrum Systems, John Wiley, 1982.

1–10 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

8. Jacob Klapper and John T. Frankle, Phase-Locked and Frequency-FeedbackSystems, Academic Press, New York, 1972.

9. William C. Lindsey and Marvin K. Simon, Telecommunication Systems En-gineering, Prentice-Hall, Englewood Cliffs, New Jersey, 1973.

10. A. J. Viterbi, Principles of Coherent Communications, McGraw-Hill, NewYork, 1966.

11. Rodger E. Ziemer and Roger L. Peterson, Digital Communications andSpread Spectrum Systems, Macmillan, New York, 1985.

1.8.2 Synchronization1. Umberto Mengali and Aldo N. D’Andrea, Synchronization Techniques for

Digital Receivers, Plenum Press, New York, 1997.

2. Heinrich Meyr, Marc Moeneclaey, and Stefan Fechtel, Digital Communi-cation Receivers: Synchronization, Channel Estimation, and Signal Pro-cessing, Prentice Hall, New Jersey, 1998. This is volume II of of Meyr andAscheid.

1.8.3 Journals1. IEEE Transactions on Communications.

2. IEEE Journal on Select Areas in Communications.

3. Other IEEE Journals

ECE 5675 Phase-Lock Loops and Synchronization 1–11

Chapter 1 Introduction and Overview

1.9 PLL Highlevel Model

� In Communication Systems I (ECE 4625/5625) you learn aboutthe basic analog PLL for tracking the phase of a carrier signal:

PhaseDetector

LoopFilter

VoltageControlledOscillator

Analog Multiplier Lowpass Filter

2A ω0t θ t( )+[ ]sin

2A ω0t θˆ t( )+[ ]cos

Phase Error

Control voltage~demod freq.modulation

Tracked input carrier

Figure 1.1: Basic analog PLL (APLL) for tracking the phase of acarrier signal.

� In simple terms the PLL as see above is a nonlinear feedbackcontrol system, which can be linearized under suitable assump-tions

– A big assumption for linearity to hold is that the loop islocked with a small tracking error

� By inserting an analog-to-digital converter (ADC or A/D) theAPLL can be moved into the discrete-time domain with a changeof components:

1–12 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

DigitallyControlledOscillator

2A ω0t θ t[ ]+( )sin

PhaseDetectorADC

Discrete-Time

Loop Filter

2A ω0t θˆ t[ ]+( )cos

fs

n

n

n

n

Figure 1.2: Basic digital PLL (DPLL) for tracking the phase of adiscrete-time carrier signal.

� Fundamentally the PLL is not restricted to carrier phase track-ing

� When the PLL is used to track other waveform attributes, suchas sampling instant under the control of an interpolator, or thetime of delay of a locally generated waveform, as in spread-spectrum, the PLL concept still holds:

ErrorDetector

LoopFilter

Controllable Waveform Generator

F(s) or F(z)r(t) or r[n] e(t) or e[n]

tracked attribute φ̂

attribute φ

Figure 1.3: High-level PLL block diagram.

� What goes on inside the error detector may be very simple orcomplex The requirement of the error detector is provide an s-shaped characteristic that under feedback control can be used

ECE 5675 Phase-Lock Loops and Synchronization 1–13

Chapter 1 Introduction and Overview

to drive the tracking error to zero (with noise to have mean zeroand small variance)

Error Between Input Waveform Attribute and Waveform Generator

e(t) or e[n]

S-Curve

Slope at zero= KED

so we can linearize

Figure 1.4: The general tracking characteristic or S -curve.

1–14 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

1.10 Four Case Studies

� To close out this introductory chapter we now consider fourPython simulation examples

Example 1: Pilot Carrier Phase Tracking in Broadcast FM

� Recall that broadcast FM is a form frequency division multi-plexing, with composite baseband spectrum being composedof a collection of useful signals.

Problem 1: Broadcast FM Demodulator Implementation 13

Part fNext move on to designing the second LPF. Choose under the assumption that you only wantto recover the LCR baseband audio signal. Note: This is a LPF, not a BPF with lower cutoff at 30Hz. Implement the downsample by five so the sampling rate is finally down to 48 ksps. Listen tothe downsampled signal vector by saving the vector as a .wav file if using Python and playing thesound vector using sound(z,fs2). The audio should be crisp sounding because the lowpassdeemphasis filter is not in place yet (it should a bit like having the treble control on your radioturned way up). Comment on any noise you might hear as well.

• The code following the discriminator first implements a 15 kHz lowpass, then a downsam-ple by 5, then the deemphasis filter:

if strcmp(mode,'mono'),

%/////////////////////////////////////////////////////////

% FM mono receiver

%/////////////////////////////////////////////////////////

% Design FIR 15 kHz audio channel lowpass filters

b15 = fir1(64,2*15000/fs1); % <== A 15 kHz lowpass

N2 = 5;

fs2 = fs1/N2; % nominally 48 kHz

y_lpr = filter(b15,1,z_dis);

y_DN2 = downsample(y_lpr,N2);

% Deemphasize with 75 us time constant to 'undo' the preemphasis

0 20 40 60 80 100 120−30

−25

−20

−15

−10

−5

0

5

10

15

20

Frequency (kHz)

Pow

er S

pect

rum

in d

B

19 kHz pilot

38 kHz subcarrier containingthe L - R channel information

L + Ratbase-band

The 38 kHz RDS subcarrier spectrum

Other subcarriers

B2

57

Figure 1.5: Received baseband spectrum (following FM demod).

� The receiver block diagram sitting behind a software definedradio (SDR) front-end is:

ECE 5675 Phase-Lock Loops and Synchronization 1–15

Chapter 1 Introduction and Overview

Problem 1 21

Part IVDeveloping Algorithms for a Broadcast FM Stereo Receiver

Problem 1Choose an FM station, KCME is fine, and capture 5-10 s from the RTL-SDR. You may use one ofyour previous captures.

• The clean KCME capture used earlier will be used again as source in for stereo demodula-tion

>> [x_LR,fs] = wavread('clean_KCME');

>> x = x_LR(:,1) + j*x_LR(:,2);

Problem 2Design a bandpass filter to extract the subcarrier signal from the discriminator output

. Plot the frequency response in dB to be confident you have a reasonable design.

• The m-file fm_rx.m contains both mono and stereo demodulation code

LPFB1

10 Discriminator

LPFB2

5

RTL-SDR

2.4 fc Gain

x n[ ] xI n[ ] jxQ n[ ]+=

yN2 n[ ]yB1 n[ ]

zL n[ ]

Msps

BPF

PLL (type 2)Bn 10 Hz=

ζ 0.707=

+

fq 19 kHz=

θ n[ ] ( )cos

Note: θ[n] is the tracked phaseof the 19 kHz pilot signal.

2

Coherent 38 kHzfor subcarrier demod

B3 B4,[ ]+

DeempFilter

75µs

5 DeempFilter

75µsLPFB2

L+R

L-R

L

RzR n[ ]

+

–

FM Demod and Stereo Demultiplex

= supplied components

r t( )

zdis n[ ]

zB2 n[ ]

zB3B4 n[ ]

L R–zdis n[ ]

Figure 1.6: Demodulator for FM stereo recovery.

� Track the 19kHz pilot phase, �Œn�, using a PLL (signal wascaptured live)

� The coherent carrier needed to demodulate the 38 kHz L-Rsubcarrier is cos.2�Œn�/ and the 57 kHz RDS carrier is cos.3�Œn�/

fs = 2400000b = signal.firwin(64,2*200e3/float(fs))# Filter and decimate (should be polyphase)y = signal.lfilter(b,1,x)z = ss.downsample(y,10)# Apply complex baseband discriminatorz_bb = sdr.discrim(z)

z_bb19 = signal.lfilter(b19,1,z_bb)theta, phi_error = sdr.pilot_PLL(z_bb19,19000,fs/10,2,100,0.707);

1–16 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

subplot(211)plot(1000*arange(len(phi_error[:1000]))/(fs/10),phi_error[:1000]*180/pi)ylabel(r’Phase (deg)’)xlabel(r’Time (ms)’)grid()subplot(212)psd(cos(2*theta),2**12,2400/10);psd(signal.lfilter(b38,1,z_bb19**2),2**12,2400/10);ylabel(r’PSD (dB)’)xlabel(r’Frequency (kHz)’)ylim([-80,5])tight_layout()

Listing 1.1: Demodulate and then track the 19 kHz pilot subcarrier.

Loop transient as it locks to the 19 kHz pilot

With and without a bandpass prefilter centered on 19 kHz

Figure 1.7: Traced phase in time and frequency.

ECE 5675 Phase-Lock Loops and Synchronization 1–17

Chapter 1 Introduction and Overview

Example 2: Bit Synchronization for FSK Demod Signal

� When an asynchronously sampled bit stream is output from anFM discriminator bit synchronization is needed to take sam-ples of the waveform at the point of maximum signal-to-noiseratio

� The sample-correlate-choose-smallest (SCCS) algorithm is usedhere1

Problem 1 29

Part VDeveloping Algorithms for a

Frequency Shift Keying Receiver

Problem 1To experiment with the FSK receiver you will need to first set up a transmitter. The Agilent 33250generator will again be used. In order determine if the system is reliable you need to perform biterror probability (BEP) testing, also commonly referred to as bit error rate (BER) testing. Toobtain a known source of data bits you will drive the external modulation port of the Agilent33250 with a level shifted out from the mbed microcontroller. Recall your experiences with thishardware back in Lab 2. The block diagram of the transmitter is shown below.

Part aDesign an test an op-amp level shifter that takes to 0–3.3v output from the mbed to an amplitudeswing of v. It is important that the data waveform not be inverted, hence a second op-amp isused.

LPFB1

N1 Discriminator

LPFB2

N2

RTL-SDR

2.4 fc Gain

x n[ ] xI n[ ] jxQ n[ ]+=

yN1 n[ ]yB1 n[ ]Msps

Removemean

+1-1

sign( )

SCCSBit Synch

m-SeqBit ErrorDetection

SR Length, m = 5

Must match mbed

ClockTrackingData bits

Bit ErrorReport

NsApproximatesamples per bit

FSK Demodulator Including Bit Synch

= supplied components

r t( )

zN2 n[ ] zD n[ ]

zdis n[ ]

zB2 n[ ]

zbits n[ ]

2.5±

Figure 1.8: FSK demod block diagram with SCCS bit synch.

� Of interest here is optimum sampling index when there arenominally N D 20 samples/bit (1 kbps) and N D 8 samplesper bit (10 kbps)

1Kwang-Cheng Chen and Jean-Ming Lee, “A Family of Pure Digital Signal Processing BitSynchronizers”, IEEE Transactions on Communications, VOL. 45, NO. 3, March 1997.

1–18 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

� The transmit clock and receiver sampling rate clock are slidingpast each other, so over time the absolute sampling index mustadjust

Problem 2 40

0 2 4 6 8 10 12 14

x 104

0

2

4

6

8

Bits

SC

CS

Tra

ck m

od 8

sam

p/bi

t

0 2000 4000 6000 8000 10000 120000

5

10

15

20

Bits

SC

CS

Tra

ck m

od 2

0 sa

mp/

bit

Rs 1 kbps=

Rs 10 kbps=

Figure 1.9: Sampling index tracking over time at 1 kbps and 10 kbps.

ECE 5675 Phase-Lock Loops and Synchronization 1–19

Chapter 1 Introduction and Overview

Example 3: Speading Code Tracking using a Delay-LockedLoop

� In a spread-spectrum system the received must implement a lo-cal spreading code generator that finds coarse code alignmentand then tracks the cross-correlation between the received sig-nal code and the local code:

ECE 5650/4650 Computer Project #2: DSP in GPS Signal Acquisition and Tracking

Background Theory 4

present in this project, but part of the CA code signal, is a 50 bit/s data stream, , which con-tains:

• Satellite almanac data

• Satellite ephemeris data

• Signal timing data

• Ionospheric delay data

• A satellite health message

To be clear, in the project simulation code only , where as in reality is present. Formore information on the formatting of the 50 bps data stream, consult [1] or [2]. Note that the bitperiod is 20ms, so 20 CA code periods fit into one data bit period.

PseudorangeI now jump back to the geometric range given in (2), and write it in terms of time parameters

(5)

where is the time the signal leaves the satellite, is the time the signal arrives at the receiver,and is the velocity of propagation. The actual measurement process is depicted in Figure 3. The

d t� �

ci t� � d t� �ci t� �

r

Geometric Range r c Tu Ts–� � c t'= = =

Ts Tuc

As the code repeats cross correlation trianglepeak also repeats every 1ms (1023 chips)

SatelliteTransmittedCA Codeat SV timeUserReceivedCA Code(delayed)

ReplicaCA Codeat localtime

ReplicaCA Codecross cor-related at

Tc

For the GPS CA code 1/Tc = 1.023 McpsTs tG+

Tu

tu tpeak TcT– c

pseudo range when scaled byc = velocity of propagation(includes local clock errors)

ci t Tu–� �

ci t tu–� �

tpeak Tu tu+=

local time

Figure 3: User time delay measurement using cross correlation with the localreplica code.

Ts

t'

Figure 1.10: For GPS user time delay measurement using cross cor-relation with the local replica code.

� For live capture or simulation purposes the following block di-agram describes the system with an emphasis on the spreadingcode tracking:

1–20 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

ECE 5650/4650 Computer Project #2: DSP in GPS Signal Acquisition and Tracking

Background Theory 5

pseudorange [1] is given by

(6)

where is the receiver clock offset or error relative to the system clock and is the offset of thesystem clock from the true system time. Rearranging (6) gives

(7)

The GPS ground monitoring system determines and includes this information in the 50 bpsdata stream. So all that is left is , meaning that to calculate the user position all you need to doobtain four pseudoranges from received CA code waveforms and solve for the four unknowns

and . The details of this are not part of this project, details can be found in [1] and[2].

Navigation Receiver Based on the RTL-SDRThis project is entirely computer simulation based, but the design of the simulation assumes thatthe receiver front-end utilizes the RTL-SDR software defined radio dongle [4]. A high level blockdiagram depicting this configuration is shown in Figure 4.In this figure you see highlighted a

multi-channel CA code acquisition and tracking subsystem. Each of these channels is responsiblefor processing the signal from a particular SV and hence uses a local replica CA code to correlateand track the code using a DLL. Serial search is used to find the proper code phase.

In the simulation for this project, the composite signal received signal at 2.4 Msps is formedusing a collection of Python functions as shown in Figure 5. The signal is generated at 3 samplesper chip making the effective sample rate in Hz be MHz, then re-sampled at 2.4E6MHz. The effective number of samples per chip is thus or 0.4262 chips per

Pseudorange U c Tu tu+� � Ts tG+� �–> @= =

tu tG

U c Tu Ts–� � c tu tG–� �+ r c tu tG–� �+= =

tGtu

xu yu zu� �� � tu

Channel 1

Channel 2

Channel N

. . .

Nav

igat

ion

Rec

eive

rPr

oces

sor

DisplayNav Data

Patch Ant.& Preamp RTL-SDR

RF Front-End& Digitizer

Complex basebanddiscrete-time signal

pseudorange

Multi-channelDSP-basedCA code acq.& track

2

Project Focus

Figure 4: High level GPS receiver block diagram noting the multi-channelCA code acquisition and tracking subsystem.

1

at 2.4 Msps

1 2= real = complex

U1d1 n> @

U2d2 n> @

UNdN n> @

& 50 bps data

3 1.023E6u2.4 1.023e 2.3462=

Figure 1.11: Generation of GPS L1 signals similar to live capturefrom an RTL-SDR.

� The geometric range r between the satellite and the user iswritten in terms of time parameters

Geometric Range D r D c.Tu � Ts/ D c�t

where Ts is the time the signal leaves the satellite, Tu is thetime the signal arrives at the receiver, and c is the velocity ofpropagation

� The pseudorange is given by

Pseudorange D � D c�.Tu C tu/ � .Ts C ıt/

�D c.Tu � Ts/C c.tu � ıt/ D r C c.tu � ıt/

where tu is the receiver clock offset or error relative to the sys-tem clock and�t is the offset of the system clock from the truesystem time

� A delay-locked loop (DLL) is a PLL-like structure for trackingthe code and then obtaining the pseudo range

ECE 5675 Phase-Lock Loops and Synchronization 1–21

Chapter 1 Introduction and OverviewECE 5650/4650 Computer Project #2: DSP in GPS Signal Acquisition and Tracking

Background Theory 11

system is shown in Figure 6. A portion of a carrier traction system, which is often used to remove

All of the implemented functionality of Figure 6 is implemented by the Python classCA_code_track found in the module GPS.py (see the appendix of the code ZIP package formore details). The code tracking class also makes use of the code_NCO class. Of special note,each instance of the CA_code_track class is an object containing three code correlators. Theprompt or P channel is used to detect coarse code alignment, and in a complete GPS receiver, notimplemented here, recover the 50 bps data stream. The early or E and late or L channels are usedto form an error signal that advances or retards the code Numerically controlled oscillator (NCO).The default time separation between these signals is 0.5 chip. The objective is to keep the replicacode perfectly aligned with the input signal. When this happens the NCO code phase contains thepseudorange, which as you know from an earlier discussion, is used to solve for the user location.

All of the signal points marked with a green dot are test points returned by the class attributetrk_var:

#+++++++++++++++++++++++++++++++++++++++++++++++++++++ trk_vars = a collection loop signals recorded during the simulation: row 0 = abs(early correlator output) row 1 = abs(prompt correlator output)

1msAccum

1msAccum

1msAccum

ej2Snf̂D fclke–

CarrierNCO

CodeNCO

LoopFilter

DLLDiscrim

Lock Det& Ser Srch

CodeLUT + +

2

2

2

2

2E1

L1

E L

P

ComplexbasebandCA Signals

1r

1r

1r

carrieraiding

chipsper sampfclk

Carrier PhaseTrack Discrim

Not Implemented

NotImplemented

Figure 6: Serial search code acquisition and noncoherent DLL code tracking.

Implemented by Python class CA_search_track

F z� � K1K2

1 z 1––----------------+=

E12 L12–

E12 L12+-------------------------

P1

L Int fclk 1ms�> @=

L

L2

L

Implement usingclass code_NCO

L

L

pseudorangeat 1ms

Figure 1.12: DLL block diagram

� Notice three correlators (local code multiply and 1ms accumu-lator) at early, prompt, and late time offsets

� The DLL error detector is formed using the early and late cor-relator outputs

� During the code acquisition phase, when the local code is steppedpast the received code, the prompt correlator output is moni-tored to see if coarse code alignment is found

� By opening the tracking loop we can observe the local codeslide past the received code, and generate verify the S -curve

1–22 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

ECE 5650/4650 Computer Project #2: DSP in GPS Signal Acquisition and Tracking

Background Theory 14

Noting that the code steps 0.05 chips/ms, it is possible to rescale the x-axis to have units of chips.

Moving on, T1 is now set back to 2000 and ss_step is set back -0.05 chips. Now coarseacquisition occurs and the track mode is entered. More plots will be shown as both the tracking

Note: Early is tothe right since we are steppingthe code back-wards

Track mode is never enteredduring this 100,000 chipsimulation! What’s wrong?

Figure 1.13: The correlator outputs under open loop tracking.

9

Figure 1.14: The DLL S-curve, theory and measured.

ECE 5675 Phase-Lock Loops and Synchronization 1–23

Chapter 1 Introduction and Overview

� Closing the loop we can observe coarse acquisition as the localis stepped into alignment with the received code

ECE 5650/4650 Computer Project #2: DSP in GPS Signal Acquisition and Tracking

Background Theory 16

The DLL pulls in and the errorsettles to zero.

These 3 values representthe correlators surroundingthe triangular crosscorrelation peak

tTc-----

-0.5-1 10.50

E

P

L

Figure 1.15: With feedback re-enable the three correlator outputsform the desired E, P, and L outputs.

� When the prompt correlator output crosses a threshold the DLLis engaged and the loop pulls in and finally begins tracking

� As with any PLL there is some settling time while the looperror approaches zero

1–24 ECE 5675 Phase-Lock Loops and Synchronization

Chapter 1 Introduction and Overview

ECE 5650/4650 Computer Project #2: DSP in GPS Signal Acquisition and Tracking

Background Theory 16

The DLL pulls in and the errorsettles to zero.

These 3 values representthe correlators surroundingthe triangular crosscorrelation peak

tTc-----

-0.5-1 10.50

E

P

L

Figure 1.16: DLL pulse-in and track

ECE 5675 Phase-Lock Loops and Synchronization 1–25