Patrick Thompson - IEEE Web Hostingewh.ieee.org/soc/cpmt/newsletter/200403/advprogectc.pdf3 Advance...

Transcript of Patrick Thompson - IEEE Web Hostingewh.ieee.org/soc/cpmt/newsletter/200403/advprogectc.pdf3 Advance...

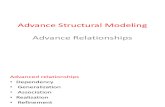

The Executive and ProgramCommittees of the ElectronicComponents and TechnologyConference (ECTC) welcome youto our 54th meeting at CaesarsPalace in Las Vegas.

This premier internationalconference continues to bringtogether the best in packaging,components and microelectronic

systems science, technology and education in an environment ofcooperation and technical exchange.The technical sessions focuson leading-edge developments and technical innovations in severalareas, including: optoelectronics, advanced packaging technologies,high-performance package design, simulation and manufacturinginterconnections and reliability.

The 54th ECTC provides a wealth of opportunities for education,discussion and networking. In 2004, we will provide 16professional development courses, taught by leaders from industryand academia.This year’s conference has more than 325 papersorganized into 39 oral presentation sessions, plus two postersessions, which provide the opportunity to exchange ideas andinformation with today’s packaging technology leaders.This year,we are especially pleased to highlight papers in two special topicareas – MEMS and nanotechnology – as part of our ongoing effortto bring emerging technologies that have great future potentialtogether with key established packaging technologies. Formalsessions are complemented by informal evening sessions on avariety of topics of interest to packaging technologists.Thesesessions allow for extensive interaction with presenters and otherattendees.The Technology Corner offers companies theopportunity to exhibit their products and services in anenvironment that fosters discussion and interactions withengineers and managers attending the ECTC.

The ECTC depends on literally hundreds of skilled and dedicatedpersons each year for continued success.We extend our sincerestthanks to ECTC authors, speakers, instructors and exhibitors foryour contributions and participation.We are most grateful to theProgram Committee, Session Chairs and Co-chairs, those whomade the conference arrangements and handled the publicity andpublications.We thank the corporate coffee break and receptionsponsors for their generous contributions which allow us to offera high-quality technical program.

Finally we offer this conference program with pride andanticipation to all conference attendees. You are the reason forthe ECTC, and we look forward to your comments on whatwe’ve done well and where we can improve to raise the qualityand value of future conferences.

Patrick Thompson54th ECTC Program Chair

2

IndexECTC Registration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3General Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3Technology Corner Exhibits . . . . . . . . . . . . . . . . . . . . . . . . .4NEMI Tin Whisker Workshop . . . . . . . . . . . . . . . . . . . . . . . .4Plenary Session . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4Luncheons and Receptions . . . . . . . . . . . . . . . . . . . . . . . . . .5Hotel Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5Attractions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5Executive & Program Committees . . . . . . . . . . . . . . . . . . .6,7Professional Development Courses . . . . . . . . . . . . . . . . .8-13Program Sessions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-27Hotel Registration Form. . . . . . . . . . . . . . . . . . . . . . . . . . . .28Corpora te Conference Sponsors . . . . . . . . . . . . . . . . . . . .28Conference Registration Form. . . . . . . . . . . . . . . . . . . . . . .29Conference Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Introduction from the 54th ECTC Program Chair Patrick Thompson

The 54th Electronic Components and Technology Conference (ECTC)Caesars Palace, Las Vegas, Nevada, June 1-4, 2004

Photograph courtesy of Las Vegas News Bureau

3

Advance RegistrationTo register in advance for the 54th ECTC, your applicationand payment check/credit card information must be receivedno later than May 15, 2004. Complete and submit the onlineregistration form (preferred registration) at:www.ectc.net/reg.htm, mail to the address on the AdvanceRegistration Form on page 31, or fax your form with paymentinformation to (703) 875-8908.

Register early … save $100. All applications received afterMay 15, 2004 will be considered Door Registrations. Thosewho register in advance can pick up their registration packetsat the ECTC Registration Desk in the Prefunction Area, 4thFloor at Caesars Palace. Additional Advance Programs areavailable from:

Jim Bruorton, Publicity Chairman 54th Electronic Components & Technology Conference c/o KEMET Electronics CorporationP.O. Box 5928Greenville, SC 29606Phone: (864) 963-6621 Fax: (864) 963-6444Email: [email protected]

DO NOT SEND ADVANCE REGISTRATIONS TOTHE ABOVE ADDRESS. SEE REGISTRATION FORMON PAGE 29.

Registration FeesAdvance Registration with proceedings (CD or printed),

CTC, CPMT and Program Chair Luncheons . . . . . .*$600Door Registration with proceedings (CD or printed),

ECTC, CPMT and Program Chair Luncheons . . . . .*$700One Day Registration . . . . . . . . . . . . . . . . . . . . . . . . .$375Speaker/Session Chair (Door Rate $500) . . . . . . . . . .$400Speaker/One Day . . . . . . . . . . . . . . . . . . . . . . . . . . . .$250Student Speaker . . . . . . . . . . . . . . . . . . . . . . . . . . . . .$150Student (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .$150Tuesday Single AM or PM Courses with Luncheon . .#$350Tuesday AM & PM Courses with Luncheon . . . . . . . .#$550 Student Tuesday All-Day Courses . . . . . . . . . . . . . . . . .$75Joint ECTC/ITHERM Advance . . . . . . . . . . . . . . . . . . .$750Joint ECTC/ITHERM Door . . . . . . . . . . . . . . . . . . . . .$800NEMI Workshop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .$75Proceedings only, U.S. Postpaid . . . . . . . . . . . . . . . . . .$300

Foreign . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .$350

* IEEE Member - Advance/$500, Door/$600# Door rate will be an additional $50(1) Students receive CD Rom.

Note: There will be no refunds on cancellations madeafter May 15, 2004.

At Door Registration ScheduleRegistration will be held at the Prefunction Area (4th Floor) asfollows:

Monday, May 31, 2004 – 3:00 to 5:00 PM (PD Courses & Conference)Tuesday, June 1, 2004 – 6:45 to 8:00 AM (AM PD Courses Only)Tuesday, June 1, 2004 – 11:00 AM to 1:15 PM (PM PD Courses Only)Tuesday, June 1, 2004 – 1:15 to 5:00 PM (Conference)Wednesday, June 2, 2004 – 6:45 AM to 4:00 PMThursday, June 3, 2004 – 7:30 AM to 4:00 PMFriday, June 4, 2004 – 7:30 AM to 12:00 PM

General InformationConference organizers reserve the right to cancel or changethe program without prior notice.

Loss Due to TheftConference management is not responsible for loss or theftof personal belongings. Security for each individual’sbelongings is the individual’s responsibility.

Coffee Break SponsorsSponsorships are available for companies that would like toparticipate in the 2004 Electronic Components andTechnology Conference by assisting in sponsoring theconference breaks. Your company’s name will be included inthe conference final program and will be displayed on a sign inthe refreshments area. A table will be provided nearby todisplay limited promotional/informational material about thecompanies sponsoring breaks. To sign up to sponsor a coffeebreak, simply indicate your interest on the ConferenceAdvance Registration form (page 29) and enclose the $350sponsorship fee, payable to the 54th Electronic Componentsand Technology Conference.

Please note: Sponsorships must be prepaid, and must be received atleast four weeks before the conference in order to be listed in theFinal Program. For further information, call EIA (703) 907-8027.

54th ECTC Advance Registration

55th Electronic Componentsand Technology Conference

Wyndham PalaceLake Buena Vista, Florida

May 31 - June 3, 2005Make plans now to join us!

The above schedule for Tuesday will be rigorously enforcedto prevent students from being late for their courses.

Although the current economic climate in theelectronics industry is improving, companies are stillbeing selective in choosing the conference and tradeshows where they will exhibit their products andservices. Each year more companies havedetermined that ECTC provides them theopportunity to identify superior prospects. Theprimary reason is that the engineers and managerswho attend ECTC hold decision-making positions atthe world’s leading electronics industry’s equipmentand components manufacturers. The attendees areattracted by ECTC’s strong technical program.Authors in the field believe that ECTC offers the bestforum for presenting their work.

Exhibit hours will be from 1:30 to 6:30 PM onWednesday, June 2 and 9:00 AM to Noon and 1:30to 6:00 PM on Thursday, June 3. Exhibit spaces arestill available. Following is a list of exhibitors as ofFebruary 2, 2004. The exhibit application, a currentexhibitor list and the booth layout showing theavailable booths can be found on the ECTC web siteat www.ectc.net under Technology Corner Exhibits.If you need additional information or have questions,call Bill Moody at (302) 478-4143, or [email protected].

3M Electronics Markets Materials Div.3M Microinterconnect Systems Div.

Advanced Packaging MagazineAnsoft Corporation

ANSYS, Inc.Asymtek

Bergquist Company (The)Ceramics Process Systems Corp.

Chip Scale ReviewChip Supply, Inc.

Dow Chemical Co., (The)Dow Corning Corporation

Electronics Cooling MagazineEmerson & CumingEnerdyne Solutions

ENGENT, Inc.Epoxy Technology, Inc.ESPEC Corporation

Fluent Inc.HD Microsystems

Henkel Loctite CorporationHitachi Cable America, Inc.

Indium Corporation of AmericaInnovative Research, Inc.

Interconnect Systems Inc.KEMET Electronics Corporation

Kyocera America, Inc.Matec Micro Electronics

Mini-Systems, Inc.Mitsui Chemicals America, Inc.

NAMICS Technologies, Inc.National Semiconductor Die Products

Optimal CorporationPac Tech Gmbh

PRC (Georgia Tech)Rotys, Inc.

Semi Dice, Inc.Semiconductor International

SIGRITY, Inc.Sony Chemical Corp. of America

SUSS MicroTecTechSearch International, Inc.

Temptronic CorporationThermagon, Inc.

Toray Engineering Co., Ltd.Unitive, Inc.

Vishay Intertechnology, Inc.Zymet, Inc.

4

ECTC NEMI Tin Whisker Workshop Tuesday, June 1, 2004 –8:30AM - 5:00PMCourse Director: Ron Gedney

With the move toward Pb-free electronics, a popular finish forcomponent terminations is 100% tin (Sn). However, pure Sncoatings have a tendency to grow small filaments, popularlycalled “whiskers,” that can bridge adjacent terminals, causingsystem failures. The National Electronics ManufacturingInitiative (NEMI) formed three projects to work on thisphenomenon:Accelerated Test (to develop accelerated tests topredict tin whiskers); Modeling (to understand basic cause ofwhiskers); and User Group (to determine how high-reliability,long-life systems can be protected with today’s knowledge).This workshop will provide an overview of more than threeyears’ work investigating all aspects of tin whiskers from allthree projects. Attendees will get a good overview of tinwhiskers, a set of tests recommended to JEDEC, basic theoriesbehind whisker formation, and how to protect system reliabilitygiven what we know today.

Technology Corner Exhibits

ECTC Plenary SessionHigh-Density InterconnectionWednesday, June 2, 2004 – 7:00 - 9:00 PM

Chair: Yoshitake Fukuoka – WeistiCochair: Kishio Yokouchi –

Fujitsu Laboratories of America, Inc.

1. Recent Advances in Materials, Processes and High-Density Structures at GT-PRCVenky Sundaram and Rao R.Tummala – Georgia Institute of Technology

2. Dielectric Materials for High-Density Interconnect TechnologyMasahiro Ito and Shunsuke Yokotsuka – Asahi Glass Co., Ltd.

3. Recent Advances in Materials, Processes and High-Density Structures at GT-PRCVenky Sundaram and Rao R.Tummala – Georgia Institute of Technology

4. Advanced Technology for High-Density Substrate and BoardsYasuhito Takahashi – Fujitsu Microelectronics America, Inc.

5. High-Density and High-Frequency Silicon Substrate Technology for SiPAtsushi Takano – Dai Nippon and Yoshitake Fukuoka – Weisti

6. Passive and Active Components Embedding Technology for High-Density SubstrateMasaaski Katsumata – Matsushita Electronic Components Co., Ltd.

7. A consideration for Total Mechanical Stress in Flip-Chip Packaging Utilizing Buildup Substrate TechnologyYutaka Tsukada – Kyocera SLC Technologies Corporation

Photograph courtesy of Las Vegas News Bureau

5

LuncheonsProfessional Development Course and NEMI Workshop LuncheonThe Electronic Components and Technology Conference willsponsor a luncheon on Tuesday, June 1st, for all ProfessionalDevelopment and NEMI Workshop attendees.

ECTC LuncheonThe Electronic Components and Technology Conference willsponsor a luncheon on Wednesday, June 2nd, for conferenceattendees.

CPMT LuncheonThe IEEE Components, Packaging and ManufacturingTechnology Society will sponsor a luncheon for conferenceattendees on Thursday, June 3rd.

Program Chair LuncheonOn Friday, June 4th, the Program Chair will sponsor aluncheon for conference attendees.

Hotel AccommodationsRooms for ECTC attendees have been reserved at CaesarsPalace.The special conference rate is $165 for Run of Houseand $199 for Palace Tower Rooms.There are 2,500 roomsand suites, three spacious casinos, four lounges, nineteenrestaurants, a health spa, a fitness center, three swimmingpools, an Omnimax theatre, and the Appian Way and ForumShops available to you for greater luxury and comfort duringyour stay.

Room reservations must be made directly with the hotel byApril 29, 2004 to ensure special convention rates. If you needto change or cancel your reservation, please do so prior to

three (3) days or 72 hours before arrival date to avoidforfeiture of deposit. Check-in time is 3:00 PM and check-outtime is 12:00 PM. Most major credit cards are accepted. Callfor booking assistance today at (702) 731-7222 or 800-634-6661 and mention ECTC for discounted rates or fax (702)731-7172.

Area AttractionsThere is plenty to see and do in Las Vegas.You can start atone end of the strip and stop at every hotel to do somethingdifferent.Adventuredome Theme Park is located at CircusCircus offering 21 rides and attractions. Free circus acts areperformed daily inside.The Eiffel Tower located at the ParisHotel offers the 50-story tower to take a panoramic view ofthe Las Vegas Valley. Shopping has not been forgotten either.The Forum Shops and the Appian Way are located at CaesarsPalace along with the famous Roman statues that come tolife at the Festival Fountains.The Bellagio Hotel is the placeto see dancing fountains that are choreographed to music byartists such as Frank Sinatra, Elton John, Henry Mancini andmore. If you want to go to the beach in the middle of thedesert, stop at Mandalay Bay. Enjoy a swim, then visit theaquarium.Treasure Island and the pirates are great fun foreveryone.The Mirage’s 54-foot volcano eruption every 15minutes from dusk to midnight is always exciting.

Just 30 miles from Las Vegas on Highway 93 is the HooverDam and Power Plant that was built in 1937.The VisitorCenter is open from 9:00AM to 5:00PM. Close to 1,000,000visitors a year visit this National Historic Landmark.Ticketsare $10 each for adults ($8 Seniors), children 7 - 16 are $5and children 6 and under are free.What a great family trip!

54th ECTC Gala ReceptionAll badged attendees and guests are invited to

attend a reception hosted by AVX Corporation,KEMET Electronics Corporation,

KOA Speer Electronics, Inc., Murata ElectronicsNorth America, ROHM Electronics USA,

and Vishay Intertechnology, Inc.on Thursday, June 3rd at 6:30 PM.

General Chair’s SpeakersReception

Tuesday, June 1, 20046:00 PM - 7:00 PM(by invitation only)

Photograph courtesy of Caesars Palace

ExecutiveCommittee

Steve BezukGeneral ChairKyocera America, Inc.+1-858-576-2651

Donna NoctorVice-General ChairECTC Consultant+1-208-978-9425

Patrick ThompsonProgram ChairTexas Instruments, Inc.+1-972-995-7660

Eric PerfectoAsst. Program ChairIBM Microelectronics+1-845-894-4400

Peter J.WalshArrangements ChairEIA/ECA+1-703-907-8028

Michael B. McShaneSr. Past General ChairMotorola, Inc.+1-512-996-6175

Wayne J. HowellJr. Past General ChairIBM Corporation+1-845-892-5360

Thomas G. Reynolds, III Finance ChairMurata Electronics NA, Inc.+1-850-897-7323

Glyndwr Smith,EIA/ECA RepresentativeVishay Intertechnology, Inc.+1-610-251-5274

C. P.WongIEEE/CPMT RepresentativeGeorgia Institute of Technology+1-404-894-8391

Albert PuttlitzProfessional Development Course ChairMechanical Engineering Consultant+1-802-899-4692

James A. BruortonPublicity ChairKEMET Electronics Corporation+1-864-963-6621

John H. LauPublications ChairAglient Technologies, Inc.+1-408-553-2358

Advanced Packaging Jeffrey A. Knight, ChairIBM Corporation +1-607-757-1105

Sudipta K. Ray, Co-ChairIBM Microelectronics+1-845-894-6240

Daniel BaldwinGeorgia Institute of Technology+1-404-894-4135

Karla Y. CarichnerConexant Systems+1-949-483-9151

Tim ChenIntel Corporation+1-480-552-8712

Altaf HasanIntel Corporation+1-430-554-3427

Douglas HopkinsSUNY Buffalo Energy Systems Institute+1-607-729-9949

Satoshi ItoNitto Denko Corporation+81-532-43-1802

Beth KeserMotorola, Inc.+1-480-413-8022

Young-Gon KimTessera+1-408-383-3685

Yee L. LowLucent Technologies+1-908-582-2718

Raj N. MasterAMD+1-408-982-7023

Gary MorrisonTexas Instruments, Inc.+1-972-995-4851

Luu T. NguyenNational Semiconductor Corp.+1-408-721-4786

Thomas NollDow Corning Corporation+1-989-496-1506

Raj PendseChipPAC, Inc.+1-510-979-8330

Sudipta K. RayIBM Microelectronics+1-845-894-6240

Joseph W. SoucyDraper Laboratory, Pkg. Group+1-617-258-2953

E. Jan VardamanTechSearch International, Inc.+1-512-372-8887

Tiao ZhouTexas Instruments, Inc.+1-214-567-2736

Components & RF Leonard W. Schaper, ChairUniversity of Arkansas+1-479-575-8408

Eric Michelson, Co-ChairVishay Intertechnology, Inc.+1-610-251-5279

Amit P.AgrawalBroadcom Corporation+1-408-922-7332

Rao BondaMotorola, Inc.+1-480-413-6121

Craig GawMotorola, Inc.+1-480-413-5920

Lih-Tyng HwangMotorola, Inc.+1-847-576-5182

Mahadevan K. IyerInst. of Microelectronics+65-770-5424

Timothy G. LenihanConsultant+1-847-599-4100

Li LiMotorola, Inc.+1-480-413-6653

Albert F. PuttlitzMechanical Engineering Consultant+1-802-899-4692

Thomas G. Reynolds, IIIMurata Electronics NA, Inc.+1-850-897-7323

Manos M.TentzerisGeorgia Institute of Technology+1-404-385-0378

Education Paul Wesling, ChairConsultant+1-408-252-9051

Leyla Conrad, Co-ChairGeorgia Institute of Technology+1-404-385-0439

Avram Bar-CohenUniversity of Maryland+1-301-405-3173

William BrownUniversity of Arkansas+1-479-575-6045

Jim MorrisPortland State University+1-503-725-9588

Albert F. PuttlitzMechanical Engineering Consultant+1-802-899-4692

Andrew A. O.TayNational University of Singapore+65-6874-2207

Klaus-Jurgen WolterTechnische Universitat Dresden+49-351-46336345

Interconnections Rajen Dias, ChairIntel Corporation+1-480-554-5202

David McCann, Co-ChairAmkor Technology, Inc.+1-480-821-5000, x5029

Haluk BalkanKulicke and Soffa+1-602-431-6020 x464

Mark V. BrillhartCisco Systems Inc.+1-408-525-7466

William ChenASE-US Inc.+1-408-986-6505

Yifan GuoSkyworks Solutions, Inc.+1-949-231-4796

Dev GuptaAdvanced Packaging & SystemsTechnology+1-480-540-3232

Christine KallmayerTechnical University of Berlin+49-30-46403-228

Sung K. KangIBM - TJ Watson Res. Center+1-914-945-3932

Corey KoehlerAmkor Technology, Inc.+1-480-821-2408 x5373

Charles LeeInfineon Technologies AP+65-6840-0448

Jong-Kai LinMotorola, Inc.+1-480-413-3254

Voya MarkovichEndicott Interconnect Technologies+1-607-755-1978

Goran MatijasevicUniveristy of California, Irvine+1-949-824-9830

Lei L. MercadoMotorola, Inc.+1-480-552-1383

Dennis OlsenConsultant+1-480-994-9926

Kanji OtsukaMeisei University+81-428-25-5214

Prema PalaniappanEricsson Inc.+1-919-472-1922

Senol PekinLSI Logic+1-408-552-4898

Wolfgang SauterIBM Microelectronics+1-802-769-3634

Lei ShanIBM T. J.Watson Research Center+1-914-945-2304

Sue TengCisco Systems, Inc.+1-408-853-2527

Jin YuKorea Advanced Institute of Science andTechnology+82-42-869-8841

Manufacturing Technology Tom Swirbel, ChairMotorola, Inc.+1-954-723-5671

Tom Poulin, Co-ChairAerie Engineering+1-909-248-1237

Sharad BhattShanta Systems Inc.+1-814-362-6996

6

7

Douglas E. ChrzanowskiIBM Corporation+1-607-755-1403

David KeezerGeorgia Institute of Technology+1-404-894-4741

Claude LadouceurIBM Canada, Ltd.+1-450-534-7314

Kitty PearsallIBM Corporation+1-512-838-7004

Shawn ShiIntel Corporation+1-480-554-2155

Jie XueCisco Systems, Inc.+1-603-896-5337

Materials & Processing Chin C. Lee, ChairUniversity of California, Irvine+1-949-824-7462

Ceferino Gonzalez, Co-ChairDuPont Advanced Fibers Sys.+1-919-248-5062

Rajen ChanchaniSandia National Labs+1-505-844-3482

Phil GarrouDOW at MCNC+1-919-248-9261

Chandra JayaramIntel Products (M) Sdn. Bhd.+604-253-5289

Vaidyanathan KripeshInstitute of Microelectronics+65-6770-5592

Yeong J. LeeDow Corning +1-989-496-7032

Ming LiThe Chinese Unviersity of Hong Kong+852-31634129

Kwang-Lung LinNational Cheng Kung University+886-6-2762709

Johan LiuChalmers Univ. of Technology+46-31-706-6294

Daoqiang (DQ) LuIntel Corporation+1-480-552-2909

Jim MorrisPortland State University+1-503-725-9588

Kyung-Wook PaikKorean Advance Institute of Science andTechnology+82-42-869-3335

Eric PerfectoIBM Microelectronics+1-845-894-4400

Mark PoliksEndicott Interconnect Technologies+1-607-755-2064

C.P.WongGeorgia Institute of Technology+1-404-894-8391

Modeling & Simulation Suresh K. Sitaraman, ChairGeorgia Institute of Technology+1-404-894-3405

Michael Lamson, Co-ChairTexas Instruments+1-972-995-2490

W. Scott BurtonAgilent Technologies, Inc.+1-970-288-1186

Andreas CangellarisU. of Ilinois at Urbana-Champaign+1-217-333-6037

Moises CasesIBM Corporation+1-512-838-6225

Steve DvorakUniversity of Arizona+1-520-621-6170

L. J. ErnstDelft University of Technology+31-15-278-6519

George A. KatopisIBM Corporation+1-914-435-6719

Ravi KawAgilent Technologies, Inc.+1-408-345-8893

Bruce KimArizona State University+1-480-965-3749

Pradeep LallMotorola, Inc.+1-847-538-9885

Erdogan MadenciUniversity of Arizona+1-520-621-6113

Tony MakDallas Semiconductor Corporation+1-972-371-4364

John L. PrinceUniversity of Arizona+1-520-621-6187

Tawfik Rahal-ArabiIntel Corporation+1-503-613-5903

Madhavan SwaminathanGeorgia Institute of Technology+1-404-894-3340

G.Q. (Kouchi) ZhangPhilips+31-40-273-3825

OptoelectronicsJames E.Watson, Chair3M Company+1-651-733-3890

Torsten Wipiejewski, Co-Chair (N.Am.)ASTRI+852-3406-2894

Yasuhiro Ando, Co-Chair (Asia)Sigma-Links Inc.+81-426-62-0853

Sue Law, Co-Chair (Australia)Australian Photonics/OFTC +61-2-9351-1960

Mario DagenaisUniversity of Maryland+1-301-405-3684

Mino F. DautartasConsultant+1-540-953-2160

Jon HallBookham+44-1327356737

Randy HeylerNewport Corporation+1-949-253-1657

Masataka ItoInterIntelligence, Inc.+1-310-768-2900

Soon JangNewport Corporation+1-949-253-1625

Harry G. KellziTeledyne Electronic Technologies+1-310-574-2097

Michael LebbyIgnis Optics, Inc.+1-408-896-8484

Graeme MaxwellConsultant+44-1473-278258

Alan J. MorrowBinOptics Corporation+1-607-257-3200 X236

Bill RingTyco Electronics - Fiber OpticBusiness Unit+1-908-704-6605

Andrew ShapiroUniversity of California, Irvine+1-949-824-8086

Dariusz SieniawskiAchray Photonics+1-613-823-2211

Ephraim SuhirUniv. of IL at Chicago and ERS +1-650-969-1530

Christopher D.TheisAgere Systems+1-484-397-2964

Jean TrewhellaIBM T. J.Watson Research Center+1-914-945-2786

Ping ZhouGeneral Optoelectronic Devices, Inc.+1-818-735-7823

Posters Michael Caggiano, ChairRutgers Univ. Dept. of Elec. & ComputerEngineering+1-732-445-0678

Swapan Bhattacharya, Co-ChairGeorgia Institute of Technology+1-404-385-0708

Gerry CaggianoConsultant+1-928-704-1613

Mark EblenKyocera America, Inc.+1-858-614-2537

Lara MartinMotorola, Inc.+1-954-723-6959

Professional Development CoursesRonald E. Scotti, ChairConsultant+1-908-534-2039

Albert F. Puttlitz, Co-ChairMechanical Eng. Consultant+1-802-899-4692

Rao Bonda, Co-ChairMotorola, Inc.+1-480-413-6121

Quality & Reliability Charles Zhang, ChairIntel Corporation+1-480-552-0453

Darvin R. Edwards, Co-ChairTexas Instruments, Inc.+1-972-995-3569

Jo CaersPhilips Electronics Singapore +65-6357-9370

Sridhar CanumallaNokia Mobile Phones+1-469-767-9808

Harry K. CharlesThe Johns Hopkins Univ APL+1-443-778-8050

George HarmanNIST+1-301-975-2097

Xiaoling HeUniversity of Wisconsin, Milwaukee+1-414-229-6772

Donna M. NoctorConsultant+1-208-978-9425

John H. L. PangNanyang Technological University+65-6790-5514

Jeffrey SuhlingAuburn University+1-334-844-3332

Patrick ThompsonTexas Instruments, Inc.+1-972-995-7660

Charles UmeGeorgia Institute of Technology+1-404-894-7411

Dongji XieFlextronics International+1-408-576-7597

Special TopicsErik JungFraunhofer Institute for Reliability andMicrointegration+49-30-46403-230

S.W. Ricky LeeHong Kong University of Science &Technology+852-2358-7203

Michael B. McShaneMotorola, Inc.+1-512-996-6175

Rao R.TummalaGeorgia Institute of Technology+1-404-894-9097

C.P.WongGeorgia Institute of Technology+1-404-894-8391

ProfessionalDevelopment CoursesJune 1, 2004Albert F. Puttlitz, ChairConsultantPhone: (802) 899-4692Fax: (802) 899-4692Email: [email protected]

Ronald E. Scotti, Co-ChairConsultantPhone: (908) 534-2039Email: [email protected]

Rao Bonda, Co-ChairMotorola, Inc.Phone: (480) 413-6121Email: rao.bonda@motorola. com

MORNING COURSES8:15 AM – 12:00 PM

1. OPTOELECTRONICSCOMPONENTS AND MODULES FOR

COMMUNICATION NETWORKSInstructor: Bill Ring

Tyco Electronics

Course Objectives:Optoelectronics components and modules forthe communications industry and networks arecontinuously advancing in terms of speed, lowercost and design for high volume manufacture.The objectives of this course are to provide abackground on the current industry activecomponents and packaging approaches andreview the direction of active devices andpackaging technology for discrete componentsand data network modules. The course willcover the fundamentals of active III-V devices,manufacturing of components and transceiversfor the communications industry.

Course Outline:• Overview of communication requirements• Brief overview of semiconductor devices for

active communications devices• FP and DFB directly moduled lasers• VCSEL device for datacommunications• Packaging technology for communication

components• Low-cost plastic optics based packaging• TO-style packaging & high-speed

RF packaging• Reliability of components• Silicon optical bench technology• Modules for datacom

• SFF and SFP datacom modules• 10 Gigabit ethernet transceivers• Parallel module technology

Who Should Attend:This course is intended for engineers andmanagers who are involved in the design ofcomponents and modules for communicationnetworks. It will be beneficial for those whorequire a fundamental understanding and broadperspective on active components for LAN, SANOI connection and telecom modules, specificallytechnology, and manufacturing issues.

2. ADVANCED ORGANIC SUBSTRATEPACKAGE DESIGN &

MANUFACTURING FOR RF ANDBROADBAND

Instructor: Hassan Hashemi Mindspeed Technologies, Inc.

Course Objectives:The objectives of this course are to reviewdesign and manufacturing practices and tradeoffsaffecting current and next-generation wirelessand broadband IC packaging using laminatesubstrate technologies in single or multiple dieformat.The course material is based upon theinstructor's experience in current micro-modules designed for GHz IC packaging forwireless and wireline communication andstorage area networking applications.

Course Outline:• Review design and manufacturing practices

and tradeoffs• Ceramic versus laminate substrate-based

packaging- Micro-module design features with

chip-on-board and surface mount technologies

- Design tradeoffs for high volume manufacturing

- Laminate module electrical, thermal,and mechanical design features

- Laminate package materials• Example package design considering

performance, cost & manufacturing - Embedded passives in laminate substrates

• Organic substrate package assembly overview- Die attach, wire bond, overmold,

saw & singulation- Process tolerances and their

effects on performance• Conclusions

Who Should Attend:Engineers and technical managers who areinvolved in the design and manufacturing ofelectronic components and modules for wirelessand broadband networking or storage

applications. Attendees will learn aboutmaterials, processes, and design practices usedfor wirebond ICs, SMDs, and organic substratemodules used in high volume RF/GHz IC andsystem packaging.

3. INTEGRATED PASSIVETECHNOLOGY AND

COMMERCIALIZATIONInstructor: Richard Ulrich

University of Arkansas

Course Objectives:This course will be a comprehensive review ofpotential applications, commercializedtechnology, and possible future directions inintegrated passive components and processingfor organic boards. The organization of thecourse centers on the benefits and problemswith their implementation in order to helppotential users make decisions about theirapplicability in a given situation. Considerabletime will also be spent on the candidatematerials and processes for integrated resistors,capacitors and inductors in order to help thepotential user decide what processes canprovide the needed electrical performance whilebeing compatible with their existing substratesand fabrication technology. Emphasis will also beplaced on electrical testing, since users ofintegrated passives will find themselves in thebusiness of producing passive components, notjust buying them, since the electricalperformance characteristics of integratedpassives can be very different from their surface-mount counterparts, possibly providing significantcompetitive advantages. Several currentpotential applications will be described, withparticular emphasis on decoupling. The courseemphasizes applicability to manufacturedmicroelectronic systems and includes theoreticalmaterial necessary to support that purpose.

Course Outline:• Why use IPs?• Substrates of interest• Integrated resistors• Integrated capacitors• Integrated inductors• Electrical measurement of integrated

passives• Applications favorable for integrated

passives• Economics of IPs• Tolerance, repeatability and yield issues• Commercialized systems• Where are integrated passives going?

Who Should Attend:Engineers and scientists involved in electronicspackaging, circuit board manufacture, electricaldesign and passive component technologies.

8

4. POLYMERS FOR ELECTRONICPACKAGING

Instructor: C. P. WongGeorgia Institute of Technology

Course Objectives:Polymers are widely used in electronic packagingas adhesives, encapsulants, insulators, dielectrics,molding compounds and conducting elementsfor interconnects. These materials also play acritical role in the recent advances of low-cost,high performance novel no flow underfills,reworkable underfills for ball grid array (BGA),chip scale packaging (CSP), system on a package(SOP), direct chip attach (DCA), flip chip (FC),paper-thin IC and 3D packaging, conductiveadhesives (both ICA and ACA), embeddedpassives and nano-functional materials. It isimperative that material suppliers, formulatorsand their users have a thorough understandingof polymeric materials and their importance inthe advances of the electronic packaging andinterconnect technologies.

Course Outline:• Overview of semiconductor packaging

technology• Next generation of electronic packaging• Common electronic packaging materials:

conformal coating, glob-top, potting and casting

• Novel no-flow, advanced and reworkable underfills for flip-chip applications

• Conductive adhesives for lead-free interconnects – fundamentals and recent advances

• Low-cost high-performance embedded passives materials and processes

• Recent advances on nano photonic and low dielectric (k) materials and nano-functional materials

Who Should Attend:Engineers, scientists and managers involved in thedesign, process and manufacturing of ICelectronic components and hybrid packaging,electronic material suppliers involved in materialsmanufacturing and research and development.

5. SYSTEM-ON-PACKAGE (SOP) VS.SYSTEM-IN-PACKAGE (SIP),AND

SYSTEM-ON-CHIP (SOC)New Paradigms in Electronics

Instructor: Rao TummalaGeorgia Institute of Technology -

Packaging Research Center

Course Objectives:This course presents an overview of the GeorgiaTech Packaging Research Center's SOP (System-on-Package) vision for highly integrated andmicrominiaturized convergent systems with

consumer, computer, communication and bio-medical functions implementing an integratedapproach to digital, analog, RF, optical and sensingtechnologies. The SOP paradigm changes thecurrent chip-centric SOC methodology to acheaper, faster-to-market IC-package co-design-centric microsystems packaging design andtechnology flow. The advantages of the SOPparadigm over SOC appear overwhelming dueto SOP's design simplicity, lower cost, and higherelectrical performance, and without theintellectual property issues that dominate SOC.To realize these enormous advantages, new SOPsub-technology paradigms are required. Theseinclude mixed-signal design, ultra high-densityembedded digital, embedded optoelectronics andembedded RF component integration as well aswafer level packaging (WLP) and assembly, testand burn-in, thermal management and systemreliability. A key technology paradigm, whichGeorgia Tech has been developing with theNational University of Singapore, is the conceptof nanoscale WLP, testing and burn-in, whichpromises ultimate size miniaturization, andvirtually unlimited interconnections by means ofnanoscale interconnections. This course makes acompelling case for and presents the status ofSOP R&D around the world and compares andcontrasts with SOC, SIP and MCM.

Course Outline:• System trends to convergent systems• Semiconductor trends to SOC• IC and systems packaging evolution• Five approaches to convergent systems• What is SOP, and why?• Global developments of SOP• Comparison of SOC, SIP, MCM and SOP• Status of SOP technologies• What next after SOP?

Who Should Attend:This course is an overview course and is suitablefor all levels of R&D management, seniorengineers and executives involved in technicalstrategy, R&D, design, manufacturing, process andproduct development of electronic packagingand systems in automotive, consumer,communication, computer, biomedical, andaerospace industries.

6. "NANO" - THE NEXTTECHNOLOGY?

Overview of Nano-TechnologyInstructors: Walter Trybula

International SEMATECH and Deb Newberry

Newberry Technologies

Course Objectives:Nano is the catchall phrase that is used to implysome super advanced technology. Everyone has

a different idea of what it means. Thisintroduction to nano-technology will provide anoverview of various aspects of nano includingbio-tech and electronics. Nano-technologystarted with the carbon Buckyballs, which consistof 60 carbon atoms formed in a sphere.Stretching the Buckyballs creates carbonnanotubes. Nanotubes have low resistance,which has given rise to some predictions of gridsof nanotubes for carrying electrical signals.Starting with the Buckyballs more than 20 yearsago, the technology has grown exponentially.The explosion of new applications has occurredin the last few years and has become the centerof businesses’ attention in a search for new areasof expansion. There is a need to understandwhat this new technology really is. This courseprovides an explanation of basics of nano-technology. The purpose is to give the attendeesan overview of potential applications and anunderstanding of some of the complexities ofdeveloping nano-technology products.

Course Outline:• Introduction to nano (including

what is nano?) • An overview of nano-bio • Specific benefits • Business requirements • Packaging potential• Economics and world competition• The future and the challenges• Where do we go from here?

Who Should Attend:This introductory course is focused on peoplewho desire a better understanding of thedeveloping field of nano-technology. It will alsobe of interest to people who need to becomeinvolved in business dealing with nano-technology.

7. MICROELECTRONIC AND MEMS SENSORS

Instructors: Gábor Harsányi andZsolt Illyefalvi-Vitez

Budapest University of Technology andEconomics

Course Objectives:The course provides participants with anoverview of microsensors, i.e. miniature devicesfor measuring physical and chemical quantitiessuch as pressure, acceleration, speed, chemicalconcentration, etc. Microsensors fabricated bysolid-state and MEMS technology, from ceramics,thin and thick films, polymer films, as well as byoptical fiber technology are described andcharacterized.The different sensor structures inuse, the most important sensing effects, as wellas the principles of sensing various parametersare presented.The overview of application fieldsincludes industrial process control, automotive

9

and household case studies, with a special focuson environmental monitoring and biomedicalapplications. Advances in sensor packaging,modeling, design and fabrication are alsodescribed shortly. The presentation will use themagnificent virtual tools of SensEdu andMEMSEdu, which are tools developed as a CPMTinitiative in the frame of IEEE/NSF facultyfellowship program.

Course Outline:• Sensor technologies and materials:

- Solid-state semiconductor and ceramic technologies

- Thin and thick film, polymer film, and optical fiber based sensor technologies

• Sensor structures, basic models of sensor operations:- Impedance type sensors, semi-

conductor devices, calorimetric sensors, electrochemical cells

- Sensors based on acoustic wave propagation, sensors with optical waveguides

• Sensing effects, basic principles of microsensors:- Thermoresistive, thermoelectric,

piezoelectric, pyroelectric,piezoresistive, Hall effect

- The principle of adsorption and the absorption of chemical species;selective molecular receptors

- Permeation through membranes,ion-selective membranes, chemical-optical transduction effects

• Sensing various parameters:- Sensors for mechanical parameters,

such as pressure, force, acceleration,angular displacement

- Thermal, acoustic, radiation, magnetic field, chemical sensors and biosensors

• Application fields: overview and case studies- Industrial process control,

automotive, household- Environmental monitoring and

biomedical applications

Who Should Attend:The course is designed for electrical, mechanicaland chemical engineers, physicists, technicalmanagers, salesmen and students who wish toget a comprehensive overview of microsensors’operation principles and characteristics, and tolearn more about their applications. The coursefocuses on practical aspects and addresses fieldengineers and technicians from companies aswell.

8. MICROELECTRONICS PACKAGINGAND INTERCONNECTION - AWORLDWIDE PERSPECTIVE

Instructor: E. Jan Vardaman TechSearch International Inc.

Course Objectives:This course will cover developments and trendsin area array packages. Ball grid array (BGA)packages are increasingly found in productsincluding personal computers, portablecommunications devices, workstations/servers,mid-range and high-end computers, network andtelecommunications systems, and evenautomotive applications. Package trends andnew developments are described. Driven by thedemand for smaller, lighter, thinner portableproducts has come the development of chipscale packages (CSPs). Discussed are the varioustypes of CSPs in volume production and newdevelopments such as wafer level packages. Flipchip's advantage over wire bond interconnectionincludes higher density mounting, improvedelectrical performance, and improved reliabilityfor many applications. New applications for flipchip are described. Also included are trends,such as bump pitch, bump metallurgy, andsubstrate feature sizes.

Course Outline:• Overview and trends in micro-electronics

packaging and interconnect technology• BGA - definition, package constructions,

major volume applications by package type,new developments by package type, and new developments especially in high-performance packaging

• CSP - definition, package constructions,major volume applications by package type,new developments by package type, and new developments including wafer-level packages

• Flip chip related technologies - definition,flip chip in-package (FCIP) and flip chip on board (FCOB) applications, drivers for expansion, and future trends

• In addition, samples of packages/substrates/ modules will be used during this course to illustrate the topics described above.Photos of products using advanced packageswill also be included in this course.

Who Should Attend:This course will be beneficial to all managers andindividual contributors from the electronicsindustry who need fundamental understandingand broad perspective on microelectronicspackaging and interconnect technology, especiallyin technology trends and key developmentalareas such as BGA, CSP, and flip chip.

AFTERNOON COURSES 1:15 – 5:00 PM

9. RF/WIRELESS PACKAGINGInstructors: Joy Laskar and

Emmanouil (Manos) M.Tentzeris Georgia Institute of Technology

Course Objectives:Review the latest developments in the area ofnext-generation RF/ microwave packaging.Investigate different materials and topologies.Present integrated solutions for wirelesstransceivers incorporating packaging adaptiveantennas. Discuss possible solutions for RF-MEMS packaging problems. Provide easy-to-usedesign rules using CAD tools. Present integratedmodules for WiFi and 60 GHz broadbandcommunication/sensor applications.Course Outline:• Vertical interconnects (flip chip, BGA, PGA)• Embedded components in organics and

ceramics (LTCC) and LCP materials• Integrated inductors, filters, duplexers in

3D configurations• Packaging adaptive ultracompact and

multiband antennas• Integrated wireless transceivers for WiFi and

mm-wave applications• RF-MEMS• Practical designs using modeling CAD tools• Discussion of the challenges for the

extension of designs in UWB

Who Should Attend:Engineers and technical managers who would liketo get familiar with the challenges and problemsencountered in RF/Wireless packaging.

10. WAFER LEVEL - CHIP SCALEPACKAGING

Instructor: Luu T. NguyenNational Semiconductor Corporation

Course Objectives:Wafer level-chip scale packaging (WL-CSP) hasgained momentum in the small chip arena lately,driven by needs for cost reduction, form factorshrinkage, and enhanced performance. Thiscourse will provide an overview of the WL-CSPtechnology. The market drivers, benefits, andchallenges facing industry-wide adoption will bediscussed. The current WL-CSP configurations

10

IMPORTANT NOTICEIt is extremely important to register

in advance to prevent delays atdoor registration. Course sizes

are limited.

will be reviewed in terms of their construction,manufacturing process and publishedelectrical/thermal performance, together withpackage and board level reliability. Since thetechnology marks the convergence of fab,assembly and test, discussion will also addresssome fundamental issues such as: Where wouldit fit best (front end or back end)? Will it beapplicable and cost-effective for complex devicessuch as microprocessors? Are current standards(design rules, outline, reliability, etc.) applicable?

Course Outline:• Wafer level-chip scale packaging

(WL-CSP) - definition• Market drivers for WL-CSPs• Benefits of WL-CSPs• Barriers and challenges for WL-CSPs• Review of current WL-CSPs in the industry• Wafer level testing - status and challenges• Infrastructure service providers• Future trends: lead-free, large die size, wafer

level underfill

Who Should Attend:The course will be useful to the following threegroups of engineers and scientists:1. Newcomers to the field who would like toobtain a general overview of WL-CSP; 2.Thosewho are already practicing research anddevelopment of IC packaging and would like tolearn new methods for solving CSP problems;and, 3. Those who are currently consideringWL-CSP as a potential CSP alternative for theirinterconnect systems.

11. MICROVIAS & HIGH-DENSITYINTERCONNECTS FOR ADVANCED

PACKAGINGInstructor: Ricky Lee,Hong Kong University

of Science and Technology

Course Objectives:This course will introduce the cutting-edgeinformation on the most important developmentand latest research results in applying microviasand high-density interconnect technologies toadvanced packaging. For professionals active inmicroelectronic packaging research anddevelopment, those who wish to master highdensity interconnect technologies, and thosewho need to choose a cost-effective design andhigh-yield manufacturing process for theirelectronic systems, this is a timely summary ofprogress in all aspects of this fascinating field.The lecture contents are based on theinstructor's books on electronic packaging, hisrecent research results, and interactions with thepackaging and assembly industries. The scope ofcourse covers flip chip and CSP technologies,wafer-level packaging, microvias and build-upsubstrates, and emerging high-density

interconnect technologies. With the informationprovided in this lecture, the attendees willacquire a practical understanding in the design,materials, processes, analysis, and reliability issuesof high-density interconnection technologies.

Course Outline:• Overview of area array and high-density

interconnect technologies• Solder-bumped flip chip & wafer level chip

scale packages• Formation of microvias on silicon wafer• Formation of microvias on organic substrate• Copper-plated and conductive

paste/ink-filled microvias• Special high-density interconnect

technologies • PCB/substrate with sequential build-up layers• Reliability issues of high-density

interconnects

Who Should Attend:This short course is intended for researchscientists, professional engineers and technicalmanagers who are involved in IC packaging,component assembly, materials and processing,contract manufacturing and marketing.

12. INTERCONNECT ANDPACKAGING TECHNOLOGIES

FOR 10 AND 40GBPS TELECOM AND DATACOM

Protocols, Design, and Case StudiesInstructors: Roberto Coccioli,

Inphi Corporation andHassan Hashemi

Mindspeed Technologies, Inc.

Course Objectives:The objectives of this course are to reviewchallenges in 10G and 40G IC packagingconsidering requirements posed by mixed ICtechnologies and system architecture as definedin industry Multi Source Agreements. Moreover,it is intended to review the technologies availableto realize package and board interconnectsassessing their relative performance and theirimpact on signal integrity on high-speed digitalsignaling.The course material is based upon theinstructors' experience on current practices used for GHz IC packaging for telecom, storage,and datacom applications.

Course Outline:• Review of 10G & 40G system features &

packaging challenges• OE systems requirements and protocols• Standards for 10Gbps and 40Gbps

transponders• Substrate technologies for 10Gpbs and

40Gbps applications• Ceramic: thick-film, thin-film, HTCC,

LTCC, low resistance multilayer alumina

• Organic: high Tg FR4/BT, PTFE glass fiber,PTFE ceramic

• Leadframe based chip-scale packages• Effects of interconnects on signal integrity• First level interconnect: wirebonds, ribbons

and flip-chip• Transmission lines: CPW, microstrip,

stripline• Second level interconnect: BGA, LGA,

QFP, QFN• Connectorized packages for 10Gbps and

40Gbps ICs• Connector types: threaded & push-on• 10Gbps and 40Gbps IC package design

examples• Manufacturing tolerances and their effects

on performance• Conclusions

Who Should Attend:The course is designed for engineers orengineering managers who want to understandmore about technical challenges of high-speedpackaging, trends, and the unique requirementsposed on technology selection and design toassure the achievement of stringent electricaland thermal performance in cost-performanceefficient manufacturing.

13. PACKAGE FAILURE ANALYSIS -FAILURE MECHANISMS AND

ANALYTICAL TOOLSInstructors: Deepak Goyal

and Rajen DiasIntel Corporation

Course Objectives:The seminar will provide an overview of thefailure modes and mechanisms observed in theplastic packages. A brief introduction to themethodology of failure analysis of these packageswill be described. Emphasis will be paid to thetools and techniques currently used and thefuture direction for the tools and techniquesrequired for successful and timely failure analysisof next generation package technologies.

Course Outline:• Package technology; trends, drivers &

challenges• Failure analysis challenges offered by package

technology roadmap• Overview of the failure modes and

mechanisms observed in the organic packages

• Introduction to the methodology of failure analysis of organic packages

• Current analytical capabilities for package fault isolation and failure analysis

• Analytical capabilities to support next generation packaging

11

12

Who Should Attend:Engineers and technical managers who areinvolved in package technology development,reliability assessment of packages and failureanalysis.

14. ADVANCED THERMALMANAGEMENT MATERIALS

Instructor: Carl ZwebenAdvanced Thermal Management

Course Objectives:This PDC presents an in-depth overview of theincreasing number of advanced thermalmanagement materials that are continuallyemerging to solve critical design problems: heatdissipation, thermal stresses, size, weight andelectromagnetic emissions. Advantages include:thermal conductivities up to four times that ofcopper; low, tailorable coefficients of thermalexpansion; tailorable electrical conductivity; highstrengths and stiffnesses; low densities; net shapefabrication processes. Payoffs include: increasedreliability; reduced thermal stresses and warpage;reduced electromagnetic emissions; simplifiedthermal design; weight savings up to 90%; sizereductions up to 65%; increased manufacturingyield; potential cost reductions. Advancedmaterials are now being used in high-volumecommercial and aerospace productionapplications, including hybrid vehicles, trains, windturbine generators, servers, cellular telephonebase stations, cellular telephones, laptops, high-power radars, spacecraft electronics, avionics, etc.Components include IGBT packages, heatspreaders, heat sinks, microprocessor unit lids,solid and flow-through PCB cold plates,microwave modules, optoelectronic packages,etc. This PDC compares traditional packagingmaterials with the large and increasing numberof advanced thermal management materials,which include: diamond particle-reinforcedcopper, aluminum, cobalt and silicon carbide;silicon-carbide-particle-reinforced aluminum(Al/SiC) and copper; carbon-fiber-reinforcedpolymers, aluminum and copper; beryllia-particle-reinforced beryllium; carbon/carbon composites;natural and highly oriented pyrolitic graphite;"ThermalGraph", etc. Topics include properties,processes, applications, costs, increasingmanufacturing yield and future directions.

Course Outline:• Introduction: design drivers;

material requirements; example of successfuladvanced materials - Al/SiC

• Material property and test method issues• Traditional packaging materials• Advanced materials overview:

monolithic materials; classes of composites• Monolithic carbonaceous materials

• Reinforcements: carbon fibers;diamond particles; carbon nanotubes

• Metal matrix composites - Part 1• Metal matrix composites - Part 2 • Metal/metal alloys-composites• Carbon, polymer matrix and ceramic matrix

composites• Manufacturing processes• Solving manufacturing problems and increase

yield with composites• Cost issues • System applications: servers, laptops, avionics,

base stations, hybrid vehicles etc.• Component applications: modules, heat

spreaders and sinks, cold plates, enclosures,optoelectronics, etc.

• Future trends

Who Should Attend:Engineers and managers involved in electronicpackaging design, production and R&D. Packagingmaterial suppliers. Since many of the materialscovered are new and not widely known, thePDC will benefit both novice and experiencedpersonnel.

15. INTRODUCTION TO NANOSCALEPACKAGING AND SYSTEMS

Instructors: Rao Tummala, GeorgiaInstitute of Technology - Packaging

Research Center and Zhong L. 'ZL' Wang,Georgia Institute of Technology - Center

for Nanoscience and Nanotechnology

Course Objectives:This course introduces nanoscale packaging asan important emerging technology. As thesemiconductor industry approaches an historictransition toward nanoscales of 100nm, and withmore than 10,000 I/Os and 150 watts/chip, it isbecoming clear that nano-packaging is necessary.Nano-packaging comes at two levels: IC andsystems, together leading to nano-systems in adecade. Wafer-level packaging, with materialssuch as solders at 20 micron pitch, fail due topoor fatigue resistance. Compliant structures,on the other hand, are expensive and have toohigh an inductance and electrical resistance.However, nano-interconnections provide anopportunity to have the best of both electricaland mechanical properties, in addition to lowcost and at-speed test and burn-in benefits notpresently available. Today's systems packagingconsists of bulk dielectrics, conductors formultilayer wiring; capacitors, resistors, inductors,filters for RF; and waveguides and detectors foroptoelectronics interconnections, high thermalconductivity materials and designs for heattransfer, solders with underfills for assembly. Canthese be scaled down to nano-dimensions withimproved properties so as to end up withsystems paradigms? This course reviews the

status of and presents potential opportunitiesthat nanoscience and packaging technologyprovide in each of the above.

Course Outline:• Nanotechnology, what is it?• Nanotechnology, why now?• What is nano-packaging? Why now?• Some research directions in nanopackaging:

Nano devices- CMOS and its nanoroadmapNanotubes and nanointerconnects- Materials growth- Self-assembly techniques- Property measurements- Integration with devicesNano IC packaging

• Nanosensors- Quantom dots- Bioapplications of quantum dot- Wireless and electric signal based sensors- Integration of sensors with microsystems- Cantilever based sensors

• Nanowires and nanobelts-based devices- Field effect transistors- Biosensing- Piezoelectric nanobelts- Resonators- Cantilevers- Transducers and sensors

• Nanobioelectronics and fluidics• Summary and outlook

Who Should Attend:This course is an overview and introductorycourse and is suitable for all levels of R&Dmanagement, senior engineers and executivesinvolved in technical strategy, future R&Dinvestments, assembly manufacturing processesand product development of electronicpackaging and systems in automotive, consumer,communication, computer, biomedical, andaerospace industries.

16. LEAD-FREE SOLDERS FORROBUST IC ELECTRONIC AND

OPTOELECTRONIC PACKAGINGInstructor: John H. LauAgilent Technologies, Inc.

Course Objectives:Since February 13, 2003, lead-free has been a lawin EU (European Union). The implementationdate is July 1, 2006. That means, after July 1st, allthe electronic products (except those withexemptions) cannot be made in and shipped toEU. At the time being, China is considering toadopt this law. Recently, packages such as PBGA(plastic ball grid array), CSP (chip scale package),and especially WLCSP (wafer level chip scalepackage) have been very popular for consumer,computer, communication, optoelectronic, and

optical MEMS (micro-electro-mechanical system)products. Most of these packages use solders astheir interconnects, thus they are affected by thelead-free regulations. In this course, some criticalissues of lead-free soldering (such as cost,regulations, definitions, design, materials, forward-and backward-process incompatibility, andreliability of components, PCBs, tin whiskers, andsolder joints) will be presented. Also, somecritical issues of PBGA, CSP, WLCSP,optoelectronic, and optical MEMS will bediscussed. The impacts of lead-free on PBGA,CSP,WLCSP, optoelectronic, and optical MEMSare examined. Most of the materials are basedon the instructor's and his co-authors’ (C. P.Wong, Ricky Lee, N. C. Lee, John Prince,Yi-HsinPao and Wataru Nakayama) recently publishedtextbooks, "Solder Joint Reliability of BGA, CSP,Flip Chip, and Fine Pitch SMT Assemblies","Electronics Packaging", "Chip Scale Packages","Low-Cost Flip Chip Technologies for DCA,WLCSP, and PBGA Assemblies", "Microvias forLow-Cost High-Density Inter-connects", and"Electronics Manufacturing with Lead-Free,Halogen-Free, and Conductive AdhesiveMaterials". (McGraw-Hill publishes all thesebooks.) Each participant will receive acomprehensive set of handout notes. Aftercompleting this course, you will be able to:Understand all important aspects and criticalissues of lead-free soldering; Have a head-start oflead-free soldering for your green products;Understand all important aspects of BGA,WLCSP, and flip chip technologies; Understandall important aspects of optoelectronic andMEMS technologies; Understand the realmeaning of reliability; Identify key parametersthat impact the lead-free solder joint reliability ofyour products; Avoid potential reliabilityproblems due to lead-free soldering of yourhigh-density products; Choose a cost-effectivedesign of your high-density electronic andoptoelectronic assemblies; Establish a high-yieldmanufacturing process.

Course Outline:• Introduction • IC trends and IC packaging technology

update• Optoelectronic and optical MEMS packaging• Lead-free soldering• Printed Circuit Boards (PCBs)• Wave soldering technology • Surface mount technology • Flip-chip WLCSP technologies with solders • Flip-chip WLCSP technologies with

conductive adhesives • Optoelectronic with lead-free technology• Optical MEMS with lead-free technology• Discussions

Who Should Attend:If you are involved with any aspect of theelectronics industry, you should attend thiscourse. The content is recommended forcomponent, packaging, design, material, process,

equipment, reliability, product assurance, qualitycontrol, manufacturing, vendor, marketing, andsales engineers and managers. It is equally suitedfor R&D engineers and scientists.

Continuing Education Units

The IEEE Components, Packaging and Manufacturing Technology Society (CPMT)has been authorized to offer Continuing Education Units (CEUs) by theInternational Association for Continuing Education and Training (IACET) for allShort Courses that will be presented at the 54th ECTC. CEUs are recognized byemployers for continuing professional development as a formal measure ofparticipation and attendance in “non-credit” self-study courses, tutorials, symposiaand workshops. IEEE CPMT CEUs can be applied towards the newly created“IEEE CPMT Professional Development Certificate.” Complete details, includingvoluntary enrollment forms, will be available at the conference. All costsassociated with ECTC Professional Development Courses CEUs will beunderwritten by the conference, i.e. there are no additional costs for ProfessionalDevelopment Courses attendees to obtain CEU credit.

IMPORTANT NOTICEAM Short Courses 1 through 8 or PM Short Courses 9 through 16 run

concurrently. Make sure you indicate specific course numbers you plan toattend on page 31.The cost of each session (AM or PM) is $350. If you plan

to attend both AM and PM courses, registrationfor all-day is $550.The student all-day course registration fee is $75.

13

Photograph courtesy of Las Vegas News Bureau

Wednesday, June 2Session 1: SIP/SOP8:00 – 11:40 AMCommittee:AdvancedPackaging

Session Co-Chairs:Jeffrey A. Knight - EndicottInterconnect Technogies, INC.Tel: +1-607-755-1105Fax: +1-607-755-6400Email: [email protected]

Gary Morrison - TexasInstruments, Inc.Tel: +1-972-995-4851Email: [email protected]

High Density and Compliant Wafer-Level Electrical and OpticalPolymer Pilar Chip I/OInterconnectionsMuhannad Bakir and James Meindl -Georgia Institute of Technology

MAP (Mobile AGP Processor) - AHigh- Performance IntegratedGraphics ModuleRaj Pendse, M.Yee, J. S.Yun and BretZahn - ChipPAC Inc.; Bob Jafari,TimLau, Mihalis Michael, Inderjit Singh andOrion Starr - NVIDIA Corp.

System-on-a-Package (SOP)Substrate and Module with Digital,RF and Optical IntegrationVenky Sundaram, Rao Tummala, GeorgeWhite, Kyutae Lim, Lixi Wan, DanielGuidotti, Fuhan Liu, Ravi Doraiswami,Joy Laskar, G. K. Chang, ManosTentzeris and Madhavan Swaminathan -Georgia Institute of Technology

Process Development and Reliabilityfor System-in-a-Package UsingLiquid Crystal PolymerLiu Chen and Johan Liu - ChalmersUniversity of Technology; XinzhongDuo - Royal Institute of Technology

Physical Design of OptoelectronicSystem-on-a-Package Using OpticalWaveguide InterconnectsChung-Seok (Andy) Seo and AbhijitChatterjee - Georgia Institute ofTechnology; Nan M. Jokerst - DukeUniversity

Thermal Limits of Fine PitchExposed Pad TQFP SIP for HardDisc Drive ApplicationsTiao Zhou - Texas Instruments; BillRugg - Seagate

Physical Layout Automation forSystem-On-PackagesRamprasad Ravichandran, Jacob Minz,Mohit Pathak, Siddharth Easwar andSung Kyu Lim - Georgia Institute ofTechnology

Wednesday, June 2Session 2: Pb-Free Flip-ChipInterconnections I8:00 – 11:40 AMCommittee:Interconnections

Session Co-Chairs:Dev Gupta - Advanced Packaging& Systems TechnologyTel: +1-480-540-3232Email: [email protected]

Jong-Kai Lin - Motorola, Inc.Tel: +1-480-413-3254Fax: +1-480-413-4511Email: [email protected]

Assembly and Reliability of FlipChip Solder Joints UsingMiniaturized Au/Sn BumpsMatthias Hutter, Florian Hohnke,Hermann Oppermann, Matthias Kleinand Gunter Engelmann - FraunhoferIZM

A Low-Cost Plated Column BumpFlip Chip Technology for Sub-100umPitch and WLP ApplicationsDev Gupta, C. Holland and M. Fria -APSTL

FCOB (Flip Chip on Board)Reliability Study for MobileApplicationsSe-Young Jang, Soon-Min Hong, Hyun-Wook Nam, Min-Young Park, Sang-Hoon Roh and Young-Joon Moon -Samsung Electronics Co., Ltd.; Dong-Ok Kwak - Samsung AdvancedInstitute of Technology

Effect of Intermetallic Compoundson Reliability in Sn-Ag-Cu Flip ChipSolder Bumps for Different UBMsand Substrate Pad FinishesPiyush Gupta, Ravi Doraiswami andRao Tummala - Georgia Institute ofTechnology; Kensuke Nakanishi -Harima Chemicals

Study of Spalling Behavior ofIntermetallic Compounds Duringthe Reaction between ElectrolessNi(P) Metallization and Lead-FreeSoldersYoon-Chul Sohn and Jin Yu - KoreaAdvanced Institute of Science andTechnology; Sung K. Kang and Da-YuanShih - IBM T. J.Watson ResearchCenter;Taek-Yeong Lee - HanbatNational University

Reliability of Lead-Free CopperColumns in Comparison with Tin-Lead Solder Column InterconnectsRahul Joshi and Seungbae Park - StateUniversity of New York, Binghamton;Lewis Goldmann - IBM Corporation

Experimental Characterization andMechanical Behavior Analysis onIntermetallic Compounds of 96.5Sn-3.5Ag and 63Sn-37Pb Solder Bumpwith Ti-Cu-Ni UBM on Copper ChipChih-Tang Peng, Chia-Tai Kuo and Kuo-Ning Chiang - National Tsing HuaUniversity;Terry Ku and Kenny Chang -VIA Technology Corporation

Wednesday, June 2Session 3: Innovative TestingMethods8:00 – 11:40 AMCommittee: Quality &Reliability

Session Co-Chairs:Charles Ume - Georgia TechTel: +1-404-894-7411Fax: +1-404-894-9342Email:[email protected]

Dongji Xie - FlextronicsInternationalTel: +1-408-576-7597Fax: +1-408-576-7988Email:[email protected]

Prediction of Process-InducedWarpage of IC PackagesEncapsulated with ThermosettingPolymersD. G.Yang, K. M. B. Jansen and L. J. Ernst- Delft University of Technology; G. Q.Zhang - Philips-CFT;W. D. van Drieland H. J. L. Bressers - PhilipsSemiconductors; X. J. Fan - Philips

Towards a Predictive Behavior ofNon-Conductive AdhesiveInterconnects in MoistureEnvironmentJo Caers, Xiujuan Zhao and Hansen G.Sy - Philips Electronics Singapore; EeHua Wong - Institute ofMicroelectronics (IME), Singapore;Subodh Mhaisalkar - NTU, Singapore

Detection of Flip Chip Solder JointCracks Using CorrelationCoefficient Analysis of LaserUltrasound SignalsLizheng Zhang and I. Charles Ume -Georgia Institute of Technology;Juergen Gamalski and Klaus-PeterGaluschki - Siemens AG

Mechanical Characterization of Sn-Ag-Based Lead Free SoldersMasazumi Amagai - Texas Instruments,Inc.

Microstructural andMicromechanical Characterisationof Sn-Ag-Cu Solder FCOBInterconnects at Ambient andElevated TemperaturesChangqing Liu, Dezhi Li and PaulConway - Loughborough University

In-Process Measurement of theInterfacial Fracture Toughness for aSub-Micron Titanium Thin Film andSilicon Interface Using a Single StripDecohesion TestJiantao Zheng and Suresh K. Sitaraman- Georgia Institute of Technology

Determination of FractureToughness of Underfill/ChipInterface with Digital Image SpeckleCorrelation TechniqueZhang Yanlie and Zhou Wei - NanyangTechnological University; Shi Xunqing -Singapore Institute of ManufacturingTechnology

Wednesday, June 2Session 4: Adhesives andEncapsulants8:00 – 11:40 AMCommittee: Materials &Processing

Session Co-Chairs:Johan Liu - Chalmers Universityof TechnologyTel: +46-31-706-6294Fax: +46-31-706-6289Email: [email protected]

Chandra Jayaram - IntelTechnology Sdn. Bhd.Tel: +604 253 5289Fax: +604 253 6507Email:[email protected]

Electrical and ThermalConductivities of PolymerComposites Containing Nano-SizedParticlesLianhua Fan, Bin Su, Jianmin Qu and C.P.Wong - Georgia Institute ofTechnology

Development on Wafer LevelAnisotropic Conductive Film forFlip-Chip InterconnectionJean-Charles Souriau, Jean Brun, RemiFraniatte and Gasse Adrien - CEA-Grenoble-LETI

Anisotropic Conductive Adhesiveswith Enhanced ThermalConductivity for Flip-Chip ApplicationsMyung Jin Yim, Jin Sang Hwang and JinGu Kim - Telephus, Inc.;WoonseongKwon, Kyung Woon Jang and Kyung-Wook Paik - Korea Advanced Instituteof Science and Technology

Reliability Enhancement ofElectrically Conductive Adhesives inThermal Shock EnvironmentHaiying Li, Kyoung-Sik Moon,Yi Li andC. P.Wong - Georgia Institute ofTechnology

Integration of Low StressPhotopatternable Silicones into aWafer Level PackageGeoff Gardner, Brian Harkness andHerman Meynen - Dow Corning;Mario Gonzales, Mathieu VandenBulcke, Bart Vandevelde and Eric Beyne- IMEC

Emerging Challenges of Underfill for Flip-Chip ApplicationTim Chen - Intel Corp.

Hygro-Thermo-MechanicalBehavior of Mold CompoundMaterials at Elevated EnvironmentSung Yi and Zeyan Yu - Portland StateUniversity; Raynard Neo - Micron;Yeong Lee - Dow Corning

Program Sessions

14

15

Wednesday, June 2Session 5: Low CostOptoelectronic PackagingTechnology8:00 – 11:40 AMCommittee:Optoelectronics

Session Co-Chairs:Alan J. Morrow - BinOpticsCorporationTel: +1-607-257-3200 x236Fax: +1-607-257-9753Email: [email protected]

Andrew Shapiro - University ofCalifornia, IrvineTel: +1-949-824-8086Fax: +1-949-824-2541Email: [email protected]

Reliability Concerns and PackagingIssues of Non-Hermetic VCSEL- andLED-Based Transceivers for theEnterprise MarketWilliam Ring, Peter Thambinayagam,Wayne Hobson, Henry Meehan, MingLiang and Peter Silbermann - TycoElectronics, Inc.

Optical SMT-Packaging for HighlyEfficient and Reliable Fiber OpticComponents Including 1300nmVCSELsHans L.Althaus, Marco Melinde,Gunther Steinle, Martin Weigert andHelmut Wietschorke - InfineonTechnologies AG

A Low-Cost Plastic Package for2.5Gbps Optical TransceiverModules with High ElectromagneticShieldingTzong-Lin Wu,Wen-Chi Hung, Chien-Hui Lee, Cheng-Wei Lin and Wood-HiCheng - National Sun Yat-senUniversity; Wern-Shiarng Jou -National Kaohsiung University ofApplied Sciences

Low-Cost Optical Subassemblies forMetro Access ApplicationsWilliam Hogan, Robert Wolf,AnandShulka and Phil Deane - JDS UniphaseCorp.

Unique 1 TO Structure Low-CostOptical SubassemblyMasahiko Tsumori, Sun Hyoung Pyo,Joong Hee Lee,Young kwon Yoon andTaeil Kim - Samsung Electronics Co.,Ltd.

Packaging of a High-Speed OpticalModulator Using Flip-ChipInterconnectsYuvaraja Visagathilagar,Wayne Roweand Arnan Mitchell - RMIT University

Ultra Compact OpticalSubassembly Using Integrated LaserDiode and Silicon Microlens forLow-Cost Optical ComponentsDaisuke Shimura, Masahiro Uekawa,Ryo Sekikawa, Kyoko Kotani,YoshinoriMaeno, Hironori Sasaki and TakeshiTakamori - Oki Electric Industry Co.,Ltd.

Wednesday, June 2Session 6: ElectricalModeling8:00 – 11:40 AMCommittee: Modeling &Simulation

Session Co-Chairs:George A. Katopis - IBMCorporationTel: +1-914-435-6719Fax: +1-914-435-1593Email: [email protected]

Bruce Kim - Arizona StateUniversityTel: +1-480-965-3749Fax: +1-480-965-3837Email: [email protected]

A Fast Full-Wave ModelingMethodology for StriplineStructures with VerticalInterconnects in Multi-LayerDielectricsKonstantinos Nikellis - Helic S.A. -National Technical University of Athens;Yorgos Koutsoyannopoulos and SotirisBantas - Helic S.A.; Nikolaos Uzunoglu- National Technical University ofAthens

An Efficient Finite Element-BasedElectromagnetic Field ModelingMethodology for InterconnectStructures Including Lumped CircuitElementsHong Wu and Andreas Cangellaris -University of Illinois at Urbana-Champaign

An Efficient Full-Wave LayeredInterconnect Simulator (UA-FWLIS)Xing Wang, Zhaohui Zhu, StevenDvorak and John Prince - University ofArizona

Very High-FrequencyCharacterization of High-Density 3-D ModuleMatti Mäntysalo, Jarmo Tanskanen andEero O. Ristolainen - TampereUniversity of Technology

Modeling and Optimization ofMultilayer LTCC Inductors forRF/Wireless Applications UsingNeural Networks and GeneticAlgorithmsRana Pratap, Saikat Sarkar, StephanePinel, Joy Laskar and Gary May -Georgia Institute of Technology

A Simplified Cross Coupling Modelfor Multiple Balanced TransmissionLinesDavid Quint, Karl Bois and Yong Wang- Hewlett Packard Company

Characterization of DiscreteDecoupling Capacitors for High-Speed Digital SystemsJoong-Ho Kim, Dan Jiao, Jiangqi He,Kaladhar Radhakrishnan andChanghong Dai - Intel Corporation

Wednesday, June 2Session 7: IntegratedCapacitor and ResistorTechnology8:00 – 11:40 AMCommittee: Components& RF

Session Co-Chairs:Leonard W. Schaper - Universityof ArkansasTel: +1-479-575-8408Fax: +1-479-575-2719Email: [email protected]

Li Li - Motorola, Inc.Tel: +1-480-413-6653Fax: +1-480-413-4511Email: [email protected]

Advanced Decoupling in High-Performance IC PackagingDeepa Mannath, Leonard Schaper andRichard Ulrich - University of Arkansas

Novel Flexible and Thin Capacitorswith Mn-Doped SrTiO3 Thin Filmson Polyimide FilmsShintaro Yamamichi and AkinobuShibuya - NEC Corporation

Thin-Film Low InductanceDecoupling Device for High SpeedDigital CircuitsJunya Takafuji, Shigeo Konushi, HisashiNakashima, Seiji Ueda, FumioFukumaru and Shinji Nambu - KyoceraCorporation

Simultaneous Switching NoiseSuppression Using HydrothermalBarium Titanate Thin- FilmEmbedded CapacitorsDevarajan Balaraman,Vijay Patel, P.Markondeya Raj, Lixi Wan, MichaelSacks, Isaac R.Abothu, MadhavanSwaminathan and Rao Tummala -Georgia Institute of Technology

Design and Performance ofPolymeric Ultra-Thin Substrates forUse as Embedded CapacitorsJohn Andresakis,Takuya Yamamoto andPranbes Pramanik - Oak-MitsuiTechnologies; Nicholas Biunno -Sanmina-SCI

Thin-Film Integration of Passives -Single Components, Filters,Integrated Passive DevicesKai Zoschke, M. Jürgen Wolf, OswinEhrmann,Thomas Fritzsch, KatrinScherpinski, Michael Töpper andHerbert Reichl - Fraunhofer IZM;Franz-Josef Schmückle - Ferdinand-Braun-Institut (FBH)

Design and Fabrication of anAutomotive Engine Controller UsingEmbedded Passive Technology forPWBJohn Myers and Jiming Zhou - DelphiElectronics and Safety

16

Wednesday, June 2Session 8: Flip-ChipPackaging1:30 – 5:10 PMCommittee:AdvancedPackaging

Session Co-Chairs:Raj N. Master - AMDTel: +1-408-982-7023Fax: +1-408-982-6164Email: [email protected]

Raj Pendse - ChipPAC, Inc.Tel: +1-510-979-8330Fax: +1-510-979-8009Email:[email protected]

IXP2400 NPU PackageDevelopmentAndreh Janian,Altaf Hasan,AdamBarrett and Upendra Sheth - IntelCorporation

High Speed DDR Performance in 4vs. 6 Layer FCBGA Package DesignEdward Chan, Huabo Chen and CheeYee Chung - NVIDIA Corporation

NanoLinks: Lithography-BasedWafer-Level Compliant Chip-to-Substrate InterconnectsSuresh Sitaraman and George Lo -Georgia Institute of Technology

BGA Ball Field Interaction withManufacturing and DesignAltaf Hasan and Daryl Sato - IntelCorporation

Gbps High-Speed ElectricalCharacteristics of Flip-Chip BGAPackage Exceeding 2,000pin CountsKazuyuki Nakagawa, Masaki Watanabe,Shinji Baba and Michitaka Kimura -Renesas Technology Corp.; KeitaroYamagishi,Yuuichi Sasaki,TomoyukiKamiyama and Masaaki Namatame -Mitsubishi Electric Corporation

Wednesday, June 2Session 9:Wirebond1:30 – 5:10 PMCommittee:Interconnections

Session Co-Chairs:Wolfgang Sauter - IBMMicroelectronicsTel: +1 802 769 3634Fax: +1 802 769 1038Email: [email protected]

Rajen Dias - Intel CorporationTel: +1-480-554-5202Fax: +1-480-554-7171Email: [email protected]

Manufacturability and Reliability ofDifferent Size Wirebonds onDifferent Al Pad StructuresWolfgang Sauter and Kevin Ostrowski- IBM Corporation;Toyohiro Aoki andTakashi Hisada - IBM Japan, Ltd.;Frederic Beaulieu and Stephanie Allard- IBM Canada, Ltd.

Wire Bonding on a Novel ImmersionGold-Capped Copper-MetallizedIntegrated CircuitGanesh Vetrivel Periasamy, KripeshVaidyanathan and Chih Hang Tung -Institute of Microelectronics; Loon AikLim - ASM Singapore

Assembly Process Development of50um Fine Pitch Wire BondedDevicesYufeng Yao, Zhengpeng Xiong, Xin Guand Simon Chua - Agere SystemsSingapore Pte Ltd.;Tingyu Lin -Motorola Electronics Pte Ltd.Singapore

Changes in Wirebond Integrity andReliability as Wirebond PitchDecreasesToyohiro Aoki and Takashi Hisada - IBMJapan, Ltd.;Wolfgang Sauter - IBMCorporation

A Study on the Reliability and Thermo-Mechanical Properties of The Gold Ribbon Wire BondingChee Wei Tan and Yan Cheong Chan -City University of Hong Kong; HongDu Liu and Bernard N.W. Leung -Photonic Manufacturing Service Ltd.

Thermosonic Wire Bonding ProcessSimulation and Bond Pad overActive (BPOA) Stress AnalysisYong Liu, Scott Irving and Timwah Luk- Fairchild Semiconductor Corporation

Radio Frequency Characterizationof Bonding Wire Interconnections ina Molded ChipJun Yi Chuang, Sung Pi Tseng and J.Andrew Yeh - National Tsing HuaUniversity

Wednesday, June 2Session 10: Characterizationof Failure Mechanisms inAdvanced Packagaing1:30 – 5:10 PMCommittee: Quality &Reliability

Session Co-Chairs:Darvin R. Edwards - Texas Instruments, Inc.Tel: +1-972-995-3569Fax: +1-972-995-2658Email: [email protected]

Jeffrey Suhling - AuburnUniversityTel: +1-334-844-3332Fax: +1-334-844-3307Email: [email protected]

Gold Embrittlement of Solder Jointsin Wafer-Level Chip Scale Packageon Printed Circuit Board with Ni/AuSurface FinishingS.W. Ricky Lee - Hong Kong Universityof Science and Technology; XingjiaHuang - Foxconn Inc.; Ming Li -Chinese University of Hong Kong;William Chen - ASE Technologies Inc.

Development of BGA Solution forthe IBM PowerPC 970 Module inApple’s G5 SystemDavid Edwards, Mukta Farooq andLewis Goldmann - IBM Corporation;Hope Chambers and Amir Salehi -Apple Computer

Failure Analysis and VirtualQualification of PBGA UnderMultiple Environmental LoadingsHaiyu Qi, Chris Wilkinison, MichaelOsterman and Michael Pecht -University of Maryland

Modeling Thermo-MechanicalReliability of Bumpless Flip-ChipPackageJohn H. L. Pang and T. H. Low -Nanyang Technological University;Charles Lin and Andrew Yang - BridgeSemiconductor

Thermo-Mechanical Reliability ofPower Flip-Chip Cooling ConceptsBernhard Wunderle, Rainer Dudek andMichel Bernd - Fraunhofer IZM; ReichlHerbert - Technical University of Berlin

Continuous Operation at 200CDevice Junction Temperature:TheFinal Frontier for RF PowerSemiconductor Plastic PackagingMali Mahalingam, Dave Abdo, FrankDanaher and Alex Elliott - Motorola,Inc.

Calculation of CriticalDelamination Size for Failure of thePad/Encapsulant Interface of PlasticIC Packages Undergoing SolderReflowAndrew Tay - National University ofSingapore;Yiyi Ma - Institute ofMicroelectronics;Toshio Nakamura -State University of New York, StonyBrook; Soon Huat Ong - NationalSemiconductor Manufacturing,Singapore

17

Wednesday, June 2Session 11: Nanoscale andEmerging Technologies1:30 – 5:10 PMCommittee: Special Topics

Session Co-Chairs:Jim Morris - Portland StateUniversityTel: +1-503-725-9588Fax: +1-503-725-3807Email: [email protected]