Ma131 Mathematics i Question Bank Question Bank Matrices: Part –a

NSCET-QUESTION BANK YR/QB/CA-QB.pdfNSCET-QUESTION BANK DEPARTMENT OF ELECTRONICS AND COMMUNICATION...

Transcript of NSCET-QUESTION BANK YR/QB/CA-QB.pdfNSCET-QUESTION BANK DEPARTMENT OF ELECTRONICS AND COMMUNICATION...

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

SEM-6 6th

Semester – B.E. / B.Tech.

BR-105 Department of Electrical and electronics Engineering

CS6303 COMPUTER ARCHITECTURE

Part-A (10 x 2 = 20 Marks)

UNIT – I

No Question Level Competence Mark

1.1 What are the eight great ideas in computer architecture? L2 Comprehend 2

1.2 What are the five classic components of a computer? L2 Comprehend 2

1.3 Define Computer Architecture L1 Knowledge 2

1.4 Differentiate DRAM and SRAM. L4 Analysis 2

1.5 Differentiate Throughput and Response Time L4 Analysis 2

1.6 Write the CPU performance equation. L1 Knowledge 2

1.7 Write the formula for CPU clock cycles required for a

program. L1 Knowledge 2

2.1 If computer A runs a program in 10 seconds, and computer

B runs the same program in 15 seconds, how much faster

is A over B.

L2 Comprehend

2

2.2 What are the fields in an MIPS instruction? L1 Knowledge 2

2.3 Write the formula for CPU execution time for a program. L1 Knowledge 2

2.4 Write an example for immediate operand. L1 Knowledge 2

Nadar Saraswathi College of Engineering and Technology,

Vadapudupatti, Theni - 625 531

(Approved by AICTE, New Delhi and Affiliated to Anna University, Chennai)

Format No. NAC/TLP-

07a.12

Rev. No. 01

Date 14-11-2017

Total Pages 01

Question Bank for the Units – I to V

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

2.5 Define – Addressing Modes L1 Knowledge 2

2.6 What are the different types ofoperands? Give examples L1 Knowledge 2

2.7 List the different addressing modes L1 Knowledge 2

UNIT - II

3.1 Add (6)10 to (7)10 in binary and Subtract (6)10 from (7)10

binary. L2 Comprehend

2

3.2 Write the overflow conditions for addition and subtraction. L1 Knowledge 2

3.3 List the steps of division algorithm L1 Knowledge 2

3.4 What is scientific notation and normalization? Give an

example L1 Knowledge

2

3.5 Define – Guard and Round L1 Knowledge 2

3.6 Subtract (11011)2 - (10011)2 L2 Comprehend 2

3.7 Divide(1001010)2 /(1000)2 . L2 Comprehend 2

4.1 Define Little Endian arrangement L1 Knowledge 2

4.2 What are the steps in the floating-point addition? L1 Knowledge 2

4.3 What is meant by sub-word parallelism? L1 Knowledge 2

4.4 For the following C statement, what is the corresponding

MIPS assembly code?

f = g + (h - 5)

L1 Knowledge 2

4.5 What is fast multiplication? L1 Knowledge 2

4.6 For the following MIPS assembly instructions above, what

is a corresponding C statement?

add f, g, h

add f, i, f

L1 Knowledge

2

4.7 What is meant by sticky bit? L1 Knowledge 2

UNIT – III

5.1 What is meant by data path element? L1 Knowledge 2

5.2 What is meant by register file? L1 Knowledge 2

5.3 Draw the diagram of portion of datapath used for fetching L1 Knowledge 2

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

instruction.

5.4 What is meant by branch target address? L1 Knowledge 2

5.5 What are the three instruction classes and their instruction

formats?

L1 Knowledge 2

5.6 Mention the various types of pipelining. L1 Knowledge 2

5.7 Differentiate branch taken from branch not taken. L4 Analysis 2

6.1 What is meant by pipelining? L1 Knowledge 2

6.2 What are the five steps in MIPS instruction execution? L1 Knowledge 2

6.3 What are hazards? Write its types. L1 Knowledge 2

6.4 What is pipeline stall? L1 Knowledge 2

6.5 What are exceptions and interrupts? L1 Knowledge 2

6.6 What is meant by forwarding? L1 Knowledge 2

6.7 What is meant by branch prediction? L1 Knowledge 2

UNIT-IV

7.1 What is meant by ILP? L1 Knowledge 2

7.2 What is multiple issue? Write any two approaches. L1 Knowledge 2

7.3 What is meant by loop unrolling? L1 Knowledge 2

7.4 What is meant by anti-dependence? How is it removed? L1 Knowledge 2

7.5 What is meant by speculation? L1 Knowledge 2

7.6 Define strong scaling and weak scaling. L1 Knowledge 2

7.7 Define Vector Processor. L1 Knowledge 2

8.1 What is the use of reservation station and reorder buffer? L1 Knowledge 2

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

8.2 Differentiate in-order execution from out-of-order

execution

L4 Analysis 2

8.3 What is meant by hardware multithreading? L1 Knowledge 2

8.4 What are the two main approaches to hardware

multithreading?

L1 Knowledge 2

8.5 Differentiate UMA from NUMA. L4 Analysis 2

8.6 Difference between Fine-grained multi threading and

Coarse grain multi threading L4 Analysis

2

8.7 Define a cluster L1 Knowledge 2

UNIT- V

9.1 What are the temporal and spatial localities of references? L1 Knowledge 2

9.2 Write the structure of memory hierarchy. L1 Knowledge 2

9.3 What is flash memory? L1 Knowledge 2

9.4 Differentiate programmed I/O and interrupts I/O L4 Analysis

2

9.5 Consider a cache with 64 blocks and a block size of 16

bytes. To what block number does byte address 1200 map? L1 Knowledge

2

9.6 How many total bits are required for a direct-mapped cache

With 16 KB of data and 4-word blocks, assuming a 32-bit

address?

L2 Comprehend

2

9.7 What are the various block placement schemes in cache

memory? L1 Knowledge

2

10.1 What is meant by virtual memory? L1 Knowledge 2

10.2 Differentiate physical address from logical address. L4 Analysis 2

10.3 What are the various block placement schemes in cache

memory?

L1 Knowledge 2

10.4 Define – TLB L1 Knowledge 2

10.5 Summarize the sequence of events involved in handling an L2 Comprehend 2

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

interrupt request from a single device.

10.6 Differentiate SRAM from DRAM. L4 Analysis 2

10.7 What is meant by address mapping? L1 Knowledge 2

Part – B ( 5 x 16 = 80 Marks) or Part – B ( 5 x 13 = 65 Marks)

UNIT- I

11.a-1 i)Discuss in detail about Eight great ideas of computer

Architecture.

ii) Explain in detail about Technologies for Building

Processors and Memory

L2 Comprehend

(6)

(7)

11.a-2 Explain the various components of computer System with

neat diagram

L2 Comprehend (13)

11.a-3 Discuss in detail the various measures of performance of a

computer L2 Comprehend (13)

11.a-4 Explain operations and operands of computer Hardware

in detail L2 Comprehend (13)

11.b-1 Explain various instruction format and illustrate the same

with example L2 Comprehend (13)

11.b-2 Discuss the Logical operations and control operations of

computer

L2 Comprehend (13)

11.b-3 Explain short notes on

i) Power wall

ii) Uni processor and Multiprocessor

L2 Comprehend

(13)

11.b-4 Define Addressing mode and explain the addressing

modes with an example for each.

L1 Knowledge

(13)

UNIT – II

12.a-1 Explain the sequential version of Multiplication algorithm

in detail with diagram and example (13) L2 Comprehend (13)

12.a-2 Explain the Multiplication algorithm in detail with

diagram and examples (13) L2 Comprehend (13)

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

12.a-3 Define Booth Multiplication algorithm with suitable

example. (13)

L1 Knowledge

(13)

12.a-4 Discuss in detail about division algorithm using non

restoring algorithm in detail with diagram and examples

L4 Analysis

(13)

12.b-1 Discuss in detail about division algorithm using restoring

algorithm in detail with diagram and examples

L4 Analysis

((13)

12.b-2 Divide (12)10 by (3)10 using both non restoring algorithm

and restoring algorithm. (13)

L4 Analysis (13)

12.b-3 Explain floating point representation with example (13) L2 Comprehend (13)

12.b-4 i) Design an arithmetic element to perform the basic

floating point operations

ii) What is meant by sub word parallelism?

L1

Knowledge (7)

(6)

UNIT - III

13.a-1 Explain the basic MIPS implementation of instruction set (13) L2 Comprehend (13)

13.a-2 Discuss the influence of pipelining in detail (13)

L1

Knowledge

(13)

13.a-3 Explain the data path in MIPS Implementation. L2 Comprehend (13)

13.a-4 Explain how the instruction pipeline works. What are the

various situations where an instruction pipeline can stall?

What can be its resolution? (13)

L2 Comprehend (13)

13.b-1 What is control hazards ?Explain the methods for dealing

with the control hazards. (13)

L1

Knowledge

(13)

13.b-2 What is data hazard? How do you overcome it? What are

its side effects? (13)

L1

Knowledge (13)

13.b-3 i) Explain the hazards caused by unconditional branching

statements

ii) Describe operand forwarding in pipeline processor with

a diagram

L2 Comprehend

(6)

(7)

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

13.b-4 Explain in detail the operation of the data path L2 Comprehend (13)

UNIT -IV

14.a-1 Explain Instruction level parallelism (13) L2 Comprehend (13)

14.a-2 Explain in detail about Flynn’s classification . L2 Comprehend (13)

14.a-3 Write short notes on :

i) HardwareMultithreading

ii) Multicoreprocessors

L2 Comprehend (6)

(7)

14.a-4 i) Discuss the challenges in parallel processing with

necessary examples

ii) Explain fylnn’s classification of parallel processing

with necessary diagram

L2 Comprehend

(6)

(7)

14.b-1 Explain SISD, MIMD ,SIMD and SPMD (13) L2 Comprehend (13)

14.b-2 i)Explain cluster and other Message passing

Multiprocessor

ii) Explain the different types of multithreading (7)

L2 Comprehend (6)

(7)

14.b-3 Describe Simultaneous Multi threading (SMT) with

example

L2 Comprehend (13)

UNIT V

15.a-1 Expain in detail about memory Hierarchy with neat

diagram

L2 Comprehend

(13)

15.a-2 Explain the virtual memory address translation and TLB

with necessary diagram. (13)

L2 Comprehend (6)

(7)

15.a-3 Draw the typical block diagram of a DMA controller and

explain how it is used for direct data transfer

between memory and peripherals.

L2 Comprehend (13)

15.a-4 Explain in detail about interrupts with diagram (13) L2 Comprehend (13)

15.b-1 Describe in detail about programmed Input/Output with L2 Comprehend (13)

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

neat diagram (13)

15.b-2 i) Describe the basic operations of cache in detail with

diagram

ii) Discuss the various mapping schemes used in cache

design

L2 Comprehend (6)

(7)

15.b-3 Elaborate on the various memory technologies and its

relevance. (13)

L1 Knowledge (13)

15.b-4 Explain the methods to improve cache performance

L2

Comprehend

(13)

Part – C ( 1 x 15 = 15 Marks)

UNIT-1

16 .a-1 i) Write down the MIPS code for if-then-else structure in C

ii) Write down the MIPS code for while loop structure in C

L1 Knowledge (8)

(7)

16 .a-2 Consider three different processors P1, P2, and P3 executing

the same instruction set. P1 has a 3 GHz clock rate and a

CPI of 1.5. P2 has a 2.5 GHz clock rate and a CPI of 1.0. P3

has a 4.0 GHz clock rate and has a CPI of 2.2.

a. Which processor has the highest performance expressed in

instructions per second?

b. If the processors each execute a program in 10 seconds,

find the number of cycles and the number of instructions.

c. We are trying to reduce the execution time by 30% but

this leads to an increase of 20% in the CPI. What clock rate

should we have to get this time reduction?

L2 Comprehend

15

(OR)

16.b-1 A Program runs in 10 seconds on computer A, which has a

2 GHz clock. We are trying to help a computer designer to

build a computer B, which will run this program in 6

seconds. The designer has determined that a substantial

increase in the clock rate is possible, but this increase will

affect the rest of the CPU design, causing computer B to

require 1.2 times as many clock cycles as computer A for

this program. What clock rate should we tell the designer

to target?

L2 Comprehend

15

16.b-2 Assume a two address format specified as source,

destination. Examine the following sequence of

instructions and identify the addressing modes used and the

operation done in every instruction.

1. Move (R5)+,R0

L2 Comprehend

15

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

2. Add (R5)+,R0

3. Move R0,(R5)

4. Move 16(R5),R3

5. Add #40,R5

UNIT-2

16 .a-1 i)Write down the binary representation of the decimal

number -0.7510 assuming the IEEE 754 single precision

format and double precision format.

ii)Explain the procedure for floating point addition

L2 Comprehend

15

16 .a-2 Add the numbers 0.510 and -0.437510using binary Floating

point Addition algorithm

L2 Comprehend 15

(OR)

16.b-1 Perform the division on the following 5-bit unsigned integer

using non-restoring division: 10101 / 00101.

L2 Comprehend

16.b-2 Multiply the following pair of signed 2’s complements

numbers using bit-pair-recoding of the multipliers: A=

010111, B=101100.

L2 Comprehend

15

UNIT-3

16 .a-1 List down the steps used in execution of the following types

of instructions with respect to the datapath

i) R- type instruction

ii) Load word instruction

iii) Branch on equal instruction

L2 Comprehend

15

16 .a-2 A Pipelined processor uses delayed branch technique.

Recommend any one of the following possibility for the

design of the processor. In the first possibility, the processor

has a 4-stage pipeline and one delay slot. In the second

possibility, it has a 6-stage pipeline and two delay slots.

Compare the performance of these two alternatives, taking

only the branch penalty into account. Assume that 20% of the

instructions are branch instructions and that an optimizing

compiler has an 80% success rate in filling in the single delay

slot. For the second alternative, the compiler is able to fill the

second slot 25% of the time.

L5 Evaluation

15

(OR)

16.b-1 Explain the function of a six segment pipelines and draw a

space diagram for a six segment pipeline showing the time it

takes to process eight tasks.

L2 Comprehend

15

16.b-2 i) Explain the hazards caused by unconditional branching

statements

L2

Comprehend 8

7

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

ii) Describe operand forwarding in pipeline processor with a diagram

UNIT-4

16 .a-1 Explain the difficulties faced by parallel processing programs

L2

Comprehend 15

16 .a-2 Explain the concept Instruction level parallelism L2

L

2

Comprehend

15

(OR)

16.b-1 i) Suppose you want to achieve a speed-up of 90 times faster

with 100 processors. What percentage of the original

computation can be sequential

ii) Suppose you want to perform two sums: one is a sum of 10

scalar variables and one is a matrix sum of a pair of two-

dimensional arrays, with dimensions 10by 10. For now let’s

assume only the matrix sum is parallelizable: we’ll as soon

how to parallelize scalar sums. What speed-up do you get with

10 versus processors?Next,calculate the speed-ups assuming

the matrices grow 20 by 20.

L2

Comprehend

8

7

UNIT-5

16 .a-1 Explain how data may be transferred from a hard disk to memory using DMA including arbitration for the bus,. Assume a synchronous bus, and draw a timing diagram showing the data transfer.

L2

Comprehend

15

16 .a-2 i) Describe the basic operations of cache in detail with diagram. ii) A byte addressable computer has a small data cache capable of holding eight 32-bit words. Each cache block contains 132-bit word. When a given program is executed, the processor reads data from the following sequence of hex addresses – 200, 204, 208, 20C, 2F4, 2F0, 200, 204,218, 21C, 24C, 2F4. The pattern is repeated four times. Assuming that the cache is initially empty, show the contents of the cache at the end of each pass, and compute the hit rate for a direct mapped cache. (15)

L2

Comprehend

15

(OR)

16.b-1 Explain the use of vectored interrupts in processors. Why is

priority handling desired in interrupt controllers? How do the

different priority schemes work?

L2

Comprehend

15

16.b-2 Assume the miss rate of an instruction cache is 20% and the

miss rate of the data cache is 4%. If a processor has a CPI of 2

without any memory stalls and the miss penalty is 100 cycles

L2

Comprehend 15

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

for all misses, determine how much faster a processor would

run with a perfect cache that never missed. Assume the

frequency of all loads and stores is 36 %

L1: Knowledge, L2: Comprehension, L3: Application, L4: Analysis, L5: Evaluation, L6: Synthesis

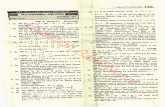

QUESTION BANK SUMMARY

S.NO UNIT DETAILS L1 L2 L3 L4 L5 L6 TOTAL

1 Unit-1

PART-A 9 3 2 14

PART-B 1 7 08

PART-C 1 3 04

2 Unit-2

PART-A 11 3 14

PART-B 2 3 3 08

PART-C 4 04

3 Unit-3

PART-A 13 1 14

PART-B 3 5 08

PART-C 4 04

4 Unit-4

PART-A 11 3 14

PART-B 7 07

PART-C 3 03

5 Unit-5

PART-A 9 2 3 14

PART-B 1 7 08

PART-C 4 04

Total No of Questions

PART-A PART-B PART-C TOTAL

70 39 19 128

Prepared By:

Staff Name1: Mrs.P.Latha

NSCET-QUESTION BANK

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

STAFF IN CHARGE HOD PRINCIPAL