NIL at hP - SCU · 2005. 5. 6. · UV-curable NIL with Double-layer Spin-on Resist 1. Prepare...

Transcript of NIL at hP - SCU · 2005. 5. 6. · UV-curable NIL with Double-layer Spin-on Resist 1. Prepare...

Nanoimprint Lithography

Wei WuQuantum Science ResearchAdvanced StudiesHP Labs, Hewlett-Packard

Email: [email protected]

April. 1, 2005 2

Outline

• Background• Nanoimprint lithography− Thermal based−UV-based

• Applications based on nanofabrication−Molecular memory and logic−Single electron memory− Patterned magnetic media

• Future work• Summary

April. 1, 2005 3

ITRS Lithography Requirements

2000 2002 2004 2006 2008 2010 2012 2014 2016 2018

20

40

60

80

100

120

140

DR

AM 1

/2 P

itch

(nm

)

Year

Source: ITRS 2002 update

April. 1, 2005 4

Nano is Great but…

• New frontier of scienceo Fundamental knowledgeo Convergence of physics, chemistry and biology.

•Potential commercial impactDNA Carbon nanotubes

Molecular electronics

• Technological challenge – Lithography!

April. 1, 2005 5

Microprocessor

A microprocessor (intel P4)

April. 1, 2005 6

Photolithography

..ANkW λ

=

Source: Britney Spears guide to Semiconductor physics

April. 1, 2005 7

Next generation lithography (NGL) tools:

Extreme UV lithography (EUV)–Extremely expensive

(complex optical system, expensive and fragile mask)

X-ray lithography–Expensive light source (synchrotron preferred)–Mask material

E-beam direct write lithography (EBL)–Extremely slow (serial process)

E-beam projection lithography (EPL)–Mask material–Distortion due to heat

April. 1, 2005 8

Extreme Ultraviolet (EUV) Lithography

Source: Lawrence Livermore National Lab

Expensive

•Reflective mask and optics require < 2.5Å accuracy.

•Low efficiency (a few percent) of the light source.

• Small resist absorption length.

April. 1, 2005 9

Time for Using EBL to Write Gratings on 4 inch Wafer

EBL I used in graduate school

Resist: 950K PMMA

Dose: 600µC/cm2

Current: 4.5 pA

Area: 4inch wafer with 50% duty cycle. ~40cm2

SpA

cmcmCCurrent

AreaDoseTime 922

1055.4

40/600×≈

×=

×=

µ

158 years!

April. 1, 2005 10

Nanoimprint Lithography (NIL)

1. Imprint mold

resist

substrate

•Press Mold

•Remove Mold

2. Pattern Transfer•RIE

Chou, Krauss, and Renstrom, APL, Vol. 67, 3114 (1995); Science, Vol. 272, 85 (1996)

April. 1, 2005 11

Nanoimprint Lithography (NIL)

10 nm

•High resolution-not limited by wavelength

•High throughput -parallel process

•Low cost

Chou, Krauss, and Renstrom, APL, Vol. 67, 3114 (1995); Science, Vol. 272, 85 (1996)

April. 1, 2005 12

Step & Flash Imprint

•UV curable process

•Room temperature

•Low pressure

•UV polymer is applied by droping

M. Colburn, A. Grot, G. Wilson’s et al SPIE 2000

April. 1, 2005 13

UV-curable NIL with Double-layer Spin-on Resist

1. Prepare substrate, spin under layer and liquid resist on

4. Mold and substrate separation

5. Residue layer and under layer etching

2. Alignment

UV

6. Metal evaporation and lift-off

3. Press and exposure

W. Wu, H. Ge, S.Y. Chou et al., EIPBN 2004

April. 1, 2005 14

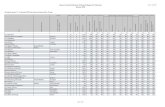

NIL is on ITRS (international technology roadmap for semiconductors)

* ITRS 2003 update

April. 1, 2005 15

Major Players

Princeton University ---- Nanonex, NanoOpto

University of Taxes at Austin ---- Molecular Imprints

University of Michigan

Hewlett-Packard

Motorola

Micro resist…

Europe:

Aachen University. Lund University…

Obducat, EVG, SUSS…

Japan:

Hitachi…

April. 1, 2005 16

Nano-circuit Crossbar Architecture

Electrodes

Molecule

Y. Chen, G.Y. Jung et al., Nanotech. 14, 462 (2003)

April. 1, 2005 17

1A-H

100

80

60

40

R (1

09oh

m)

20

10

0.8

0.6

0.4

0.2

0

2A-H 3A-H 4A-H 5A-H 6A-H 7A-H 8A-H

H P i n v e n t

Y. Chen, G.Y. Jung et al., Nanotech. 14, 462 (2003)

64 bits Cross-bar Memory at 60 nm Half-pitch by Thermal Nanoimprint Lithography

•First working circuit fabricated using NIL

•First working Molecular memory circuit

April. 1, 2005 18

Schematic of Single Electron Memory

Injection Store

e2/C dot

Coulombblockade

Channel

GateFloating gate

Buried OxideSubstrate

Poly Si Control Gate

Source

Drain

Floating Dot

dotCeE

2

=∆ kTE >>∆

• Higher operation temperature requires larger energy gap, implying smaller dot size.

• Sub-10 nm dot size is required for room temperature operation.

W. Wu, J. Gu, H. X. Ge, et al., Applied Physics Letters 83, 2268 (2003).

April. 1, 2005 19

Room Temperature Si Single Electron Memory Fabricated by NIL

30nm

-0.2 -0.1 0.0 0.1 0.21E-12

1E-11

1E-10

1E-9

∆Vth

=22 mV

tox

=13.6 nm thermal +

33.1 nm PECVD

Vds

=50 mV

Original 7 V, 1 µs

9 V, 1 µs

I ds (A

)

Vg (V)

Id vs. VgImprinted channelBefore oxidation

W. Wu, J. Gu, H. X. Ge, et al., Applied Physics Letters 83, 2268 (2003).

April. 1, 2005 20

0 2 4 6 8 10

-0.05

-0.04

-0.03

-0.02

-0.01

0.00

0.01

*same result for 1 ms pulsePulse duration 1 µs

V t (V)

Control Gate Voltage (V)

Single Electron Memory at Room Temperature Threshold vs. Pulse Voltage

W. Wu, J. Gu, H. X. Ge, et al., Applied Physics Letters 83, 2268 (2003).

April. 1, 2005 21

Threshold Shift Independent of Charging Time

10-8 10-7 10-6 10-5 10-4 10-3 10-20

10

20

30

40

Vctrl

= 7 V

Thre

shol

d sh

ift (V

)

Pulse width (Sec)

W. Wu, J. Gu, H. X. Ge, et al., Applied Physics Letters 83, 2268 (2003).

April. 1, 2005 22

Density Limit of Continuous Thin Film Magnetic Media

1. Each grain has to be large enough to be thermally stable (superparamagnetism).

2. Transition noise of each bit

Patterned magnetic media

Answer:

April. 1, 2005

Quantized Magnetic Disk

Magnetic

Nonmagnetic

Substrate

N

N

N

N

N

S

S

S

S

S

•Several orders higher density limit than continuous thin film.

–Each bit is a single domain.

–Week coupling between each bit.

•Nano-lithography needed.

Chou, Wei, Krauss and Fischer, JAP, 76(10), 6673 (1994)

April. 1, 2005

18 Gbits/in2 Large Area Quantized Magnetic Disk

W. Wu, B. Cui, X. Sun, W. Zhang, L. Zhuang, L. Kong, and S. Chou, JVSTB, Vol 16, Iss 6, 3825 (1998)

April. 1, 2005

MFM Image of 18 Gbits/in2 Large Area Quantized Magnetic Disk (After Polishing)

Every bit is a single domain.

W. Wu, B. Cui, X. Sun, W. Zhang, L. Zhuang, L. Kong, and S. Chou, JVSTB, Vol 16, Iss 6, 3825 (1998)

April. 1, 2005

30 Gbits/in2 Co Longitudinal Quantized Magnetic Disk

25 nm

MFMSEMW. Wu, B. Cui, X. Sun, W. Zhang, L. Zhuang, L. Kong, and S. Chou, JVSTB, Vol 16, Iss 6, 3825 (1998)

April. 1, 2005 27

Future Work:

Challenges of NIL:

•Yield

−It is easier to have defects, because it is a contact lithography

•Alignment accuracy is currently 10x worse than resolution

−Alignment must be achieved without high cost

April. 1, 2005 28

Summary

• Nanoimprint lithography is:• High throughput

• High resolution

• Low cost

• Capable of making real applications

• More need to be done.

April. 1, 2005 29