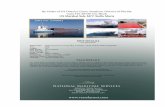

Mt k 51 Schematic

Transcript of Mt k 51 Schematic

5

4

3

2

1

D[0..7] A[0..7]

Ext.Code Memory 0x0000-0x7FFFU5D

Ext.Code& Data Memory 0x8000-0xFFFFD0 D1 D2 D3 D4 D5 D6 D7 A8 A9 A10 A11 A12 A13 A14 /RAM_CE /RAM_OE /WR A0 A1 A2 A3 A4 A5 A6 A7 U2 10 9 8 7 6 5 4 3 25 24 21 23 2 26 1 20 22 27 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 CE OE WE HM62256B D0 D1 D2 D3 D4 D5 D6 D7 11 12 13 15 16 17 18 19 D0 D1 D2 D3 D4 D5 D6 D7 D0 D1 D2 D3 D4 D5 D6 D7

8-bit output portU3 2 3 4 5 6 7 8 9 11 1 +5V 20 19 18 17 16 15 14 13 12

8-bit input portU4 2 4 6 8 11 13 15 17 1 19 18 16 14 12 9 7 5 3 D0 D1 D2 D3 D4 D5 D6 D7

D0 D1 D2 D3 D4 D5 D6 D7 ALE

2 3 4 5 6 7 8 9 11 1 +5V 20

1D 2D 3D 4D 5D 6D 7D 8D LE OE VCC 74HC573

1Q 2Q 3Q 4Q 5Q 6Q 7Q 8Q

19 18 17 16 15 14 13 12

A0 A1 A2 A3 A4 A5 A6 A7

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 /PSEN +5V

U1 10 9 8 7 6 5 4 3 25 24 21 23 2 26 27 20 22 1 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 CE OE VPP 27C256 A[8..14] O0 O1 O2 O3 O4 O5 O6 O7 11 12 13 15 16 17 18 19

1D 2D 3D 4D 5D 6D 7D 8D LE OE VCC 74HC573

1Q 2Q 3Q 4Q 5Q 6Q 7Q 8Q

DOUT0 DOUT1 DOUT2 DOUT3 DOUT4 DOUT5 DOUT6 DOUT7

DIN0 DIN1 DIN2 DIN3 DIN4 DIN5 DIN6 DIN7

1A1 1A2 1A3 1A4 2A1 2A2 2A3 2A4 1G 2G 74LS244

1Y1 1Y2 1Y3 1Y4 2Y1 2Y2 2Y3 2Y4

D

/WR /RDC

memory & i/o decoderU6 /RD /WR 2 3 4 5 6 7 8 9 1 11 12 13 14 15 16 17 18 19

D0 D1 D2 D3 D4 D5 D6 D7

J1 +5V 1 2 3 CON3 +5V + S1 RESET RST P3.2 P3.3 P3.4 P3.5 P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 A0 A1 +5V 1 J3 P0.0 P0.2 P0.4 P0.6 1 3 5 7 9 + + + + + + + + + + 2 4 6 8 10 P0.1 P0.3 P0.5 P0.7 R22 2 3 4 5 6 7 8 9 10k Populate only for NMOS MCU D0 D1 D2 D3 D4 D5 D6 D7 /INT0 12 13 14 15 1 2 3 4 5 6 7 8 10uF 10V C3 C2 11.0592MHz Q1 18 9 X2 RESET INT0 INT1 T0 T1 P1.0/T2 P1.1/T2X P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 8051 compatible MCU P2.0 P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7 RD WR PSEN ALE/P TXD RXD INTERNAL U7 EXTERNAL 31 30pF C1 19 EA/VP X1 P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 39 38 37 36 35 34 33 32 21 22 23 24 25 26 27 28 17 16 29 30 11 10 D0 D1 D2 D3 D4 D5 D6 D7 P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 A8 A9 A10 A11 A12 A13 A14 A15 P3.7 P3.6 ALE P3.1 P3.0

D0 D1 D2 D3 D4 D5 D6 D7

C

A8 A9 A10 RS232 RS485 A15 /PSEN

I I I I I I I I I/CLK I/OE

I/O/Q I/O/Q I/O/Q I/O/Q I/O/Q I/O/Q I/O/Q I/O/Q

8255

/RAM_CE /RAM_OE LCD_E GPIO3 GPIO1 GPIO2

RxD

30pF

R1 10K

RST

P2.0 P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7

16x2 text LCD interfaceJR1 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 R19 D7 D6 D5 D4 D3 D2 D1 D0 R/W RS LCD_E A1 A0 +5V 100

GAL16V8B (8051sbc.JED)

B

TxD

RxD

memory mapped I/O using external data memory 0x0000 0x0001 lcd command write lcd data write lcd command read lcd data read GPIO1/OUTPUT PORT GPIO2/INPUT PORT GPIO3/OUTPUT PORT 8255 PORTA 8255 PORTB 8255 PORTC 8255 PORT CONTROL2

B

A0 A1

J2 P3.0 P3.2 P3.4 P3.6 1 3 5 7 9 + + + + + + + + + + 2 4 6 8 10 P3.1 P3.3 P3.5 P3.7 1 2

0x0002 0x0003 0x0100 0x0200

CONN RECT 16

+5V

3 R2 10K

+5V

+5V

C

CON10AP

CON10AP

+5V

VCC VCCA

S2A

0x0400P3.2 P3.3 JP1 1 2 Single Step

J4 P2.0 P2.2 P2.4 P2.6 1 3 5 7 9 + + + + + + + + + + 2 4 6 8 10 P2.1 P2.3 P2.5 P2.7 INT0

Designed by Wichit Sirichote, [email protected]

0x0300 0x0301 0x0302 0x0303

+5V

Title

MTK51 8051 MICROCONTROLLER TRAINER KITSize B Date: Document Number Sunday, July 26, 2009 Sheet1

CON10AP

Rev 2 1 of 3

5

4

3

5

4

3

2

1

D2 POWER +5V TP1D

R3

2k +5V

+12V J5 1 1N4007 1

U8 LM7805/TO 3 C7 10uF 16V C8 0.1uF C9 0.1uF C10 0.1uF C11 0.1uF + C4 C12 0.1uF VOUT GND VIN 1 + C13 0.1uF C5 1000uF 16V

D3 +12V 2

DC input

R4 330D

+5V

1 C6 0.1uF

D4 Debug LED

TP2 GND 1

2

DC2 0.1uF P1.7

2

+5V +5V 10uF 10V C14 U10C

VCC VCC 10uF C15 + +5V

+5V

2-channel 12-bit ADCU9 R5 4.7k

R6 4.7k U11

P1.1

6 5

DOUT DIN CLK CS/SHDN VCC LTC1298 C18 0.1uF CH0 CH1 2 3

R7 100

VB1 + 5 9 4 8 3 7 2 6 1 C16 10uF

SUB-D 9, Male (cross cable) R9 680 +5V R10 120

J7B

1 2 3 CON3

A

5

+

J6 1 2 3

2 6

V+ V-

C+ C1C2+ C2T1IN T2IN R1OUT R2OUT

1 3 4 5 11 10 12 9

P1.2 10uF + C17 P1.0 P1.0 6 7 1 2 3 S0 S1 S2 SCL PP 24C256 32kB eeprom +5V R21 SDA 5 P3.4 P3.4

7 1

max clock 200kHzP1.3 8

C

R8 100 C19 0.1uF

CON3

14 7 13 8

T1OUT T2OUT R1IN R2IN MAX232A

TxD

10

+ 4.7uF 16V C20

C21 0.1uF

R11 680 U12 6 7 1 A B R D DE RE 75176 4 3 2 +5V R12 4.7k +5V RS232 RS485 P1.3 J8 P1.0 P1.2 P1.4 P1.6 1 3 5 7 9 + + + + + + + + + + 2 4 6 8 10 P1.1 P1.3 P1.5 P1.7

B

CON10AP

Real-time clock32768Hz Y1 1 2 6 3 8 U13 X1 X2 SCLK VBAT VCC DS1307 +3V LithiumA

SDA SQW/OUT

5 7

P3.4

P1.0 SW1 1 2 3 4 SW DIP-4 8 7 6 5 DIN0 DIN1 DIN2 DIN3

DIN0 DIN1 DIN2 DIN3

BT1 2 1 +5V

Designed by Wichit Sirichote, [email protected] settingsTitle

MTK51 8051 MICROCONTROLLER TRAINER KITSize B Date:4 3 2

Document Number Sunday, July 26, 2009 Sheet1

Rev 2 2 of 3

5

4

3

2

1

DOUT0 DOUT1 DOUT2 DOUT3 DOUT4 DOUT5 DOUT6 D0 D1 D2 D3 D4 D5 D6 D7 2 3 4 5 6 7 8 9 11 1 DIN5 S17 S18 S19 S20 S21 S22 S23 +5V 20

U14 1D 2D 3D 4D 5D 6D 7D 8D LE OE VCC D5 74HC573 LED D6 LED D7 LED D8 LED D9 LED D10 LED D11 LED D12 1Q 2Q 3Q 4Q 5Q 6Q 7Q 8Q 19 18 17 16 15 14 13 12

D

S3

S4

S5

S6

S7

S8

RESET KEY

D

DIN4

RELAY

S10

S11

S12

S13

S14

S15

S16

DIN6

S24

S25

S26

S27

S28

S29

S30

3mm LED x8D15 1N5236A DIN7 GPIO3C

+5V R13 DIN0 DIN1 DIN2 DIN3 DIN4 DIN5 DIN6 DIN7 2 3 4 5 6 7 8 9 4.7K LS1 J10 R20 SPEAKER +5V 1 2 3 CON3 10 5 3 4 1 2 RELAY SPDT PA0 PA2 PA4 PA6 J11 1 3 5 7 9 + + + + + + + + + + 2 4 6 8 10 1N4148 PA1 PA3 PA5 PA7 1 R17 2 4.7k 3 1 3 5 7 9 11 13 15 + + + + + + + + + + + + + + + + J12 +5V +5V +5V U16 2 4 6 8 10 PC1 PC3 PC5 PC7 3 VDD R18 4.7k DQ GND DS1820 2 VCC VCC 2 4 6 8 10 12 14 16 RELAY_USE RELAY_OFF DS1820_USE DS1820_OFF PS2_DATA PS2_OFF PS2_CLK PS2_OFF RELAY P3.4 P1.4 P1.7 Q3 BC337 D14 M-DIN_6-P K1 1 R14 DOUT7 4.7k 3 C R15 4.7k DATA 1 2 3 JP2 R16 6 5 4 CLK + C22 22uF 4.7k +5V SPI PORT 2 +5V Q2 BC327 +12V +5V +5V P1.5 P1.6 P1.7 1 MOSI MISO SCK J9 1 2 3 4 5 CON5

C

B

U15 D0 D1 D2 D3 D4 D5 D6 D7 /RD /WR A0 A1 RST 34 33 32 31 30 29 28 27 5 36 9 8 35 6 D0 D1 D2 D3 D4 D5 D6 D7 RD WR A0 A1 RESET CS PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7 8255 4 3 2 1 40 39 38 37 18 19 20 21 22 23 24 25 14 15 16 17 13 12 11 10

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

B

+5V

CON10AP PB0 PB2 PB4 PB6 J13 1 3 5 7 9 + + + + + + + + + + 2 4 6 8 10 PB1 PB3 PB5 PB7

+5V

CON10AP PC0 PC2 PC4 PC6 J14 1 3 5 7 9 + + + + + + + + + +

8255A

+5V

1

A

Designed by Wichit Sirichote, [email protected]

CON10AP

Title

MTK51 8051 MICROCONTROLLER TRAINER KITSize B Date:5 4 3 2

Document Number Sunday, July 26, 2009 Sheet1

Rev 2 3 of 3