MP Notes - Question Bank

-

Upload

saileshmurali -

Category

Documents

-

view

221 -

download

0

Transcript of MP Notes - Question Bank

-

8/3/2019 MP Notes - Question Bank

1/8

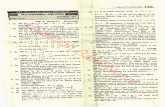

Micro ProcessorsUnit no S No Description SRM

Unit 1

1 8085 Architecture Jun-11 Nov-10

2What are the ways in memory are classified. Define the

spec of a typical memoryJun-11

3a Write notes on Decoder and Tristate Logic Nov-10

3b Exp addressing modes of 8085 with examples. Nov-10 Nov-11

3cBriefly explain about the classification and interfacing of

8085 MPNov-10

4

Write shor notes on: RAM Memory interfacing and

interrupt structure of 8085. May-106a Write short notes on vectored interrupts in 8085. May-10

6bDraw the micro processor bus timing for the instruction

STA 4500h and explain.May-10

7Different data transfer schemes in 8085 with necessary

diagramsNov-11

7b Draw the timing diagram for MVI A,02 Nov-11

Unit 2

1 Descending order program Jun-11

2 Timig diagram for memory write, I/O Read cycle Jun-11 Nov-10

2.b How to write, assemble and execute a simple program Jun-11

3 Briefly explain about stck and subroutine in 8085 Nov-10

4 Write the algorithms, flow chart and assembly languageprogram to find the average mark of 10 students using

8085.

Nov-10

5a Write a program for adding a set of nos. May-10

5bWrite a program to find the max no from the given set of

nos.May-10

6 Exp instruction set of 8085 with examples May-10

7 Program to multiply two 16 bit nos Nov-11

Unit 3

1 Various conditions for data transfer Jun-11 Nov-10

2Draw and explaint he conditions of 8237 A-DMA

controlling with 8085Jun-11

3 Operating modes of 8255 Programmable interfaes Nov-10 May-10

4What is meant by DMA transfer method and explain the

8257 programmable DMA controllerMay-10

5 What is known as PPI? What is the use of interfacingthe same in 8085?

Nov-11

6a Exp how PPI devices are interfaced with 8085? Nov-11

6b What are the uses of SID and SOD lines? Nov-11

Unit 4

1Draw the block diagram of 8279 prog keyboard and

display interfacing and explain each section.Jun-11

2Draw the schematic diagram of programmable interrupt

controller and define the functions of each pinJun-11 Nov-10

3 Draw architecture of 8259 and exp each function Nov-10

4 What are interrupts? Exp the interrupts in 8085 May-10

4bDraw and explain the timing diagram of any one of the 3

byte instruction.May-10

5 Exp the different modes of operation of 8253 timer/counter May-10

6 Exp architecture of 8259 PIC Nov-11

7 Exp different modes of operation of 8253 timer Nov-11

Unit 5

1List and explain various types of addressing modes in

8051. Give two examples for each.Jun-11

1b Write notes on: CALL, JUMP, PUSH and POP Jun-11

2 Architecture of 8031 and explain. Jun-11 Nov-11

-

8/3/2019 MP Notes - Question Bank

2/8

3Write a prog to clear Acc, complement the accumulator

and store the results in registers in 8051.Nov-10

3bHow many interrupts are there in 8051? List and briefly

exp each of them.Nov-10

4List the various types of instrcution sets in 8051. Explain

each with two examples.Nov-10

5Explain the LCD display interfacing with micro controller

8051.May-10

6 Explain keyboard interfacing with 8051 May-10

-

8/3/2019 MP Notes - Question Bank

3/8

S No Parameter

Nov-10 1.1Diff the functions of Program counter

and stack pointer in 8085

1.2 Define - Bidirectional bus. Why is thedata bus bidirectional?

May-2010 1.3What are the addressing modes of

8085?

1.4How do the address and data lines get

demultiplexed in microprcessor?

June-2011 1.5Distinguish Van Neumann and Harvard

architecture. Give an example for each.

1.6 Adv of micro controller

Diff bet Micro Pro and Micro Cont

2.1 What is the need for timing diagram?

Nov-10 &

Jun-112.2 How long can the INTR pulse stay high?

2.3Define the machine control instructions

of 8085 micro processor.

2.4 What is the significance of XCHG andSPHL instructions?

2.5 Use of assemblers

Nov-10 &

Jun-112.6 How long can the INTR pulse stay high?

3.1Briefly explain about DMA transfer

scheme.

3.2List the various methods of I/O

interfacing.

3.3What are the ports available in 8255?

What is the advantage of the third part?

3.4What is meant by interrupt mask

register in 8259?

3.5 Define DMA transfer scheme

-

8/3/2019 MP Notes - Question Bank

4/8

3.6List out various methods of I/O

interfacing.

4.1Distinguish hardware and software

polling.

4.2Write the control word format for

programmable interval timer.

4.3 List the functions performed by 8279.

4.4 What is the use of USART?

4.5 Interrrupts in 80854.6

What are the tasks involved in keyboard

interface?

5.1 What are the salient features of 8051?

5.2How is the selection of a particular

register bank is done in 8051?

5.3Name any four bit manipulation

instruction in micro controller 8251.

5.4 What is meant by SFR in 8051? Give anexample.

5.5 Give the hardware descriptions of 8071.

5.6List the various types of instruction sets

in 8051

Nov-11

1What are the important control signals in

8085 Micro processor?

2What are the different data transfer

schemes?

3 Write the different between Op code andoperand

4Write the stack related instructions in

8085 micro processor.

5

What is the maximum number of I/o

devices that can be connected to 8085

Micro processor using 8259 IC's?

-

8/3/2019 MP Notes - Question Bank

5/8

6What is the bit set reset mode of 8255

PPI?

7Name the interrupts available in Micro

controller

8 Write the memory capacity of 8051

9 What are the hardware interrupts?

10What are th different interrupt signals in8086? Among these, which one has the

highest priority?

8155/56 Prog I/O port and Timer

8251A

USART - Universal Asynchronous/

synchronous Receiver/ transmitter

8253 Programmable Interval Timers

8254 Programmable Interval Timers

8255 Prog peripheral interface

8259 Programmable interrupt controller

8279 KB interface

8355 ROM and I/o port chip

-

8/3/2019 MP Notes - Question Bank

6/8

Micro ProcessorsDecription

Prog counter holds the address of the first byte of next execution or the remaining

part of the address byte in a long address. Stack pointer holds the address of the

top of the stack.

Bidriectional bus is a group of conducting lines in which the current flos in both the

directions. In 8085, the data bus carries the data bus and also the lower byte of theaddress bus. This is because the addresses are of 16 bit.

Immeiate, Direct, Register direct, Register Indirect & Implied,

By using IC 74373

Harward Architecture - separate pathways for instruction and data, in Van

Neumann, it can be combined.

It has less no of compoenents, easy to use and program, easy to modify, specific

to an application.

Micro proc has more op-codes, few bit handling instructions, micro controller hasless op codes and more bit handling instructions. Micro controoler is a single chip

consisting of Micro processor, Memory, I/O lines etc.

Timing diagram provides the information regarding the status of various signals,

when machine cycle is executed. The knowledege of timing diagram is useful for

selecting peripheral devices like memories, latches, ports, etc.

INTR can be high till the interrupt is accepted or acknowledged.

Opcode fetch, Memory Read, Memory write, I/O read, I/O write, Bus Idle, Interrupt

acknowledge.

In these instructions, the 16 bit address are directly handled. XCHG - transfers the

content of HL pair to DE pair. SPHL copies the the address in HL pair to stack

pointer.

Assemblers convert the assembly level programs to machine language programs.

Compilers or interpreters convert the high level program to machine level

programs.

INTR can be high till the interrupt is accepted or acknowledged.

For Direct Data transfer between memory and I/O devisec, a separate H/w

contrller called DMA is used. DMA controller temporarily borrows address, data

and control buses from the processor and transfers the data bytes directly from the

I/O ports to memory locations or Vice versa.

Memory mapping and standard mapping.

Ports A,B and C. In C, individual pins can be set or reset.

Ref 3.1

-

8/3/2019 MP Notes - Question Bank

7/8

Ref 3.2

Polling is the process of selecting a particular interrupt, when the processor gets

signals from more than one simultaneously. In s/w polling, the entire polling is

governed by program. In h/w, the hardware takes care of the checking of status of

interrupting devices and allowing one by one to the processor.

KB Scanning, KB Debouncing, Key code generation, Informing the key entry to

CPU, Storing display codes, Output Display codes to LEDs, Display refreshing

A device which can be programmed to perform Synchronous or Asynchronous

serial communicateion is called USART. It is used for converting parallel data to

serial or vice cersa. 8251A can be used to interface MODEM and establish serail

communication through MODEM over telephone lines.

S/w and H/wRef 4.3

4096 bytes On chip memory, 4 register banks and 4 I/o ports, High speed

programmable serial port, two multiple mode 16 bit timer/ counter, 12M Hz clock,

Direct byte and bit addressability, Bianry or decimal arithmetic, compatible with

existing 8084 software.

Register selection is done by the bits RS0 and RS1 in the program word. 00-07 -

Bank 0, 08-0F - Bank 1, 10 - 17 - Bank 2, 18 - 1F - Bank 3

Special Function Register. This is speciality of 8051. All access to the 4 I/o ports,

CPU registers, interrupt control registers, timer/ counter etc are performed thorughregisters between 80h and FFh

8051 H/w descriptions - Consists of a CPU, two memory sections ( Data Memory -

RAM and Programmable memory - PROM/ EPROM), I/o ports/ SFR, and control

logic for peripheral devices.

Data transfer, Logical, Arithmetic, Jump and CALL,

-

8/3/2019 MP Notes - Question Bank

8/8