Module 3 Combinational and Sequential Logic Circuit

description

Transcript of Module 3 Combinational and Sequential Logic Circuit

Module 3Combinational and Sequential

Logic Circuit

By: Cesar Mendoza

Combinational logic:

• Combinational logic: When logic gates (such as AND, OR and NOT) are connected together to produce a specified output for certain specified combinations of input variables, with no storage involved

• “is that logic in which all outputs are directly related to the current combination of values on its inputs”.

The Exclusive-OR and Exclusive-NOR gates

• Exclusive-OR (XOR)

OR

A

B

X

NOT

NOT

Y1

Y2AND-2

AND-1

XA

BXOR

XOR Logical Operation and Truth Table

• The logical operation of XOR is such that the output is high only when the two inputs are at opposite levels

INPUTS OUTPUTA B X0 0 00 1 11 0 11 1 0

XOR Logical Function• The two variables expression “X = A B” is

called the Logical XOR Function

OR

A

B

X

NOT

NOT

Y1

Y2AND-2

AND-1

The Exclusive-NOR (XNOR)

OR

A

B

AND

AND

NOT

NOT

NOT X

Y1

Y2

Z

XA

BXNOR

XNOR Logical Operation and Truth Table

• The logical operation of XNOR is such that when the two inputs are opposite the output is LOW.

INPUTS OUTPUTA B X0 0 10 1 01 0 01 1 1

XNOR Logical Function• The expression is called the Logical

XNOR Function

• Then the output of XNOR can be written as and it means:

• If A and B both are High or both Low, then X is High. Otherwise X is Low

XA

BXNOR

XNOR Logical Function

• Then the output of XNOR can be written as

• and it means:• If A and B both are High or both Low, then X is High.

Otherwise X is Low

QUESTION #1

1. What is combinational logic Circuit?

2. Draw the combinational circuit for XOR gate.

3. What is the logical operation of XOR gate

4. Construct and complete 2 input Truth Table for XOR gate.

QUESTION #2

1. What is combinational logic Circuit?

2. Draw the combinational circuit for XNOR gate.

3. What is the logical operation of XNOR gate

4. Construct and complete 2 input Truth Table for XNOR gate.

Example of Combinational Logic

• Central Heating Pump

S1

S2

0VDC

ON OFF

ON OFF

+5VDC

Q

NOT

AND

Truth Table for Central Heating Pump

Switches Output

Heating Switch

Temp Sensor Pump

off off (Hot) offoff on (Cold) offon off (hot) onon on (cold) off

Example of Combinational Logic

• Multiplexer

A

S

B

ANDG1

ANDG2

ON OFF

ON OFF

OFFON

0VDC

OR

+5VDC

NOT NOT Q

Truth Table for Multiplexer

Inputs Switches OutputS A B Q (LED)

OFF OFF OFF offOFF OFF ON onOFF ON OFF offOFF ON ON onON OFF OFF offON OFF ON offON ON OFF onON ON ON on

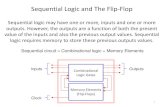

Sequential Logic

• A digital logic function made of basic logic gates (AND, OR, NOT, etc.) in which the output values depend not only on the values currently being presented to its inputs, but also on previous input values.

• “is that logic in which the output depends on a sequence of its input values”.

Latches and Flip-Flops

1) LatchesIt is a bistable element that can have its output latched HIGH (Set) or LOW (Reset), hence the name S-R Latch.

1) Flip-FlopsIt is a synchronous bistable device that can have its output changes state only on the clock edge.

Main difference between Latches and Flip-Flops Latch: It is active when clock either at logic high

level or at low level. Flip-Flop: It is active only on the clock edges.

Example of Latches Example of Flip-Flops 1) SR Latch2) Clocked SR Latch3) D Latch

1) JK flip-flops2) T-type flip-flops3) Edge triggered D-FF

The NOR Gate S-R Latch

• Cross coupled NOR Gate

NORG1

NORG2

R

S

Q

QR

S

Q

Q

S-R Latch logic CircuitLatch logic symbol

• initially assume that both inputs R and S and output Q are LOW

• [i.e. R = S = 0 and Q = 0]

NORG1

NORG2

R

S

Q

Q

0

0

0

10

1

R S Q /Q0 0 0 1

• Now G2 inputs are G = 0 and S = 0, therefore G2 output is = 1.

• G1 inputs are Q = 1 and R = 0, therefore G1 output is Q = 0.

NORG1

NORG2

R

S

Q

Q

0

0

0

10

1

R S Q /Q0 0 0 1

NORG1

NORG2

R

S

Q

Q

0

0->1

0->1

1-> 0

0

Change S to HIGH G2 inputs become Q = 0 and S = 1, therefore G2 output is = 0.Now G1 inputs will change to = 0 and R = 0, therefore G1 output will change to Q = 1 the latch is in the Set state.

1 0

1

10

1

R S Q /Q0 1 1 0

NORG1

NORG2

R

S

Q

Q

0

1->0

0->1

1-> 0

0

Change S to HIGH G2 inputs become Q = 0 and S = 1, therefore G2 output is = 0.Now G1 inputs will change to = 0 and R = 0, therefore G1 output will change to Q = 1 the latch is in the Set state.

1 0

1

1

R S Q /Q0 1 1 0

0 0 1 0

NC

0

NORG1

NORG2

R

S

Q

Q

0->1

0

1->0

0->1

01

Change S to HIGH G2 inputs become Q = 0 and S = 1, therefore G2 output is = 0.Now G1 inputs will change to = 0 and R = 0, therefore G1 output will change to Q = 1 the latch is in the Set state.

01

10

10

R S Q /Q0 1 1 0

0 0 1 0

1 0 0 1

0

1

Inputs Outputs OperationR S Q0 0 Q No Change (same as

previous)0 1 1 0 The output Set to ON1 0 0 1 The output Reset to OFF

1 1 Invalid condition unpredictable output state

Table 6 Truth table for S-R Latch

Q

Q

Terminology usedTerms MeaningsNo change

Latch remains in previous state (store the previous output.

Latch Set The output (Q) Set to ON (i.e. Q = 1).Latch Reset The output (Q) Reset to OFF (i.e. Q = 0).

Invalid Condition

Simultaneous High’s on both inputs (i.e. R = S =1) not allowed. It generates unpredictable output state.

QUESTION #3

1. What is sequential logic circuit?

2. What is the difference between latch and flip flop?

3. Complete the Truth Table for RS Latch

4. What does “No Change Means”?

5. What is “invalid Condition Means”?

Flashback Lesson• Distinctive Shape – Rectangular Shape Symbol

Level Triggered Latches• To have control over the Latch’s operation, a clock signal is

applied to decide when a latch is enabled or disabled and when the output changes its state. The clock signal ensures that the device is triggered into operation at the right time and is denoted with C Clock Signal or EN Enable Signal

• Level Triggered latch can be defined as “a logic device that changes its output state in response to a HIGH or LOW level of the clock”;

Level triggered SR Latch

R

CK

S

Q

Q

AND

AND

NOR

NOR

AND Inputs Latch Outputs Comments

CK R S Inputs Q

0 0 0 0 0

NO Change

As long as the clock level CK is LOW the output remain same as previous (No Change will occur).

0 0 1 0 0

0 1 0 0 0

0 1 1 0 0

1 0 0 0 0 Q No Change (same as previous)

1 0 1 0 1 1 The output Set to ON

1 1 0 1 0 0 The output Reset to OFF

1 1 1 1 1 Invalid unpredictable output state

Table 7 Truth table for Level Triggered SR Latch

Level Triggered D-type Latch• The D-type latch is basically a S-R latch with small circuit modification.

This modification was introduced to ensure that the S and R inputs are never HIGH or LOW at the same time. So D-latch is used to eliminate the undesirable invalid state occurs in the S-R latch.

• “The D-type latch is a Data-type circuit that can latch (store) a binary 1 or 0”.

Level Triggered D-type Latch

AND Inputs

Latch Inputs Outputs Comments

CK D R S Q

0 0 0 0NO

Change

As long as the CK is LOW, the output remains same as previous.

0 1 0 0

1 0 1 0 0 The output Reset to OFF

1 1 0 1 1 The output Set to ONTable 8 Truth table for Level Triggered D Latch

CK

D

Q

Q

C

NOR

NOR

Q

Q

RAND

AND

NOT D

CK S

Question #4

• What is “level triggered latch” means?

• Draw the symbol of level triggered SR latch.

• Draw the level triggered SR latch circuit.

• Complete the truth table for level triggered SR latch.

Flashback--- Question #1:

• Draw the distinctive symbol and the equivalent rectangular symbol of the following basic gates:

1. AND2. OR3. NOT4. NAND5. NOR

Review Exercise:1. “is that logic in which all outputs are directly related to the current combination of values

on its inputs”.a) Combinational Logicb) Sequential Logicc) Common Logic

2. The logical operation of XOR is such that the output is high only when the two inputs are at opposite levels

a) OR Gateb) XNOR Gatec) XOR Gate

3. “is that logic in which the output depends on a sequence of its input values”.a) Combinational Logicb) Sequential Logicc) Common Logic

Review Exercise:4. It is a synchronous bistable device that can have its output changes state only on the clock edge.

a) Flip Flopb) Latchc) Level Trigger

5. Latch remains in previous state (store the previous output.a) Latchb) No Changec) Reset

6. It is a bistable element that can have its output latched HIGH (Set) or LOW (Reset), hence the name S-R Latch.

a) Flip Flopb) Latchc) Level Trigger