MIT LL Superconductor Electronics Fabrication Process for ......• SFQ Process Overview – SFQ...

Transcript of MIT LL Superconductor Electronics Fabrication Process for ......• SFQ Process Overview – SFQ...

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

MIT LL Superconductor Electronics Fabrication Process for VLSI Circuits With 4, 8, and 10

Niobium Layers

Applied Superconductivity Conference, ASC 2014 August 10-15, Charlotte, NC

Sergey K. Tolpygo, Vladimir Bolkhovsky, Terry Weir, William D. Oliver, Leonard M. Johnson, and Mark A. Gouker

Quantum Information and Nanosystems Technology Group Lincoln Laboratory, Massachusetts Institute of Technology, Lexington, MA 02420

This work was sponsored by the IARPA under Air Force Contract FA872105C0002. Opinions, interpretations, conclusions, and recommendations are those of the authors, and not

necessarily endorsed by the United States Government.

1EOr2A-01-2 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• SFQ Process Overview – SFQ fabrication process nodes – General process description (4M, 8M, and 10M) – Multi-chip module process

• SFQ fabrication process highlights – Process Control Monitors and test examples – Junction properties and sizing, inductors, vias – SFQ5ee and beyond: shrinking feature size to 180 nm, stud vias

– See also our poster presentations 2EPo1A-02 and 2EPo1A-03 on

Tuesday morning for more info on JJs, inductances, etc.

Outline

1EOr2A-01-3 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

MIT LL Fully Planarized SFQ Process

• Nb/Al-AlOx/Nb JJ technology • 10 kA/cm2 (100 µA/µm2) baseline • 200-mm Si wafers • 4-, 8- &10-Nb layer nodes • Min feature sizes 350 nm • Full planarization for uniformity • Transition to stacked/stud vias

Process Features • RQL circuits with > 7.2·104 JJs per chip have been successfully demonstrated in the 8-layer SFQ4ee process node, see Micah Stoutimore, et al. presentation 4EOr3A-06 on Thursday

• New-SFQ circuits with > 2.1∙104 JJs have been successfully demonstrated in the 4-layer SFQ3ee process node, see Vasili Semenov, et al. presentation 4EOr3A on Thursday

• ERSFQ 8-bit adders, see Alex Kirichenko et al. presentation 2EOrC-04 on Tuesday

SFQ4ee (8-Nb-layer) Junction Layers

Wiring Layers

1EOr2A-01-4 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Classification – Total: 6,400 m2 (Class-10: 740 m2; Class-100: 910 m2)

• Production-class 90-nm CMOS, 200-mm tool set – Cluster metallization (sputter & MBE), etch, CMP, … – Advanced lithography: i-Line, 248-nm, 193-nm, e-beam – Full SPC, electronic traveler, technicians – ~ 10,000 wafer starts per year

• Cryogenic electronics fabrication – SFQ with deep submicron JJs and wiring features – Superconducting MCM – Superconducting qubits and ion traps

• SFQ program 200-mm tool set – Dedicated metal deposition tools – Dedicated etch and dielectric deposition tools – Shared lithography, CMP, and defect inspection tools – 248-nm and 193-nm photolithography tools

Lincoln Microelectronics Laboratory Microelectronics Laboratory

1EOr2A-01-5 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

Room-Temperature and 4 K

Process-Yield Testing • Room-temperature wafer-scale testing

– Three semi-automatic probe stations – Automation software

• Cryogenic testing – 14-chip LHe immersion probe – Switch matrix and test equipment

19 20 21 22 23 24 25 260

20

40

60

80

100

120

Num

ber o

f Jos

ephs

on ju

nctio

ns

Critical current (µA)

1000 JJs of 0.7 µm Gaussian fit

Model GaussAmp

Equation y=y0+A*exp(-0.5*((x-xc)/w)^2)Reduced Chi- 14.10988

Adj. R-Squar 0.99131Value Standard Er

# of JJs y0 0 0# of JJs xc 22.5027 0.01297# of JJs w 0.68932 0.01297# of JJs A 114.227 1.86133# of JJs FWHM 1.62323 0.03054# of JJs Area 197.370 3.21616

1σ = 3.1%

Mo room-temperature sheet resistance 4 K Ic spread data 1σ = 2.1%

1EOr2A-01-6 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• MIT Lincoln Laboratory support for IARPA Cryogenic Computing Complexity C3 program – Superconducting integrated circuit fabrication (RQL, SFQ, ERSFQ, eSFQ, etc.)

• Digital logic and memory applications (no magnetic material) – Superconducting MCM fabrication and indium-bump die attachment – Process testing & monitoring

• Snapshot – Fully planar process, 100 µA/um2 (10 kA/cm2), 500 nm JJ

• Years 1 - 2: 4 Nb metal layers • Years 1 - 2: 8 Nb metal layers • Years 2 - 5: 10 Nb metal layers

– C3 program participants design into these processes • 6 tape-outs per year • Average 3-month cycle time depending on process

– Work with design teams to maximize utility and output of GFF to meet C3 program goals

Government Furnished Foundry for C3 Program

1EOr2A-01-7 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

MIT-LL SFQ Process Nodes Fabrication Process Attribute Process Node

SFQ3ee SFQ4ee SFQ5ee SFQ6ee SFQ7ee

Critical Current Density (µA/µm2) 100 100 100 100 100

JJ diameter (surround) (nm) 700 (500) 700 (500) 700 (300) 500 (200) 500 (200)

Number of superconducting layers 4 8 10 10 10

Line width (space) (nm) 500 (1000) 500 (700) 350 (500) 250 (300) 180 (220)

Metal thickness (nm) 200 200 200 200 150

Dielectric thickness (nm) 200 200 200 200 180

Resistor width (space) (nm) 1000 (2000) 1000 (1000) 700 (700) 500 (500) 350 (350)

Resistor value (ohms per square) 2 2 2 and 0.002 2 and 0.002 2 and 0.002

Via diameter (surround) (nm) 700 (500) 700 (500) 500 (350) 350 (250) 350 (200)

Via type Etched, Stacked

Staggered

Etched, Stacked

Staggered

Stud, Stacked

Stud, Stacked

Stud, Stacked

Process Development Complete Advanced Underway Underway Underway

Early Access Availability 2013 Now 2015 2016 2017

Primary Process Now Sep. 2014 2016 2017 2018

1EOr2A-01-8 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

4-Layer Process Node: SFQ3ee Cross Section

• 4 Nb layers • 700 nm Josephson junctions • Wiring: 500 nm width, 700 nm spacing

Si substrate

Chip-edge to circuit-edge spacing

Thermal Ox SiO2

SiO2

SiO2

NbO /SiOx 2

SiO2

M5 - Bot Electrode

M6 - JJ InterconnectM7 - Interconnect

M4 - Gnd Plane

Over glass

I5 - via

I4 - via

I6 - via

J5 - JJR5 - resistor C5 - contact

M8 - Underbump 220nm

200nm 200nm

200nm

200nm

130nm 270nm

500nm

200nm

200nm Ti/Pt/Au

NbNb

NbNb

LayerLayer

ThicknessThickness

MaterialMaterial

Pad M3 M2

M1 M0

I2 Via I1 Via

Resistor Via Resistor

JJ I0 Via

1EOr2A-01-9 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

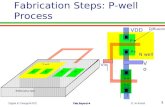

8-Nb Layers Process Node: SFQ4ee

• 8 Nb layers • 700 nm Josephson junctions • Wiring: 500 nm width, 500 nm spacing

Si substrate

Chip-edge to circuit-edge spacing

Thermal Ox SiO2

SiO2

SiO2

SiO2

NbO /SiOx 2

SiO2

SiO2

SiO2

SiO2M0 - Gnd Plane

M1 - Wiring

M3 - Wiring

M5 - Bot Electrode

M6 - JJ InterconnectM7 - Interconnect

M2 - Gnd Plane

M4 - Gnd Plane

I2 - via

Over glass

I3 - via

I5 - via

I4 - via

I6 - via

J5 - JJR5 - resistor C5 - contact

I1 - via

M8 - Underbump 220nm

200nm 200nm

200nm

200nm

130nm

200nm

270nm

500nm

200nm

200nm

200nm

200nm 200nm

200nm

200nm

200nm 200nm

Ti/Pt/Au

NbNb

Nb

Nb

Nb

Nb

Nb

Nb

LayerLayer

ThicknessThickness

MaterialMaterial

I0 - via

1EOr2A-01-10 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

8-Nb Layer Process Cross Section SEM

Si wafer

Thermal oxide

• 8 Nb layers • 700 nm Josephson junctions • Wiring Design Rules: 500 nm width, 500 nm spacing • Experimental: 350 nm width, 350 nm spacing

1EOr2A-01-11 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

SEM Images of 8-Nb Layer Process M6 M5 M4 M3

M0 M1 M2

V1 V0

V2 V3

V4 V5

V6

M6

M5

C5 J5

M7

700-nm Staggered Via Stack

1000-nm Josephson Junction

Etched 400 nm JJs

SiO2

500-nm Josephson junction TEM

1EOr2A-01-12 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

Process Pictures of Wires and Via Formation 350-nm M3 lines over planarized 350-nm M2 lines

500-nm M3 lines over planarized 500-nm M2 lines

500-nm etched contact hole

In-line CD measurements

500-nm via (with Nb) 500 nm line – 700 nm space 350 nm line – 350 nm space

1EOr2A-01-13 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

Target 10-Nb Layer Node: SFQ5ee

• 10 Nb layers • 500 nm Josephson junctions • Wiring: 180 nm width, 200 nm spacing • Stud vias • Two layers of resistors

1EOr2A-01-14 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Dielectric thicknesses chosen to facilitate impedance targets – 50-ohm for ‘clock’ line, 15-ohm for ‘data’ line

(subject to revision) • In bumps: 8-15 µm diameter on 35 µm pitch • Up to 6·104 bumps per chip in flip-chip MCMs

demonstrated • MCM size up to 5 cm by 5 cm

Process for 4-Metal-Layer Superconducting MCM

Si substrate(not high rho)

Chip-edge to circuit-edge spacing

Thermal Ox Thermal SiO2 500nm

M4 - Pad 220nm Ti/Pt/AuM5 - Bump 8 um In

A1/I1 - IMD/via 200nm Nb/SiO2

A3 - overglass 200nm SiO2M3 - Gnd 200nm NbA2/I2 - IMD/via 200nm Nb/SiO2M2 - Data 200nm Nb

M1 - Gnd 250nm Nb

M0 - Clock 150nm Nb

Layer Thickness Material

550nm Nb/SiO2A0/I0 - IMD/via

Reflowed Indium Bumps (Optical Image) 15 µm bump diameter on 35 µm pitch

1EOr2A-01-15 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• SFQ Process Overview – SFQ fabrication process nodes – General process description (4M, 8M, and 10M) – Multi-chip module process

• SFQ fabrication process highlights – Process Control Monitors and test examples – Junction properties and sizing, inductors, vias – SFQ5ee and beyond: shrinking feature size to 180 nm, stud vias

– See also our poster presentations 2EPo1A-02 and 2EPo1A-03

on Tuesday morning for more info on JJs, inductances, etc.

Outline

1EOr2A-01-16 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

Chip 12 SFQ 1A Circuit

Chip 6 JJs from 200 nm to 15 µm for Jc

Chip 7 JJ statistics 500 nm 700 nm 1000 nm 1500 nm

Chip 3 JJ Strings & Resistors

Chip 4 In-line Process Monitor

Chip 11 JJs from 200 nm to 15 µm for Jc

Chip 2 Capacitors and CBKR Via

Chip 8 Metal Lines Snake& Combs

Chip 13 Stacked 400k Via Strings JJ strings

Chip 16 JJ chains Metrology CTT Structures

Chip 1 Via Chains Staggered, Capacitors Chip 5 Via Chains Individual

Chip 9 Layer Thick

Measure SEM,

I1R Array

Chip 10 400k Via Strings staggered

Chip 12 JJ statist. 500 nm 700 nm

Chip 14 Snake & Combs CT, JJ shunted

Chip 15 JJ statistics 300 nm 350 nm 400 nm 450 nm

SFQ3ee Process Control Monitor PCM300

PCM300 includes process test structures for SFQ3ee and smaller-geometry test devices for later C3 process nodes down to 180 nm

22 mm

1EOr2A-01-17 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

0 20 40 60 80 100

250

300

400

500

600

700

800

900

10002000

Junc

tion

diam

eter

(nm

)

Yield (%)

Wafer Map

JC (µA/µm2) at PCM exposure locations

Single JJ Yield By Size and Jc Wafer Map

PCM data indicates excellent junction yield down to 450 nm drawn diameter

1EOr2A-01-18 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

Josephson Junction PCM Prescreening Room Temperature Histogram 600 nm JJs, full wafer, 1σ < 4%

4 K Single-Junction Test

700 nm Ic = 26 µA Extensive PCM testing continues at MIT-LL following

initial chip delivery to circuit design teams

• RT conductance histograms indicating IC spreads • Single JJ and JJ arrays 4 K I-V characterization • Ic of vias and wires

Key JJ testing prior to chip delivery

Room Temperature Histogram 800 nm JJs, full wafer, 1σ < 3%

1EOr2A-01-19 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Testing of series arrays of 1000 JJs at 4.2 K is an efficient method for evaluating yield of JJs and uniformity of their critical currents

• Typically from 10,000 to 40,000 JJs per chip can be tested.

4.2 K Testing of 1000-JJ Arrays

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.50

20

40

60

80

100

C

urre

nt (µ

A)

Voltage (V)

1.0 µm 0.9 µm 0.8 µm 0.7 µm 0.6 µm

1000-JJ Arrays

1EOr2A-01-20 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• From the IcRn = Const. relationship, measuring Ic of JJ arrays at 4.2 K gives similar distributions as the RT measurement of Rn distribution

JJ Uniformity (“Ic Spreads”) from 4.2 K Measurements and Correlation with RT Data

45 50 55 60 650

20

40

60

80

100

120

Num

ber o

f JJs

Critical Current (µA)

0.3 µA bin Gaussian fit

Model GaussAmp

Equation y=y0+A*exp(-0.5*((x-xc)/w)^2)

Reduced Chi-Sqr 17.32258Adj. R-Square 0.98476

Value Standard ErrorNumber of JJs y0 0 0Number of JJs xc 55.6983 0.02314Number of JJs w 1.08196 0.02314Number of JJs A 108.83705 2.01613Number of JJs FWHM 2.54783 0.0545Number of JJs Area 295.17446 5.46791

1−µm JJsMean = 55.7 µAWidth = 1.1 µA1σ = 1.9%

19 20 21 22 23 24 25 260

20

40

60

80

100

120

Num

ber o

f Jos

ephs

on ju

nctio

ns

Critical current (µA)

1000 JJs of 0.7 µm Gaussian fit

Model GaussAmp

Equation y=y0+A*exp(-0.5*((x-xc)/w)^2)Reduced Chi- 14.10988

Adj. R-Squar 0.99131Value Standard Er

# of JJs y0 0 0# of JJs xc 22.5027 0.01297# of JJs w 0.68932 0.01297# of JJs A 114.227 1.86133# of JJs FWHM 1.62323 0.03054# of JJs Area 197.370 3.21616

1σ = 3.1%

6 7 8 9 10 110

20

40

60

80

100

Num

ber o

f JJs

Critical Current (µA)

0.5-µm JJs Gaussian fit

Model GaussAmp

Equation y=y0+A*exp(-0.5*((x-xc)/w)^2)

Reduced Chi-Sqr 4.26256Adj. R-Square 0.98805

Value Standard ErrorNumber of JJs y0 0.20032 0.15962Number of JJs xc 7.76487 0.00407Number of JJs w 0.37051 0.00415Number of JJs A 103.63923 0.99315Number of JJs FWHM 0.87249 0.00978Number of JJs Area 96.25404 0.96886

1σ = 4.8%

JJ drawn diameter (µm)

Critical Current, 1σ (%) @4.2 K

Resistance, 1σ (%) @300 K

0.5 4.8* 3.8 0.7 3.1 3.0 1.0 1.9 1.8

• Ic distribution of JJ arrays from 4.2 K measurements

* Ic of small JJs become affected by thermal and EM noise

1EOr2A-01-21 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• SFQ Process Overview – SFQ fabrication process nodes – General process description (4M, 8M, and 10M) – Multi-chip module process

• SFQ fabrication process highlights – Process Control Monitors and test examples – Junction properties and sizing, inductors, vias – SFQ5ee and beyond: shrinking feature size to 180 nm, stud vias

– See also our poster presentations 2EPo1A-02 and 2EPo1A-03

on Tuesday morning for more info on JJs, inductances, etc.

Outline

1EOr2A-01-22 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Robust JJ fabrication process provides high yield and tight spreads

• IC targeting depends on precision of photolithographic patterning

SFQ Fabrication Flow Josephson Junctions

Nb/Al-AlOx/Nb trilayer deposition

Si waferNb base electrode

Al/AlOxNb top electrode

Si waferNb base electrode

Al/AlOxJJ JJ

Pattern Top Electrode to form JJ

Pattern Bottom Electrode to separate JJs

Si waferNb base electrode

Al/AlOxJJ JJ

Passivate by anodization

Si wafer

JJ JJ

500 nm Josephson Junction TEM

Nb SiO2

SiO2

Nb

Nb

1EOr2A-01-23 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Need to compensate for photolithography diffraction effects in mask layout to achieve desired JJ sizing

• SFQ3ee (&4ee) design rules provide relationship between ‘drawn’ JJ diameter dd on mask and resulting JJ diameter dw on wafer

dw = (dd2 – dc

2)1/2 + b, for design: dd = [(dw – b)2 + dc2]1/2

• Parameters dc and b are provided in the Design Rules

JJ Fabrication Near Photolithography Diffraction-Limited Resolution

Nb

Photoresist

Photomask

d

Image on PR 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0 2.20.00

0.05

0.10

0.15

0.20

0.25

0.30

0.35

0.40

0.45

D1 C3 E3 A4 D4 G4 C5 E5 D7

1/sq

rt(R

n)JJ drawn diameter (µm)

See our poster 2EPo1A-02 on Tuesday morning

1EOr2A-01-24 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

JJ Size on Wafer vs JJ Size on Photomask

dw = (dd2 – dc

2)1/2 + b The minimum printable size dc ≈ 250 nm for our 248-nm photolithography, and ~ 130 nm for our 193-nm photolithography

GN = G0(π/4)dw2 and Ic = Jc(π/4)dw

2

1EOr2A-01-25 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Dependence of JJ conductance spread (IC spread) with JJ size down to 200 nm • Characterized baseline 248 nm photolithography prior to transition to 193 nm • Full runs for JC and Ic spreads @ 100, 200 & 500 µA/µm2 to characterize trilayer process • Solid and dash lines – theory based on mask error enhancement, see our poster

2EPo1A-02 on Tuesday morning

PCM300 Junction Characterization: 10 kA/cm2 process

SEM Measurements of JJ Area JJ statistics

1EOr2A-01-26 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• JJs are externally shunted for βc ~ 1 • No hysteresis of I-V • IcRn range 700 – 900 µV • Rn: shunt resistance; RN: JJ normal-state resistance

Shunted Junction Characteristics

0.0 0.5 1.0 1.5 2.0 2.5 3.00.0

0.2

0.4

0.6

0.8

1.0

10 kA/cm2 process

R||

Externally shunted junction

Cur

rent

(mA

)

Voltage (mV)

TS#3

Ic = 158 µA; Rn = 4.45 ΩIcRn = 703 µVR|| = 3.17 ΩRN = 11.02 ΩIcRN = 1.74 mV

Rn

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.50.0

0.2

0.4

0.6

0.8

1.0

10 kA/cm2 process

R||

Rn

Externally shunted Josephson junction

Cur

rent

(mA

)Voltage (mV)

TS#5

Ic = 160 µA, Rn = 5.49 ΩIcRn = 922 µVR|| = 3.63 ΩRN = 10.80 ΩIcRN = 1.73 mV

1EOr2A-01-27 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

Layer Inductances and Inductance Uniformity in SFQ4ee (8M) Process

• Below ~ 1 µm, inductances increase as ~ w−1/2 with line width decreasing

• Simulations using different software packages generally agree within a few percent

• Simulated inductances are very close to the experimental data, within a few percent

Inductance on-Wafer Uniformity • w = 0.5 µm, 1σ = 1.5% • w = 1.0 µm, 1σ = 1.2% • w = 2.0 µm, 1σ = 0.7% • w = 4.0 µm, 1σ = 0.5%

0.1 1

0.1

1

Microstrips

Indu

ctan

ce p

er u

nit l

engt

h (p

H/µ

m)

Linewidth, w (µm)

M6_M7 M5_M4 M6_M4 M5_M7 µ0(2λ+d)/(w+b),

b = 0.7 µm

w-1/2

0.1 1

0.1

1 Striplines

Indu

ctan

ce p

er u

nit l

engt

h (p

H/µ

m)

Linewidth (µm)

M4_M6_M7 M4_M5_M7 M5_M6_M7 M4_M6_M7 (Khapaev) M4_M5_M7 (Khapaev) solid lines: InductEx

See our poster 2EPo1-03 on Tuesday morning

1EOr2A-01-28 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Design rules for SFQ3ee (&4ee) currently require staggered vias

• Stacked vias may have smaller inductance, and possibly occupy less area in circuits

• Both have been tested on a 2M-via scale, using PCM300 via test structures

Stacked Vias vs Staggered Vias

Wafer M0

M1

M2

M3

Staggered I0_I1_I2 Via (from M0 to M3)

I0

I1

I2

Wafer M0

M1

M2

M3

Stacked Via I0_I1_I2 (from M0 to M3)

I0

I1

I2

M6 M5 M4 M3

M0 M1 M2 V1

V0

V2 V3

V4 V5

V6

700-nm Staggered Via Stack

1EOr2A-01-29 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Stacked vias I0_I1_I2 (from M0 to M3 layers) with 400k vias per chip were fabricated and tested at RT Excellent yield and reproducibility across the wafers were found

• Ic measurement at 4.2 K have shown that all 1.8M stacked vias are superconducting with Ic ~ 35 mA. This is an excellent result!

Testing Stacked Vias

1 10 100 1000 10000 10000010

100

1000

10000

100000

Via stack: I0=0.7 µm, I1=1.4 µm, I2=2.0 µm

A4 B2 B6 D1 D4 D7 F2 F6 G4

RT

resi

stan

ce o

f sta

cked

via

cha

in, R

(Ω)

Number of I0_I1_I2 stack vias, N

Solid line: R = Rlead + N*Rvia

Rlead = 20.0 ΩRvia = 2.15 Ω

Total number of vias tested = 1.8M(2 groups of 100,000 stacked vias on 9 sites)

1 10 100 1000 10000 10000010

100

1000

10000

100000Total number of vias tested = 1.8M(2 groups of 100,000 stacked vias on 9 sites) Solid line: R = Rlead + N*Rvia

Rlead = 20.0 ΩRvia = 2.15 Ω

Via stack: I0=0.7 µm, I1=1.2 µm, I2=1.7 µm

A4 B2 B6 D1 D4 D7 F2 F6 G4

RT

resi

stan

ce o

f sta

cked

via

cha

in, R

(Ω)

Number of I0_I1_I2 stack vias, N

1EOr2A-01-30 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• SFQ Process Overview – SFQ fabrication process nodes – General process description (4M, 8M, and 10M) – Multi-chip module process

• SFQ fabrication process highlights – Process Control Monitors and test examples – Junction properties and sizing, inductors, vias – SFQ5ee and beyond: shrinking feature size to 180 nm, stud vias

– See also our poster presentations 2EPo1A-02 and 2EPo1A-03

on Tuesday morning for more info on JJs, inductances, etc.

Outline

1EOr2A-01-31 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

Etched Nb Lines for Advanced Nodes

200 nm line / 300 nm space

180 nm line / 300 nm space

180 nm line / 300 nm space

150 nm line / 300 nm space

200 nm line / 300 nm space

250 nm lines / 250 nm space

Min pitch, p = w + s, is 420 nm for our 248-nm photolithography

1EOr2A-01-32 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Nb lines with length L ~ 1 m - 2 m and different widths, w, down to 0.15 µm were fabricated. Six test structures of the same type (width and length) per chip

• Critical currents of Nb lines were found to be close to the theoretical limit – Ginzburg-Landau depairing current for wide films w > λ2/t, where λ is magnetic field penetration depth, t is film thickness

• Allows setting the Design Rule for the future process nodes up to 7ee (0.18 µm)

Critical Current of Narrow Nb Lines SNC1 and PCM300

0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.70

5

10

15

20

25

30

35

40

45

50

w1/2 at w > 2λ2/t

w2 SNC1-14-1 w3 SNC1-14-1 GL depairing current, uniform

current distribution, w < 2λ2/t GL depairing, current concentration

at edges, w > 2λ2/t

Mea

n cr

itica

l cur

rent

(mA

)Linewidth (µm)

T = 4.2 KjGLc = 0.8 A/µm2

t = 195 nmλ2/t = 41 nm

suggested Design Rule

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.00.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

1.8

2.0

2.2

SNC1-14-1-w4

w4_D1 Rs = 0.93 Ω/sq, dw = 0.016 µm

Con

duct

ance

of u

nit l

engt

h, L

/R (µ

m/Ω

)

Design width, w (µm)

L/R = R-1s (w-dw)

1EOr2A-01-33 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

SFQ5ee Stud Via Development

0.0 0.1 0.2 0.3 0.4 0.50

1

2

3

4

5

6

7

8

I1/2

c (

mA

1/2 )

Design diameter of Nb studs (µm)

c1r4 c4r4 c2r4 c3r4 c5r4 Ic = Jcπd2

av/4, dc= 0.25 µm, b = - 85 nm

dc= 0.285 µm, b = - 50 nm

dav = (d2-d2c)

1/2- b

Jc = 298 mA/µm2(a)

Double Etch and Planarization Process Studs Al

(etch stop)

Demonstrated >5 mA Ic’s for 300-nm stud vias, meeting SFQ5ee requirement

1EOr2A-01-34 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Jc = 20 kA/cm2 (200 µA/µm2) process – JJs sizes: 0.7 µm to 1.6 µm – Ic range: 77 µA to 400 µA

• Ic spreads (1σ) nearly match 10 kA/cm2 process

Higher Jc Junctions: 20-kA/cm2

130 135 140 145 150 155 160 165 170 1750

10

20

30

40

50

60

70

Num

ber o

f Jos

ephs

on ju

nctio

ns

Critical current (µA)

F3_8 Gauss fit

Model Gauss

Equationy=y0 + (A/(w*sqrt(PI/2)))*exp(-2*((x-xc)/w)^2)

Reduced C 22.32039Adj. R-Squ 0.9462

Value Standard

# of JJs

y0 0 0xc 151.27 0.16596w 9.7950 0.33242A 698.22 20.50096sigma 4.8975 0.16621FWHM 11.532 0.3914Height 56.875 1.66846

Jc = 23 kA/cm2

<Ic> = 151.3 µA1σ = 3.24%

70 80 90 100 110 1200

10

20

30

40

50

60

# of

JJs

Current (µA)

E3_6: 0.8-µm JJs Gaussain<Ic> = 93.1 µA

1σ = 4.16%

Model Gauss

Equationy=y0 + (A/(w*sqrt(PI/2)))*exp(-2*((x-xc)/w)^2)

Reduced Chi-Sqr 20.48109Adj. R-Square 0.92678

Value Standard Error

# of JJs

y0 0 0xc 0.09307 1.38969E-4w 0.00775 2.79296E-4A 0.43866 0.01365sigma 0.00387 1.39648E-4FWHM 0.00912 3.28845E-4Height 45.18382 1.40816

0 500 1000 1500 2000 2500 3000 35000

50

100

150

200

250

300

350 20 kA/cm2 process, 1000-JJ string

Cur

rent

(µA)

Voltage (mV)

E3_6: 0.8-µm JJs F3_8: 1.0-µm JJs

1EOr2A-01-35 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• Jc = 50 kA/cm2 (500 µA/µm2) – Self-shunted junctions – βc ~ 1 – JJs sizes: 0.5 µm to 1.2 µm – Ic range: 90 µA to 500 µA

• Ic spreads (1σ) nearly match 10 kA/cm2 process

• IcRn ~ 2.2 mV! • Vg = 2.65 mV – no excess heating!

Higher Jc Junctions: 50-kA/cm2

0 500 1000 1500 2000 25000

20

40

60

80

100

120

140

160

180

Cur

rent

(µA

)

Voltage (mV)

C3_5: 500-nm JJs

50-kA/cm2 process, 1000-JJ string

1EOr2A-01-36 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

• We have developed a fully planarized 8-Nb layer fabrication process (SFQ4ee) for superconductor electronics on a tool set typical for a CMOS foundry with 248-nm photolithography

• The process and its truncated 4-Nb layer version (SFQ3ee) are high yielding processes based on extensive PCM measurements and high yield of operational circuits with tens of thousands of JJs

• We have demonstrated high uniformity and reproducibility of JJ with sizes down to 500 nm and below, sufficiently high to enable VLSI superconducting circuits with over 106 JJ/cm2 at 10 kA/cm2, 20 kA/cm2, and 50 kA/cm2 current densities

• We have developed a fully planarized process for stacked stud-vias with 300 nm diameter for replacing etched vias

• We have demonstrated high-critical-current superconducting Nb lines with linewidth to down to 150 nm at 450 nm pitch

• We are proceeding along our roadmap toward a 10-Nb layer fully planarized process with 180 nm linewidth at 380 nm pitch.

Conclusion

1EOr2A-01-37 11 August 2014

IEEE/CSC SUPERCONDUCTIVITY NEWS FORUM (global edition) October 2014 Invited Presentation 1EOr2A-01 given at ASC 2014, Charlotte, August 10 – 15, 2014

Thank you very much for your attention

Questions?