Mission critical computing by intel

-

Upload

hp-essn-philippines -

Category

Technology

-

view

637 -

download

0

Transcript of Mission critical computing by intel

Itanium in Mission Critical Computing

<speaker name>

<designation>

Itanium Momentum

0%

25%

50%

75%

100%

125%

150%

175%

200%

225%

04Q

1

04Q

2

04Q

3

04Q

4

05Q

1

05Q

2

05Q

3

05Q

4

06Q

1

06Q

2

06Q

3

06Q

4

07Q

1

07Q

2

07Q

3

07Q

4

08Q

1

08Q

2

08Q

3

08Q

4

09Q

1

09Q

2

09Q

3

09Q

4

10Q

1

10Q

2

10Q

3

10Q

4

11Q

1

11Q

2

11Q

3

Itanium-based customer revenue as a percentage of SPARC

APAC Itanium-based system customer revenue as

percentage of Power* and SPARC* By Quarter

New OEMs

77%

134%

It’s A $4B Business…

Source: IDC Q4 ‘11 APAC Server Tracker

Mission Critical Workloads

• 1,000s – 1,000,000+ online users

• Support large transactional databases

• 24 x 7 operation

• Enable all users

• Complex queries

• Multiple data sources

• Large data warehouse

• Large scalable enterprise databases

• No single point of failure

• Extremely fast operational speed

Transaction Processing

Database Business

Intelligence and Analytics

Growth in Volume & Velocity of Data and Transactions

New Mission Critical Economics

Powering the next generation of mission critical computing

Common Ingredients

Open VMS

HP NonStop

Buffers Chipset

Interconnects Memory

Performance

Beyond Mission Critical Economics...

Performance RAS Energy Efficiency

Commitment to Itanium Roadmap

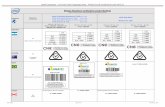

65nm

Tukwila

32nm

22nm

Poulson Kittson

Poulson

• New architecture for breakthrough in Itanium Performance

• Greater reliability to extend mainframe class resiliency

• Fully compatible with existing applications

• With HP-UX… the Leading UNIX platform

Poulson: Most Significant Itanium®

Processor to Date

Key Highlights

• New architecture - 2x the cores, 2x instructions throughput

• Total 54MB on-die memory

• 3.1 Billion Transistors on 32nm process

Key Capabilities

• Intel® Instruction Replay Technology

• Intel® Hyper-Threading Technology, enhanced with dual-domain multi-threading support

• Intel® Itanium New Instructions

On track for 2012!

New Itanium Architecture

Improved Power Management and RAS features

Innovative engineering work

• Doubles the number of high capacity cores

• Delivers maximum 12-issue execution EPIC architecture

• Supports higher speed system interconnects (QPI, SMI)

• Enables accurate Core power prediction and management

• Expands cache and logic error detection and correction

• Achieves mainframe reliability and resiliency with high levels of RAS feature integration

• First reported 3.1B transistors general purpose processor

• New core design for next decade of Itanium computing

• Industry leading cache design and density

Poulson Advances Itanium® Architecture

Most Significant Itanium Processor To Date

Improved Power Management

• Accurate power monitoring and control to deliver power where it is needed

• Design optimizations to reduce dynamic and leakage power

• Enhanced DIMM clock gating to reduce system power consumption

• Reduced overall socket power consumption

Power savings beyond technology scaling

Note: Lower is better

+70% Better*

+60% Better*

+30% Better*

Leakage Current

Idle Activity

TDP Activity

Ratio

Core Power Scaling

Note: Poulson compared to Tukwila when scaled to equivalent process technology

• Expanded soft error resilient flops and logic structures usage

• Hardware/Software mechanisms enabling correctable parity errors

Increases Process

Resiliency

Improves Execution Integrity

Minimizes Service

Interruption

Error Prevention and

Correction

End to End Error Detection

Improved Firmware Error

Handling

• Enhanced Cache error coverage

• Residual error protection for floating-point operations

• Expanded coverage of potential error events for automatic recovery

• Improved logging and configurations for higher availability and serviceability

Poulson RAS Advances Increase System and Application Resiliency

Enhanced error prevention, detection and correction

Instruction Replay

Technology

• Expanded error detection captures more errors

• Errant instructions are then re-executed from Instruction buffer to auto recover from severe errors

Improves System

Resiliency

Greater Parallelism with Intel® Hyper-Threading Technology Improvements

Back-End Front-End

Instruction

Buffer

Instruction

Buffer

Dual-Domain Multithreading support enhances performance

• Minimizes thread switching costs of traditional Itanium MT implementation

• Maximizes efficiency of concurrent threads to complement 12-issue instruction execution

11

Unique EPIC architecture implementation to increase overall throughput

Poulson Architecture & The New Instructions – Foundation For Future Itanium

Itanium® Processor New Instructions

Individual Poulson Core

Bu

ffe

rs

Floating Point

Execution

Integer Execution

1st level

Cache

1st level

Cache

Branch

Predict

Interface

Logic

1st

level

Cache

Mid-

Level

Inst.

Cache

Pipe Line

Control

Mid-

Level

Data

Cache

Instr

uctio

n

Qu

eu

es

Bu

ffe

rs

Integer

Register

Floating

Pt RF

BR

CTL

Thread Control • hint@priority

Integer Operations • mpy4 • mpyshl4 • clz

Expanded Software Prefetch

• ifetch.count

Expanded Data Access Hints

• mov dahr

• Poulson continues to optimize for legacy Itanium code without recompilation

• New instructions simplify common tasks and branch operations to help take future Itanium performance to the next level

12

Performance

Delivering Mission Critical Computing

Transactions at your fingertips Data to support customers Real-time Business Analytics

• Modernize mission-

critical solutions

infrastructure

• Innovate to keep up

with market dynamics

• Improve economic

efficiency

• Lower operational costs

• Highly reliable, scalable

performing systems

Summary

HP & Intel have a history of transforming IT

Strong roadmaps for Itanium & Xeon

HP and Intel committed to Mission Critical computing

Announced at IDF Beijing, 2011

Two New Itanium OEMs…

Xeon E7 Series

Architected for scalable Windows and Linux performance with advanced reliability

Family of Mission Critical Processors

Itanium 9300 Series

Architected for Mission Critical UNIX with mainframe resiliency and scalability

Two server platforms to meet a wide range of mission critical requirements

• Hardened Operating System

• Application Availability

• OEM System Capability

• OEM Service & Support

All dates, product features and plans are subject to change without notice.

Accelerating Mission Critical Transformation

Intel® Xeon® Processor E7-8800/4800/2800 Product Families

• Lower partial active & idle power via Intel Intelligent Power Technology2

• Support for Low Voltage-DIMMs3

More Efficient

• Supports 32GB DDR3 DIMMs (2TB per 4-socket system)1

More Expandable

More Security & RAS

• 10 cores / 20 threads

• 30MB of last level cache

More Performance

SECURITY

• Intel® Advanced Encryption Standard-New Instructions

RELIABILITY, AVAILABILITY, SERVICEABILITY

• Enhanced DRAM Double Device Data Correction

New Poulson Core Architecture

Key Architectural Advances

• New Data and Instruction Pipelines

• New Floating Point Pipeline

• New Instruction Buffer

• Double max execution width

(6 to12)

Derived Benefits

• Increased instruction throughput

• Improved performance/watt

• Improved RAS coverage

• Process optimized core layout

Enables leap in performance, power reduction and reliability

Buff

ers

Individual Poulson Core

Floating Point

Execution

Integer Execution

1st level

Cache

1st level

Cache

Branch

Predict

Interface

Logic

1st

level

Cache

Mid-

Level

Inst.

Cache

Pipe Line

Control

Mid-

Level

Data

Cache

Instr

uctio

n

Qu

eu

es

Buff

ers

Integer

Register File

Floating

Pt RF

BR

CTL

Poulson Delivers Investment Protection

• Pin compatible support for Itanium® 9300 processor

• 33% Bandwidth improvement via higher bus speeds (QPI and SMI)

• Poulson continues to take advantage of common platform ingredients with Xeon architecture

Building on the common platform vision

Intel® QuickPath and Scalable Memory Interconnects

Intel® Scalable Memory Buffer and DDR3

Intel® Chipset

Common Platform Ingredients with Xeon

Itanium 9300 series-based Platform

Poulson-based Platform

Poulson