Microtronix ViClaro II Development Board

Transcript of Microtronix ViClaro II Development Board

9-1510 Woodcock St. London, ON Canada N5H 5S1 www.microtronix.com

Microtronix ViClaro II Development Board

User Manual

Page 2 of 13

This user guide provides basic information about using the Microtronix ViClaro II Development Board. The following table shows the document revision history.

Date Description

December 2006 Initial Release – Version 1.0

March 2006 Added Errata – Version 1.1

E-mail Sales Information: [email protected]

Support Information: [email protected]

Website General Website: http://www.microtronix.com

Nios Forum Website: http://www.niosforum.com

Phone Numbers General: (001) 519-690-0091

Fax: (001) 519-690-0092

Path/Filename A path/filename

[SOPC Builder]$ <cmd> A command that should be run from within the Cygwin Environment.

Code Sample code.

Indicates that there is no break between the current line and the next line.

Document Revision History

How to Contact Microtronix

Typographic Conventions

ViClaro II User Manual

Page 3 of 13

Table of Contents

Document Revision History ............................................................................................................. 2

How to Contact Microtronix ............................................................................................................. 2

E-mail ........................................................................................................................................... 2

Website ........................................................................................................................................ 2

Phone Numbers ........................................................................................................................... 2

Typographic Conventions................................................................................................................ 2

Introduction ...................................................................................................................................... 4

Power Supply................................................................................................................................... 5

Configuration ................................................................................................................................... 5

Clocking ........................................................................................................................................... 5

Board Components.......................................................................................................................... 6

Cyclone II.................................................................................................................................. 6

User LEDs ................................................................................................................................ 6

I2C............................................................................................................................................. 6

DDR2 SDRAM.......................................................................................................................... 7

HDMI Receiver ......................................................................................................................... 8

HDMI Transmitter ..................................................................................................................... 9

LVDS ...................................................................................................................................... 10

Expansion Headers ................................................................................................................ 11

Errata ............................................................................................................................................. 12

Appendix A. Schematics................................................................................................................ 13

ViClaro II User Manual

Page 4 of 13

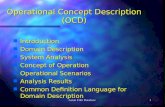

The Microtronix ViClaro II Video Enhancement IP Development Platform is targetted at the development of consumer video display and imaging systems. It is designed to demonstrate the capabilities of Altera's Cyclone II for video and image enhancements applications in Video Display Controller ASSP systems. Figure 1 shows the ViClaro II board.

• Altera Cyclone II FPGA (EP2C35F484C6)

• 64 Mbyte DDR2 SDRAM (256 Mbit x 32) running up to 400 MHz data rate.

• Dual 5-channel LVDS receiver and LVDS transmitter

• HDMI receiver and analog video input

• HDMI transmitter

• I2C interface port

• Expansion header

Introduction

DDR2 SDRAMHDMI

TransmitterLVDS

Transmitter

HDMIReceiver

LVDSReceiver JTAG

I2C

Analog Video

Cyclone II

Expansion Headers

POWER PLUG

ViClaro II User Manual

The on-board switching regulators generate all board voltages (1.2V, 1.8V, 2.5V and 3.3V). Additionally a linear regulator generates 5V required for the I2C and HDMI interfaces.

The board is powered through the 2.5mm power jack input using an external +12V DC power supply. The center pin is the postive terminal.

The Cyclone II device can be configured in JTAG stand-alone mode or active serial mode. At power-up the EPCS serial flash device configures the Cyclone II device. If the configuration is successful, the CONF_DONE LED illuminates.

The EPCS device can be programmed using JTAG in-system programming.

The board has a 50.0 MHz crystal oscillator. Figure 2 shows the clocking circuitry.

Power Supply

Configuration

Clocking

Cyclone II

CLK12 (V12) CLK2 (M1)

CLK0 (L1)

CLK1 (L2)

CLK13 (W12)

CLK3 (M2)

(D5) PLL3_OUT

LVDSCLK5 (E12)

LVDSCLK4 (A12)

50.0 MHz

Oscillator Santa Cruz

BUFFER

HDMI RX Audio Clock

Santa Cruz

HDMI RX Clock

LVDS RX Odd ClockLVDS RX Even Clock

Figure 2. Clocking Circuitry

Page 5 of 13

ViClaro II User Manual

Page 6 of 13

Cyclone II

The ViClaro II board is fitted with an Altera Cyclone II EP2C35 device in 484-pins Fineline BGA package with speedgrade -6.

For more information on Cyclone II devices, refer to the Cyclone II Device Handbook.

User LEDs

There are two general purpose LEDs driven by the Cyclone II device. The LEDs are located in bank 1.

Table 1. LED Pins

Cyclone II Pin Number

LED1 R8

LED2 R7

I2C

The ViClaro II board has an I2C interface, which can be used to access the (optional) I2C controller / slave in the Cyclone II. Also it provides access to the HDMI receiver and transmitter I2C interface. The interface has two level shifters, so an external I2C master can be connected without damaging the Cyclone II device. Also an 5 volt power supply and pull-up resistors are provided.

Table 2. I2C Pins

Cyclone II Pin Number

SCL N2

SDA N1

Board Components

ViClaro II User Manual

Page 7 of 13

DDR2 SDRAM

The ViClaro II board has two Micron DDR2 SDRAM devices (MT47H16M16BG-3) with a total capacity of 256 Mbit x 32. The memory devices are connected to banks 5 and 6 of the Cyclone II device and uses the SSTL-18 I/O-standard. The two banks are powered with the 1.8V power supply. The board is designed for matched length traces across all DDR2 signals. All unused I/O-pins in the banks are connected to ground. Table x lists the DDR2 pin-outs.

Table 3. DDR2 SDRAM Pins

Signal Name

Cyclone II Pin Number

Signal Name

Cyclone II Pin Number

Signal Name

Cyclone II Pin Number

Signal Name

Cyclone II Pin Number

CKE H18 BA0 K18 DQ0 C22 DQ16 R19

CLK1 E18 BA1 K17 DQ1 F20 DQ17 Y20

CLK1# E19 A0 J19 DQ2 C21 DQ18 W20

CLK2 U18 A1 L17 DQ3 E20 DQ19 V19

CLK2# T18 A2 H19 DQ4 E21 DQ20 W22

CS# N22 A3 M16 DQ5 C20 DQ21 R17

RAS# P21 A4 K22 DQ6 E22 DQ22 W21

CAS# N21 A5 P19 DQ7 C19 DQ23 R18

WE# J18 A6 K21 DQ8 D22 DQ24 T22

ODT G18 A7 P20 DQ9 G21 DQ25 V21

A8 J22 DQ10 D21 DQ26 V22

A9 R21 DQ11 G22 DQ27 V20

DQS0 F22 A10 J15 DQ12 H21 DQ28 Y22

DQS0# F21 A11 J21 DQ13 J17 DQ29 U19

DQS1 L18 A12 R22 DQ14 H22 DQ30 Y21

DQS1# L19 DQ15 H16 DQ31 T21

DQS2 U22 DQM0 H17

DQS2# U21 DQM1 G17

DQS3 M18 DQM2 Y18

DQS3# M19 DQM3 Y19

ViClaro II User Manual

Page 8 of 13

HDMI Receiver

The Viclaro II board contains a dual analog / HDMI video receiver. The AD9880 from Analog Devices supports all HDTV formats (up to 1080p and 720 p) and display resolutions up to SXGA (1280 x 1024 @ 75 Hz). The HDMI receiver interface pins are located in bank 2 and this bank is powered at 3.3 volts. Table x lists the FPGA pins.

Table. 4. HDMI Receiver Pins

Signal NameCyclone II Pin Number

Signal Name

Cyclone II Pin Number

CLK L1 G6 H2

DE J3 G7 H1

HS J4 B0 D3

VS J5 B1 D4

FIELD J6 B2 E3

R0 F3 B3 E4

R1 F4 B4 C2

R2 G3 B5 C1

R3 G5 B6 D2

R4 H3 B7 D1

R5 H4

R6 J1 MCLK L2

R7 J2 SCLK L7

G0 E2 LRCLK L8

G1 E1 SPDIF D6

G2 F2 I2S0 M6

G3 F1 I2S1 H6

G4 G2 I2S2 G6

G5 G1 I2S3 H5

ViClaro II User Manual

Page 9 of 13

HDMI Transmitter

The ViClaro II board has a HDMI transmitter from Analog Devices. The AD9889B supports HDTV formats up to 1080p and computer graphics resolutions up to UXGA (1600 x 1200 @ 60 Hz). The HDMI transmitter interface pins are located in bank 1 and this bank is powered at 3.3 volts.

Table 5. HDMI Transmitter Pins

Signal NameCyclone II Pin Number

Signal Name

Cyclone II Pin Number

CLK Y3 MCLK R5

DE T3 SCLK W4

HS U3 LRCLK Y4

VS W3 SPDIF R6

D0 R1 I2S0 T5

D1 R2 I2S1 T6

D2 T1 I2S2 U4

D3 T2 I2S3 V4

D4 U1

D5 U2

D6 V1

D7 V2

D8 W1

D9 W2

D10 Y1

D11 Y2

ViClaro II User Manual

Page 10 of 13

LVDS

The ViClaro II board provides a dual LVDS transmitter running at 622 Mbps per channel and a dual LVDS receiver with each 5-channels running at 805 Mbps per channel.

The LVDS receiver pins are located is bank 3 and 4 and are terminated with a 100 Ω resistor. The LVDS transmitter pins are located in banks 7 and 8. All LVDS banks are powered at 2.5 volts.

The LVDS connector is Hirose part number DF13-40DP-1.25V. The mating socket is DF13-40DS-1.25C

For more information on the LVDS connectors see the Hirose website (www.hirose-connectors.com)

Table 6. LVDS pin numbers

Signal Name

Cyclone II Pin Number

Signal Name

Cyclone II Pin Number

Signal Name

Cyclone II Pin Number

Signal Name

Cyclone II Pin Number

RXE_CLK+ A12 RXO_CLK+ E12 TXE_CLK+ AB9 TXO_CLK+ AB11

RXE_CLK- B12 RXO_CLK- D12 TXE_CLK- AA9 TXO_CLK- AA11

RXE_A+ A4 RXO_A+ A3 TXE_A+ AB3 TXO_A+ AB4

RXE_A- B4 RXO_A- B3 TXE_A- AA3 TXO_A- AA4

RXE_B+ A8 RXO_B+ A7 TXE_B+ AB7 TXO_B+ AB8

RXE_B- B8 RXO_B- B7 TXE_B- AA7 TXO_B- AA8

RXE_C+ A15 RXO_C+ A14 TXE_C+ AB14 TXO_C+ AB15

RXE_C- B15 RXO_C- B14 TXE_C- AA14 TXO_C- AA15

RXE_D+ A18 RXO_D+ A17 TXE_D+ AB17 TXO_D+ AB18

RXE_D- B18 RXO_D- B17 TXE_D- AA17 TXO_D- AA18

RXE_E+ A20 RXO_E+ A19 TXE_E+ AB19 TXO_E+ AB20

RXE_E- B20 RXO_E- B19 TXE_E- AA19 TXO_E- AA20

ViClaro II User Manual

Page 11 of 13

Expansion Headers

The ViClaro II board provides three expansion headers. These connectors use standard 0.1’’ headers and can be used for Altera daughter cards (e.g. Santa Cruz) or for debugging purposes. The expansion header signals are located in banks 1, 3, 4, 7, and 8. Due to the different bank power supplies, the expansion header signals located in banks 3, 4, 7, and 8 will drive out maximum 2.5 volts, while the signals in bank 1 will drive out 3.3 volts. All inputs are 3.3 volts complaint.

If in a design both the LVDS signals and the expansion headers signals H11 and C14 are used, then the Quartus assignment Toggle Rate must set to 0 MHz to prevent a compilation error.

Table 7. Expansion Header Pins

GND 1 2 NC NC 1 2 GND

J14 3 4 H14 C7 3 4 E7

H11 5 6 G11 C10 5 6 D7

F11 7 8 F10 C14 7 8 A10

B10 9 10 H7 C16 9 10 E15

F8 11 12 G7 D16 11 12 D15

M8 13 14 R16 AA13 13 14 W15

AB13 15 16 AA12

Y7 17 18 AB12

GND 19 20 NC

VIN 1 2 GND AA6 21 22 GND

NC 3 4 GND AB6 23 24 GND

3.3V 5 6 GND T8 25 26 GND

3.3V 7 8 GND U8 27 28 P6

OSC 9 10 GND P5 29 30 GND

NC 11 12 GND P4 31 32 P3

M2 13 14 GND P2 33 34 NC

3.3V 15 16 GND P1 35 36 N6

3.3V 17 18 GND N5 37 38 N4

3.3V 19 20 GND N3 39 40 GND

ViClaro II User Manual

An issue with the HDMI transmitter and receiver PLL power supply stability was identified. The effect of this issue may cause unstable behavior of the HDMI video data.

To improve the stability an extra capacitor (range 2.2 uF – 10 uF) must be added to the PLL power supply.

Errata

Figure 3. HDMI Transmitter

Figure 4. HDMI Receiver

Page 12 of 13