Lecture 3 - Harvey Mudd Collegepages.hmc.edu/harris/class/e85/lect3.pdfDigital Design and Computer...

Transcript of Lecture 3 - Harvey Mudd Collegepages.hmc.edu/harris/class/e85/lect3.pdfDigital Design and Computer...

Lecture 3: Timing &Sequential Circuits

E85 Digital Design & Computer Engineering

Lecture 3 <2> Digital Design and Computer Architecture: ARM® Edition © 2015

• Timing• Sequential Circuits• Latches and Flip-Flops• Synchronous Logic Design

Lecture 3

Lecture 3 <3> Digital Design and Computer Architecture: ARM® Edition © 2015

A logic circuit is composed of:• Inputs• Outputs• Functional specification• Timing specification

inputs outputsfunctional spec

timing spec

Introduction

Lecture 3 <4> Digital Design and Computer Architecture: ARM® Edition © 2015

A

Y

Time

delay

A Y

• Delay: time between input change and output changing

• How to build fast circuits?

Timing

Lecture 3 <5> Digital Design and Computer Architecture: ARM® Edition © 2015

A

Y

Time

A Y

tpd

tcd

• Propagation delay: tpd = max delay from input to output

• Contamination delay: tcd = min delay from input to output

Propagation & Contamination Delay

Lecture 3 <6> Digital Design and Computer Architecture: ARM® Edition © 2015

• Delay is caused by– Capacitance and resistance in a circuit– Speed of light limitation

• Reasons why tpd and tcd may be different:– Different rising and falling delays– Multiple inputs and outputs, some of which are

faster than others– Circuits slow down when hot and speed up when

cold

Propagation & Contamination Delay

Lecture 3 <7> Digital Design and Computer Architecture: ARM® Edition © 2015

AB

C

D Y

Critical Path

Short Path

n1n2

Critical (Long) Path: tpd = 2tpd_AND + tpd_OR

Short Path: tcd = tcd_AND

Critical (Long) & Short Paths

Lecture 3 <8> Digital Design and Computer Architecture: ARM® Edition © 2015

Example: 8-input OR Delay

• Find the minimum and maximum delay of this 8-input OR

Cell Propagation Delay (ps) Contamination Delay (ps)OR2 20 15OR3 25 19OR4 35 28

Lecture 3 <9> Digital Design and Computer Architecture: ARM® Edition © 2015

Solution: 8-input OR Delay

• Find the minimum and maximum delay of

this 8-input OR

• Annotate each node with earliest and latest arrivals

• Min = 15 ps from A7 to Y.

• Max = 140 ps from A0 to Y.

Cell Propagation Delay (ps) Contamination Delay (ps)OR2 20 15

OR3 25 19

OR4 35 28

Lecture 3 <10> Digital Design and Computer Architecture: ARM® Edition © 2015

Example: Optimized 8-input OR

• Redesign the 8-input OR to be as fast as possible.

Cell Propagation Delay (ps) Contamination Delay (ps)OR2 20 15OR3 25 19OR4 35 28

Lecture 3 <11> Digital Design and Computer Architecture: ARM® Edition © 2015

Example: Optimized 8-input OR

• Redesign the 8-input OR to be as fast as possible.

• Try various possibilities:

Cell Propagation Delay (ps) Contamination Delay (ps)OR2 20 15OR3 25 19OR4 35 28

Lecture 3 <12> Digital Design and Computer Architecture: ARM® Edition © 2015

Solution: Optimized 8-input OR

• Redesign the 8-input OR to be as fast as possible.

• Annotate delays. OR3+OR3 is fastest (50 ps).

Cell Propagation Delay (ps) Contamination Delay (ps)OR2 20 15OR3 25 19OR4 35 28

Lecture 3 <13> Digital Design and Computer Architecture: ARM® Edition © 2015

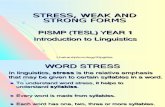

• Outputs of sequential logic depend on current

and prior input values – it has memory.

• Some definitions:

– State: all the information about past inputs

necessary to explain its future behavior

– Latches and flip-flops: state elements that store

one bit of state

– Synchronous sequential circuits: combinational

logic followed by a bank of flip-flops

Sequential Logic Introduction

Lecture 3 <14> Digital Design and Computer Architecture: ARM® Edition © 2015

• Give sequence to events• Have memory (short-term)• Use feedback from output to input to store

information

Sequential Circuits

Lecture 3 <15> Digital Design and Computer Architecture: ARM® Edition © 2015

• The state of a circuit influences its future behavior

• State elements store state– Bistable circuit– SR Latch– D Latch– D Flip-flop

State Elements

Lecture 3 <16> Digital Design and Computer Architecture: ARM® Edition © 2015

QQ Q

Q

I1

I2

I2 I1

• Fundamental building block of other state elements

• Two outputs: Q, Q• No inputs

Bistable Circuit

Lecture 3 <17> Digital Design and Computer Architecture: ARM® Edition © 2015

Q

Q

I1

I2

0

1

1

0

Q

Q

I1

I2

1

0

0

1

• Consider the two possible cases:– Q = 0:

then Q = 0, Q = 1 (consistent)

– Q = 1: then Q = 1, Q = 0 (consistent)

• Stores 1 bit of state in the state variable, Q (or Q)

• But there are no inputs to control the state

Bistable Circuit Analysis

Lecture 3 <18> Digital Design and Computer Architecture: ARM® Edition © 2015

R

S

Q

Q

N1

N2

• SR Latch

• Consider the four possible cases:

– S = 1, R = 0– S = 0, R = 1– S = 0, R = 0– S = 1, R = 1

SR (Set/Reset) Latch

Lecture 3 <19> Digital Design and Computer Architecture: ARM® Edition © 2015

– S = 1, R = 0: then Q = 1 and Q = 0Set the output

– S = 0, R = 1: then Q = 0 and Q = 1Reset the output

SR Latch Analysis

R

S

Q

Q

N1

N2

1

0

0

10

1

R

S

Q

Q

N1

N2

0

1

1

00

0

11

Lecture 3 <20> Digital Design and Computer Architecture: ARM® Edition © 2015

R

S

Q

Q

N1

N2

0

0

R

S

Q

Q

N1

N2

0

0

0

Qprev = 0 Qprev = 1– S = 0, R = 0: then Q = QprevMemory!

– S = 1, R = 1: then Q = 0, Q = 0Invalid StateQ ≠ NOT Q

SR Latch Analysis

R

S

Q

Q

N1

N2

1

1

0

00

0

1

Lecture 3 <21> Digital Design and Computer Architecture: ARM® Edition © 2015

S

R Q

Q

SR LatchSymbol

• SR stands for Set/Reset Latch– Stores one bit of state (Q)

• Control what value is being stored with S, Rinputs– Set: Make the output 1

(S = 1, R = 0, Q = 1)– Reset: Make the output 0

(S = 0, R = 1, Q = 0)• Avoid invalid state

(when S = R = 1)

SR Latch Symbol

Lecture 3 <22> Digital Design and Computer Architecture: ARM® Edition © 2015

D LatchSymbol

CLKD Q

Q

• Two inputs: CLK, D– CLK: controls when the output changes– D (the data input): controls what the output changes to

• Function– When CLK = 1,

D passes through to Q (transparent)– When CLK = 0,

Q holds its previous value (opaque)• Avoids invalid case when

Q ≠ NOT Q

D Latch

Lecture 3 <23> Digital Design and Computer Architecture: ARM® Edition © 2015

S

R Q

Q

Q

QD

CLKD

R

S

CLKD Q

Q

S R Q0 0 Qprev0 1 01 0 1

Q

10

CLK D0 X1 01 1

DX10

Qprev

D Latch Internal Circuit

Lecture 3 <24> Digital Design and Computer Architecture: ARM® Edition © 2015

D Flip-FlopSymbols

D QQ

• Inputs: CLK, D• Function

– Samples D on rising edge of CLK• When CLK rises from 0 to 1, D

passes through to Q• Otherwise, Q holds its previous

value– Q changes only on rising edge of CLK

• Called edge-triggered• Activated on the clock edge

D Flip-Flop

Lecture 3 <25> Digital Design and Computer Architecture: ARM® Edition © 2015

CLKD Q

Q

CLKD Q

Q

D N1

CLK

L1 L2

• Two back-to-back latches (L1 and L2) controlled by

complementary clocks

• When CLK = 0– L1 is transparent

– L2 is opaque

– D passes through to N1

• When CLK = 1– L2 is transparent

– L1 is opaque

– N1 passes through to Q

• Thus, on the edge of the clock (when CLK rises from 0 1)

– D passes through to Q

D Flip-Flop Internal Circuit

Lecture 3 <26> Digital Design and Computer Architecture: ARM® Edition © 2015

CLK

D

Q (latch)

Q (flop)

D Latch vs. D Flip-FlopCLKD Q

QD Q

Q

Lecture 3 <27> Digital Design and Computer Architecture: ARM® Edition © 2015

CLK

D Q

D Q

D Q

D Q

D0

D1

D2

D3

Q0

Q1

Q2

Q3

D3:04 4

CLK

Q3:0

Registers: Multi-bit Flip-Flop

Lecture 3 <28> Digital Design and Computer Architecture: ARM® Edition © 2015

InternalCircuit

D Q

CLKEN

DQ

0

1D QEN

Symbol

• Inputs: CLK, D, EN– The enable input (EN) controls when new data (D) is stored

• Function– EN = 1: D passes through to Q on the clock edge

– EN = 0: the flip-flop retains its previous state

Enabled Flip-Flops

Lecture 3 <29> Digital Design and Computer Architecture: ARM® Edition © 2015

Symbols

D QReset

r

• Inputs: CLK, D, Reset• Function:

– Reset = 1: Q is forced to 0

– Reset = 0: flip-flop behaves as ordinary D flip-flop

Resettable Flip-Flops

Lecture 3 <30> Digital Design and Computer Architecture: ARM® Edition © 2015

• Two types:– Synchronous: resets at the clock edge only– Asynchronous: resets immediately when Reset = 1

• Asynchronously resettable flip-flop requires changing the internal circuitry of the flip-flop

• Synchronously resettable flip-flop?

Resettable Flip-Flops

Lecture 3 <31> Digital Design and Computer Architecture: ARM® Edition © 2015

Resettable Flip-Flops

InternalCircuit

D Q

CLK

D QReset

• Two types:– Synchronous: resets at the clock edge only

– Asynchronous: resets immediately when Reset = 1

• Asynchronously resettable flip-flop requires changing the internal circuitry of the flip-flop

• Synchronously resettable flip-flop

Lecture 3 <32> Digital Design and Computer Architecture: ARM® Edition © 2015

Symbols

D QSet

s

• Inputs: CLK, D, Set• Function:

– Set = 1: Q is set to 1 – Set = 0: the flip-flop behaves as ordinary D flip-flop

Settable Flip-Flops

Lecture 3 <33> Digital Design and Computer Architecture: ARM® Edition © 2015

X Y Z

• Sequential circuits: all circuits that aren’t combinational

• A problematic circuit:

• No inputs and 1-3 outputs• Astable circuit, oscillates• Period depends on inverter delay• It has a cyclic path: output fed back to input

Sequential Logic

XYZ

time (ns)0 1 2 3 4 5 6 7 8

Lecture 3 <34> Digital Design and Computer Architecture: ARM® Edition © 2015

• Multi-input XOR: Odd parity

SystemVerilog Description

module flop(input logic clk, d,output logic q);

always_ff @(posedge clk)q <= d;

endmodule

Lecture 3 <35> Digital Design and Computer Architecture: ARM® Edition © 2015• Multi-input XOR: Odd parity

SystemVerilog Descriptionmodule flopenr(input logic clk, en, reset, d,

output logic q);

always_ff @(posedge clk, posedge reset)if (reset) q <= 0;else if (en) q <= d;

endmodule

Lecture 3 <36> Digital Design and Computer Architecture: ARM® Edition © 2015

• Multi-input XOR: Odd parity

SystemVerilog Description

module flopenr #(parameter WIDTH = 4)(input logic clk, reset, en,input logic [WIDTH-1:0] d, output logic [WIDTH-1:0] q);

always_ff @(posedge clk, posedge reset) if (reset) q <= 0;else if (en) q <= d;

endmodule

Lecture 3 <37> Digital Design and Computer Architecture: ARM® Edition © 2015

• Breaks cyclic paths by inserting registers• Registers contain state of the system

• State changes at clock edge: system synchronized to the clock

• Rules of synchronous sequential circuit composition:– Every circuit element is either a register or a combinational circuit

– At least one circuit element is a register– All registers receive the same clock signal

– Every cyclic path contains at least one register

• Two common synchronous sequential circuits– Finite State Machines (FSMs)– Pipelines

Synchronous Sequential Logic Design