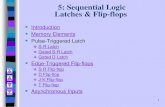

Latches, Flip-Flops BIL- 223 Logic Circuit Design Ege University Department of Computer Engineering.

-

Upload

milton-walker -

Category

Documents

-

view

217 -

download

0

Transcript of Latches, Flip-Flops BIL- 223 Logic Circuit Design Ege University Department of Computer Engineering.

Latches, Flip-Flops

BIL- 223 Logic Circuit Design

Ege UniversityDepartment of Computer

Engineering

A TV channel control example

CH 2 CH 3

CH 1

0

0

1 1

1

0

Introduction to Sequential Circuits

Combinational

LogicStorage Elements

Inputs Outputs

StateNextState

Sequential circuits • Combinational logic circuits• State information (stored in memory)

Output is a function of inputs and present state Can be synchronous or asynchronous

clock

Clocks and synchronization A clock is a special device that whose output continuously

alternates between 0 and 1.

The time it takes the clock to change from 1 to 0 and back to 1 is called the clock period, or clock cycle time.

The clock frequency is the inverse of the clock period. The unit of measurement for frequency is the hertz.

Clocks are often used to synchronize circuits. They generate a repeating, predictable pattern of 0s and 1s that

can trigger certain events in a circuit. If several circuits share a common clock signal, they can

coordinate their actions with respect to one another. This is similar to how humans use real clocks for synchronization.

clock period

0.4

0.5

0.4

SY0.2

Storing Information

0.2 ns 0.5

ns0.4 ns

SR LatchS R Q QN

0 0 Q Q

0 1 0 1

1 0 1 0

1 1 0 0

Reset

Set

Undefined

No Change

S

Q

QN

R

S

R

Q

QN

Race, and Unstable

S

R

SR

SR Latch

S R Q QN

0 0 1 1

0 1 1 0

1 0 0 1

1 1 Q Q

R

Q

QN

S

ResetSet

Undefined

No Change

SR

S

R

SR Latch with Control Input

C S R Q QN

0 X X Q Q

1 0 0 Q Q

1 0 1 0 1

1 1 0 1 0

1 1 1 1 1

Q

QN

R

C

S

ResetSet

Undefined

No ChangeNo Change

D LatchQ

QN

C

D

C D Q QN

0 X Q Q

1 0 0 1

1 1 1 0 D with 1 Control

D

C

D

C

D with 0 Control

Transparency

D Latch is called “transparent”: Output follows input instantaneously

Desired behavior: Y changes only once per clock pulse

C

D

Q

Q

Latch Transparency Problem

C1

D Q D

C

DQ

Oscillating Unstable

C

S

R

Q

Q

C

R

Q

Q

C

S

R

QS

Q

S-R Master-Slave Flip-FlopY

C

S

R

Y

Q

Glitch

1s Catching Problem

Master SlaveS and R must be stable during clock pulse for the correct operation

PULSE TRIGGERED

Negative Edge Triggered D Flip-Flop

C

Q2

D

C

S

R

Q

QC

Q

QC

D QD

Q

Q1

Positive Edge Triggered D Flip-Flop

C

S

R

Q

QC

Q

QC

D QD

Q

C

Q1

D

Q2

Pulse Triggered

Edge-Triggered:

Triggered D

(b) Master-Slave Flip-Flops

D

C

Triggered DTriggered SR

S

R

C

D

C

Triggered SR

S

R

C

(c) Edge-Triggered Flip-Flops

Triggered D

D

C

Triggered D

D

C

Standard Symbols for Flip-Flops

Direct Inputs Direct R and/or S inputs that control the state

of the latches within the flip-flops asynchroniously.

For the example flip-flop shown 0 applied to R resets the flip-flop to the 0 state 0 applied to S sets the flip-flop to the 1 state

D

C

S

R

Q

Q

S-R Flip-Flop Descriptors

0

0

1

1

OperationS

0

1

0

1

R

No change

Reset

Set

Undefined

0

1

?

Q(t+1)

Q(t)

Operation

No change

Set

Reset

No change

S

X

0

1

0

Q(t+ 1)

0

1

1

0

Q(t)

0

0

1

1

R

X

0

1

0

Characteristic Table

Excitation Table

Q(t) (t)R S(t) 1)Q(t Characteristic Equation

D Flip-Flop Descriptors

Characteristic Table

Excitation Table

(t) 1)Q(t DCharacteristic Equation

D

01

Operation

ResetSet

01

Q(t 1)+ Q(t+1)

01

01

D Operation

ResetSet

J-K Flip-flop

D

CK

JJ

C

K

0

0

1

1

No change

Set

Reset

Complement

OperationJ

0

1

0

1

K

0

1

Q(t +1)

Q(t)

Q(t)

Q(t+1)

0

1

1

0

Q(t)

0

0

1

1

Operation

X

X

0

1

K

0

1

X

X

J

No change

Set

Reset

No Change

Characteristic Table

Excitation Table

Q(t) (t)K (t)QJ(t) 1)Q(t Characteristic Equation

T Flip-flop

Characteristic Table

Excitation Table

Q(t) T(t) 1)Q(t Characteristic Equation

C

DT

T

C

No change

Complement

Operation

0

1

T Q(t 1)

Q(t)

Q(t)

+ Q(t+1)

Q(t)

1

0

T

No change

Complement

Operation

Q(t)

Flip-flop Behavior Example Use the characteristic tables to find the output

waveforms for the flip-flops shown:

T

C

ClockD,T

QD

QT

D

C

Flip-Flop Behavior Example (continued)

Use the characteristic tables to find the output waveforms for the flip-flops shown:

JC

K

SCR

ClockS,J

QSR

QJK

R,K

?