Intro MIPS Computer Organization I 1 CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens The...

-

Upload

michael-melton -

Category

Documents

-

view

216 -

download

2

Transcript of Intro MIPS Computer Organization I 1 CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens The...

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

1The Stored Program Computer

1945: John von Neumann– Wrote a report on the stored program concept, known as the First Draft of a Report on

EDVAC – also Alan Turing… Konrad Zuse… Eckert & Mauchly…

The basic structure proposed in the draft became known as the “von Neumann machine” (or model).

– a memory, containing instructions and data– a processing unit, for performing arithmetic and logical operations– a control unit, for interpreting instructions

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

2von Neumann Model

Abstraction of von Neumann

implements a next state function

stores both program instructions and data

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

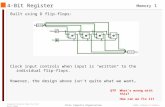

3Memory

•••

0000000100100011010001010110

110111101111

00101101

10100010

2k x m array of stored bits

Address– unique (k-bit) identifier of location

Contents– m-bit value stored in location

Basic Operations

LOAD– read a value from a memory location

STORE– write a value to a memory location

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

4Interface to Memory

How does processing unit get data to/from memory?MAR: Memory Address RegisterMDR: Memory Data Register

To LOAD a location (A):– Write the address (A) into the MAR.– Send a “read” signal to the memory.– Read the data from MDR.

To STORE a value (X) to a location (A):– Write the data (X) to the MDR.– Write the address (A) into the MAR.– Send a “write” signal to the memory.

M EM ORY

M AR M DR

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

5Hardware Level Organization

PC MAR

IR MBR

I/O AR

I/O BREx Unit

CPU

I/O Module

buffers

Main Memory

Instruction

Instruction

Instruction

Data

Data

Data

0

n-1

SystemBus

PC = program counterIR = instruction registerMAR = memory address registerMBR = memory buffer registerI/O AR = I/O address registerI/O BR = I/O buffer register

Major components:

- memory

- central processing unit

- registers

- the fetch/execute cycle

(the hardware process)

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

6Central Processing Unit Control

- decodes instructions and manages CPU’s internal resources

Registers

- general-purpose registers available to user processes

- special-purpose registers directly managed in fetch/execute cycle

- other registers may be reserved for use of operating system

- very fast and expensive (relative to memory)

- hold all operands and results of arithmetic instructions (on RISC systems)

- save bits in instruction representation

Data path or arithmetic/logic unit (ALU)

- operates on data

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

7

memory for data, programs, compilers, editors, etc.

Stored Program Concept

Fetch & Execute CycleInstructions are fetched and put into a special register

Bits in the register "control" the subsequent actions

Fetch the “next” instruction and continue

Instructions are collections of bits

Programs are stored in memory, to be read or written just like data

PC MAR

IR MBR

I/O AR

I/O BREx Unit

CPUMain Memory

Instruction

Instruction

Instruction

Data

Data

Data

0

n-1

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

8

Of course, on most systems several programs will be stored in memory at any given time.

On most contemporary systems instructions of only one of those will be executed at any given instant.

Stored Program Concept

The operating system will rapidly switch among the eligible processes, producing the illusion that several programs are executing at the same time.

PC MAR

IR MBR

I/O AR

I/O BREx Unit

CPUMain Memory

PowerPoint pgm

(machine code)

vim

(machine code)

GIS source code

(data)

g++

(machine code)

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

9Fetch/Execute Cycle

Sometimes called the hardware process… executes continuously.

Steps:

- fetch an instruction from memory to the instruction register

- increment the program counter register (by the instruction length)

- decode the instruction (in the control unit)

- fetch operands, if any, usually from registers

- perform the operation (in the data path); this may modify the PC register

- store the results, usually to registers

Fetch Stage Execute Stage

Fetch Next Instruction

Execute InstructionSTART HALT

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

10Simplified MIPS Datapath

Register File

Memory

Memory

ALU

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

11Finite State Machine

So, where's the FSM?

Input

Next Instruction

Execute Instruction

Current State

Contents of registers and

memory

Output devices

Input devices

CS@VT September 2009 ©2006-09 McQuain, Feng & Ribbens

Intro MIPS

Computer Organization I

12Control Unit State Diagram

Here's a state machine diagram for the MIPS control logic we'll be studying: