International Journal of Pure and Applied Mathematics ... · implementation procedure of an...

Transcript of International Journal of Pure and Applied Mathematics ... · implementation procedure of an...

Abstract—Resonant converters featuring

soft switching are commonly used in

domestic induction heating applications due

to their high efficiency and high power

density. In this paper, the design and

implementation procedure of an improved

efficiency and lowprofile resonant inverter

for induction heating applications is

presented.The proposed converter is based

on a multi-MOSFET cell implementation,

reducing the equivalent on-state resistance

per chip-area. By using automotive-grade

MOSFET devices, a converter capable of

delivering up to 4 kW has been built,

reducing conduction losses against the

classical IGBT-based converter. In addition

to this, the reduced switching times of

MOSFET devices decrease switching losses,

further increasing the conversion efficiency.

The main design challenges including the

device selection, gate drive circuit, and

cooling have been addressed. As a

conclusion, a low-profile implementation

without fan and heat sink is obtained, which

significantly improves state-of-the-art

technology in terms of efficiency and power

density.

1.1 Introduction

Domesticinduction heating (IH) has

become the technology of choice of many

users due to its improved properties in terms

of efficiency, quickness, safety, cleanness,

and accurate power control. Advances in

power electronics, digital control, and

magnetic component design have allowed

designing reliable products with improved

user performance. Unlike classical solutions,

the pot is directly heated by means of a

varying magnetic field in the range of the

kilohertz[1-5], requiring a specific power

electronic converter. The main design

constrains of this converter are derived from

the reduced enclosure, the limited cooling

capabilities, and the high output power

levels, requiring the use of high-efficiency

and high power density converters.

The domestic IH power supply is

composed by two power electronic

converters. First, the mains ac voltage is

filtered to fulfil the electromagnetic

compatibility (EMC) requirements and, after

that, a diode full-bridge rectifier is used to

obtain a high-ripple dc-link voltage. This

POWER DENSITY MULTI-MOSFET-BASED SERIES RESONANT INVERTER FOR INDUCTION

HEATING APPLICATIONS

Dr.S.P.Vijayaragavan

1, Dr.V.Jayalaksnmi

2

Professor 1 2, Department of EEE, BIST, BIHER, Bharath University, Chennai.

International Journal of Pure and Applied MathematicsVolume 119 No. 12 2018, 147-167ISSN: 1314-3395 (on-line version)url: http://www.ijpam.euSpecial Issue ijpam.eu

147

bus is used to supply the inverter stage that

generates the high-frequency accurrent

required for the IH application[6-9]. The

power electronic converter structure is

depicted in Fig. 1(a), where typical

conversion losses, 1-η, are included.

In the past, several inverters with

improved performance have been proposed

for this application field, including improved

control strategies, topologies and

semiconductor technologies[10-15]. As a

consequence of the involved current levels

and the high switching frequencies, the

inverter stage concentrates main amount of

losses, playing an important role in the

development of such systems. Considering

the output power range (2–5 kW) and

switching frequencies (20–100 kHz) typical

of domestic IH, the series-resonant half-

bridge inverter is usually the selected

option[16-19]. Additionally, as a result of

the output power levels and the involved

switching frequencies, insulated-gate bipolar

transistor (IGBT) devices are selected for

this application. In order to achieve high

efficiency, zero voltage switching (ZVS)

during the turn-on transition is obtained at

switching frequencies above the resonant

frequency[20-25]. However, conduction

losses and the power loss during turn-off

transition still lead to a significant power

loss which requires a heat sink and fan to

ensure a proper thermal design.

In this paper, a high-efficiency and

high power density series resonant inverter

is proposed that significantly improves

efficiency and reduces cooling requirements,

obtaining an implementation that does not

require a heat sink and fan. The proposed

converter is based on the half-bridge

topology, where each switching device is

implemented by means of a multi-MOSFET

cell. The series operation of power devices

has been successfully used in the past for

other applications either using IGBTs or

MOSFETs. The main challenges for this

implementation, i.e., [26] cost, driving, and

cooling system, are studied and explained in

this paper. In addition, an analytical model

has been proposed for both the output power

and the converter losses. Based on this

model, an optimized design, capable of

delivering up to 4 kW, has been successfully

implemented to prove the feasibility of the

proposed approach[27-31]. The domestic IH

power supply is composed by two power

electronic converters (see Fig. 1). First, the

mains ac voltage is filtered to fulfill the

electromagnetic compatibility (EMC)

requirements and, after that, a diode full-

bridge rectifier is used to obtain a high-

ripple dc-link voltage[32-36]. This bus is

International Journal of Pure and Applied Mathematics Special Issue

148

used to supply the inverter stage that

generates the high-frequency accurrent

required for the IH application. The power

electronic converter structure is depicted in

Fig. 1(a), where typical conversion losses, 1-

η, are included.

In the past, several inverters with

improved performance have been proposed

for this application field, including improved

control strategies, [9]–[13], topologies [14]–

[19], and semiconductor technologies [20],

[21]. As a consequence of the involved

current levels and the high switching

frequencies, the inverter stage concentrates

main amount of losses, playing an important

role in the development of such systems.

Considering the output power range (2–5

kW) and switching frequencies (20–100

kHz) typical of domestic IH, the series-

resonant half-bridge inverter is usually the

selected option[37-41]. Additionally, as a

result of the output power levels and the

involved switching frequencies, insulated-

gate bipolar transistor (IGBT) devices are

selected for this application. In order to

achieve high efficiency, zero voltage

switching (ZVS) during the turn-on

transition is obtained at switching

frequencies above the resonant frequency

[22]. However, conduction losses and the

power loss during turn-off transition still

lead to a significant power loss which

requires a heat sink and fan to ensure a

proper thermal design.

In this paper, a high-efficiency and

high power density seriesresonant inverter is

proposed that significantly improves

efficiency and reduces cooling requirements,

obtaining an implementation that does not

require a heat sink and fan. The proposed

converter is based on the half-bridge

topology, where each switching device is

implemented by means of a multi-MOSFET

cell [23]. The series operation of power

devices has been successfully used in the

past for other applications either using

IGBTs [24]–[27] or MOSFETs [27]–[31].

The main challenges for this

implementation, i.e., cost, driving, and

cooling system, are studied and explained in

this paper[42-45]. In addition, an analytical

model has been proposed for both the output

power and the converter losses. Based on

this model, an optimized design, capable of

delivering up to 4 kW, has been successfully

implemented to prove the feasibility of the

proposed approach. The remainder of this

paper is organized as follows. Section II

presents the proposed multi-MOSFET cell

series-resonant inverter, including its

operation and optimized gate drive circuit.

Section III presents the main design

International Journal of Pure and Applied Mathematics Special Issue

149

procedure and key simulation results,

including an electrical and thermal analysis.

The proposed converter operation is

experimentally verified in Section IV,

including a comparative evaluation against

the classical implementation. Finally, the

conclusions of this paper are drawn in

Section IV.

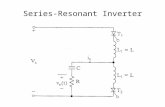

II. MULTI-MOSFET-BASED SERIES

RESONANT INVERTER

A. Proposed Converter

Considering the specific constrains

imposed by the application, i.e., high

operation temperature and reduced cooling

capabilities, IGBT devices are usually

selected. One of the main disadvantages of

the IGBT devices arises from its large

switching times, i.e., the collector current

tail due to minority carriers that causes the

turn-off speed to be slow. This behavior has

a significant impact in the converter

performance, not only because of the

efficiency penalty caused by the increased

switching losses, but also due to the

increased magnetic component size due to

the restricted switching frequency. In order

to overcome these limitations, MOSFET

devices offer reduced switching times and

reduced on-state resistance. Nevertheless,

the required device area for the same current

is higher, increasing the final cost. In

addition to this, the on-state resistance

variation with the temperature significantly

degrades the efficiency. In spite of this, in

the low-voltage range (<100 V), the power

MOSFET devices are a feasible option

because of their reduced on-state losses and

high current capabilities, even if a high-

temperature operation is considered.

It consists of EMC filter, bridge

rectifier, PFC boost converter, multi

MOSFET series resonant inverter, switched

capacitor network and induction coils act as

loads. EMC filter means combination of

passive elements to minimize the noise

International Journal of Pure and Applied Mathematics Special Issue

150

which is produced by diode rectifier. Here

rectifier is used to convert ac-dc conversion

and then it convert into high frequency ac

signal. Here boost converter is used to

perform PFC in AC side. This method PFC

is called active PFC.Here multi-MOSFET

half bridge inverter is to perform switching

operation at high frequency such as 100

KHz. In addition to this series resonant

circuit are used to perform soft switching

operation and to achieve high power density

.In addition to this switched capacitor

networks are used to achieve high power

density operation.

As a result, according to the

theoretical limit presented in (2),it is

possible to improve the on-state

performance of the converter using the same

chip areawith the proposed series

arrangement. Thus, since α > 2 in the case

of Si vertical NMOS, the MOSFET

serialization ideally leads to a conduction

loss reduction depending on the number of

serialized devices, N. Ideally, in the case of

600-V applications, a 40-V 15-MOSFET

stack achieves an on resistance reduction up

to five times, significantly reducing

conduction losses with the same total silicon

area. Besides, the resultant distributed

cooling is more efficient, allowing removing

the heat sink and fan. As a consequence, a

high power density and low-profile

implementation is obtained. In order to

obtain a cost-effective solution, automotive

grade MOSFETS, M1,M2 . . . MN , are

used. The series operation ofpower devices

has been successfully used in the past for

other applications, mainly for high-voltage

generators (10–100 kV), either using IGBTs

[24]–[26] or MOSFETs [28]–[31].

Nonetheless, themain disadvantage of the

previously proposed solutions (see Fig. 3)

arises from the difficulties to ensure the

correct series device activation, i.e., to

ensure the proper voltage distribution in

each device. In this paper, a simple active

activation circuit is proposed. Unlike

classical solutions based on isolated dc–dc

converters or pulse transformers [24], [26],

[29], the proposed activation circuit is

composed of a few discrete components,

resulting in a cost-effective solution

specially designed for the ZVS behavior of

the converter. As a result, the series stack of

low-voltage MOSFETs can be operated as

an equivalent switching device [see Fig.

3(b)]. The next section presents the

International Journal of Pure and Applied Mathematics Special Issue

151

proposed converter operation analysis,

followed by a power loss analysis in

Section II-C, and a detailed

explanation of the proposed activation

circuit will be provided in Section II-

D.

B. Converter Analysis

The converter analysis is performed

regardless the device properties, i.e.,

assuming ideal components. Once the

converter is analyzed, the effect of the

switching devices in the efficiency will be

analyzed. The complete converter schematic

is composed of a diode full-bridge rectifier

and a half-bridge inverter (see Fig.

4).Considering that the operating

frequencies of the rectifier and the inverter

are separated enough, i.e., the rectifier stage

operates at mains frequency, fac = 1/Tac ,

whereas the multi-MOSFET inverter stage

operation frequency, fsw = 1/Tsw, is set

higher than 20 kHz to avoid acoustic noise,

the converter analysis can be performed

independently. 1) Rectifier Stage: As it has

been previously explained, a small dc-link

capacitor, Cb , is selected to ensure an input

power factor close to one for the worse

operation point, i.e., at the minimum output

power. As a result of this, the dc-link

voltage has a big sinusoidal ripple.

Consequently, the rectifier diodes DA,H and

International Journal of Pure and Applied Mathematics Special Issue

152

DB,L conducts during the positive mains

half-cycles whereas DB,H and DA,L

conduct during the negative ones, resulting a

dc-link voltage waveform, vb

2) Multi-MOSFET Based Half-

Bridge Series Resonant Inverter:

The inverter stage is composed of

two equivalent switching devices, SH , SL ,

composed of N low-voltage MOSFET

transistors,MH,1 toMH,N , andML,1

toML,N , respectively. In addition, a lossless

snubber capacitor, Csnb, is included in

parallel with each MOSFET to reduce the

turn-off switching losses. The series RLC

resonant tank is composed of the equivalent

IH load, modeled as a series resistor, Req ,

and inductance, Leq , and the resonant

capacitor, Cr , split into two capacitors to

reduce the EMC filter requirements. The

main waveforms of the converter are

depicted in Fig. 5, where the load current

flows through the different devices, and the

snubber capacitors has been highlighted.

The dead-timebetween the upper and the

lower activation signals, GH ,GL ,

respectively, is denoted as tDT, whereas the

required time to charge/discharge the

snubber capacitor has been denoted as tsnb.

In order to reduce the control complexity

and ensure symmetric power loss

distribution in the power devices, a 50%

duty cycle is assumed, resulting in a square

wave (SW) control. Switching frequencies

higher than the resonant frequency are used

to ensure the ZVS soft-switching behavior.

Depending on the load current, io , and the

devices activation, eight different states (I to

International Journal of Pure and Applied Mathematics Special Issue

153

VIII) are defined, summarized in Fig. 6.

During states I and V, the load current flows

through the snubber capacitors, resulting in

a reduced dv/dt waveform during the turn-

off transition. As a result, the switching

losses during the turn-off transition are

reduced. Once the snubber capacitors are

fully charged/discharged, the load current

flows through the antiparallel diodes of

theMOSFET devices (States II, VI, for SH

and SL , respectively). It is important to note

that, in order to reduce conduction losses,

theMOSFET devices are activated to

conduct the negative current through the

device channel (States III, VII), resulting in

a synchronous rectification. Finally, during

States IV, VIII, the positive load current

flows through the MOSFET devices.

The equivalent inverter is supplied

by the output voltage of the rectifier stage,

Vb , where

fac fsw is

assumed. By the use of the Fourier harmonic

analysis [33], the output power, Po , results

where h is the harmonic number, Zo

is the impedance of the series RLC resonant

tank, and Vo is the output voltage of the

inverter. The harmonic peak voltage results

By rewriting the previous expression, the

output power expression results

C. Power Loss Analysis

Efficiency is a key design parameter of the

proposed converter and, consequently, a

detailed power loss analysis is performed in

this section. Assuming lossless passive

components, the power losses are mainly

concentrated in the switching devices. As a

result of this, two loss terms can be

considered, conduction losses and switching

losses, both in the rectifier and in the

equivalent inverter stage.

1) Rectifier Stage:

Due to the reduced operating frequency of

the rectifier, fac , the switching losses in the

rectifier can be neglected and this analysis

will focus in the conduction losses term. The

mains current, iac , flows through two

International Journal of Pure and Applied Mathematics Special Issue

154

rectifier diodes simultaneously, depending

on the mains sign. As a result, the average,

ID,avg , and rms, ID,rms , current values

through the rectifier diodes results

By defining as Von,D,Ron,D , the on-state

voltage drop and the on-state resistance of

the rectifier diodes, respectively, the rectifier

stage conduction losses, Pon,D , results

2) Multi-MOSFET-Based Half-Bridge

Series Resonant Inverter:

a) Conduction losses:

Starting with the conduction losses, by

neglecting the snubber charge/discharge

times,

tsnb Tsw , the

instantaneous current waveform, id , through

the MOSFET switching devices, can be

expressed as

respectively, for the upper and the lower

series devices.

where a constant on-state voltage drop,

Von,S , and on-state resistance, Ron,S , is

assumed. It is important to note that a

synchronous rectification is assumed to

reduce conduction losses. As a result, the

device conducts both if the current is

positive or negative, allowing to model the

on-state losses by using the equivalent on-

state resistance, Ron,S , regardless of the

current sign. In addition to this, the

equivalent switching device is composed by

N series low-voltage MOSFET devices,

resulting inRon,S = NRon,1 , where Ron,1

denotes the on-state resistance of a single

low-voltage MOSFET device. The

equivalent switching device rms current,

International Journal of Pure and Applied Mathematics Special Issue

155

It is important to note that due to the ZVS

operation, the turn-on losses can be

neglected. In addition, considering the series

multi-MOSFET approach, the current

through each lowvoltage device is ideally

the same, it,1 = it , whereas the voltage

stress is reduced by N-times, vt,1 = vt /N.

As a result, the total switching losses in each

device, Psw,1 , resultsthus, the total amount

of losses remains constant and equally

distributed in each series device, Psw,1=

Psw /N, making reasonable to consider an

equivalent switching device for the

switching losses analysis. The average

switching losses pswTsw in a switching

period can be defined as a function of the

turn-off energy losses, eOFF,HTsw ,

eOFF,LTsw , for the upper and lower

equivalent switching devices, respectively.

D. Proposed Activation Circuit

One of the main challenges when designing

the multi-MOSFET inverter is the design of

a reliable and cost-effective gate drive

circuit. In the past, several solutions have

been proposed using capacitive coupling

[28], [30], [31], pulse transformers [25],

[26], or optical fiber [29] using isolated dc–

dcconverters. In this paper, a specific

activation circuit, specially designed for the

multi-MOSFET operation considering the

ZVS behavior is proposed to ensure the

correct devices activation in a cost-effective

way. It is composed of a Zener diode, Dz, a

low-voltage PMOS, and a fast diode, Db .

As a result of this,the series combination of

low-MOSFET devices operates as an

equivalent transistor. The activation circuit

is described in Fig. 7. When the activation

signals, GH and GL for the upper and the

lower series MOSFET, respectively, are

turned-on (States III, VII) the equivalent

gate-to-source capacitance of the MOSFET

devices is sequentially charged via the series

diode [see Fig. 7(a)]. Considering the higher

switching devices, firstMH,N is activated.

Then,MH,N−1 is activated via the current

International Journal of Pure and Applied Mathematics Special Issue

156

path composed by Db,H,N−1 − Dz,H,N−1 −

Rg,H,N−1 and the channel of the MH,N

MOSFET. The same occurs until all the

devices are sequentially activated. It is

important to note that a sequential activation

sequence can be performed during this

transition because the negative load current

is flowing through the antiparallel diodes

until the devices are activated. During the

turn-off transition, all the series devices

must be deactivated simultaneously. In this

transition, the negative voltage,

typically−5V, applied by the driver stage

polarizes (reverse biased) the

ZenerdiodesDz . Consequently, the

breakdown voltage of the Zener diodes, vz ,

activates the PMOS, short-circuiting the

gate-to-source capacitance of the power

MOSFET. As a result of this, all the devices

are simultaneously turned OFF [see Fig.

7(b)]. At this point, it is important to note

that depending onthe parasitic capacitance

of the diode, Db , and the Zener diode, Dz ,

a parallel capacitance, Cb , can be added to

ensure the Zener activation during the turn-

off transition. A good criterion for its

selection consists on selecting ten times the

output capacitance of the Zener diode.

Finally, during the off-states, i.e., states

VIII, IV, for the upper and lower switching

devices, respectively, the series diode Db

blocks the blocking voltage of the devices.

One of the most challenging aspects of this

converter is to ensure the proper voltage

distribution in each low-voltage MOSFET,

which may be unbalanced due to phase lag

in the activation or circuit asymmetries.

However, considering the ZVS operation

mode and the effect of the snubber

capacitor, smooth voltage waveforms are

obtained, enabling a better voltage

distribution in the power devices. The effect

of the phase lag between devices activation,

φ, in the devices voltage unbalance is

depicted in Fig. 8. More in detail, the effect

of both positive and negative phase lag are

detailed in Fig. 9. As it is shown, a negative

phase lag (early device activation) causes an

overvoltage in the device. However, since

the equivalent snubber capacitance is

increased N-times while the other devices

are inactivated, i.e., the equivalent snubber

capacitor is Csnb, instead of Csnb/N, that

results in a reduced voltage slope. As a

consequence, a positive effect is obtained by

the use of a discrete low-voltage sparse

snubber network instead of a high-voltage

capacitor. On the other hand, considering a

positive phase-lag the same situation occurs,

resulting in a reduced voltage in the device.

The simulated results quantifying the effect

of the phase lag into the voltage unbalance

are plotted in Fig. 10 for different snubber

capacitors, Csnb. As it is shown, higher

snubber capacitances reduce the voltage

unbalance in the switching devices.

Nonetheless, the proposed activation circuit

achieves a phase lag constrained to a

maximum of |φ| ≤ 11 ns. For this lag value,

and considering a 330-nF snubber capacitor,

the effect of the voltage unbalance can be

neglected.

International Journal of Pure and Applied Mathematics Special Issue

157

neglected.single

The aim of this section is to apply the

previously obtained analytical results to

propose a design procedure, and to apply it

to design a power converter with the same

specifications as the reference design, i.e.,

the same output power range. The main

design specifications are summarized in

Table I, whereas the design flowchart is

shown in Fig. 11. Considering a fixed mains

voltage, Vac,rms = 230 V, and assuming a

maximum output power, Po,max = 3.6 kW

at the resonant point, the maximum IH

heating equivalent series resistor can be

calculated using the first-harmonic approach

as follows: Req< 2V 2 ac,rms π2Po,max

(27) leading to a maximum load resistance

value of 2.98 Ω. As a consequence, it has

been selected to be Req = 2.85 Ω. The IH

quality factor, QIH , depends on the inductor

design, i.e., external diameter, internal

diameter, and turns number. For the selected

IH load, QIH = 1.32, the series inductance

obtained is Leq = 29.6 μH. The maximum

output power is achieved at the resonant-

load natural frequency, which will be the

minimum operating switching frequency to

ensure ZVS operation mode. As a

consequence, the resonant capacitor results

1687 nF, being Cr = 1440 nF, the final

chosen value. As a result, the minimum

switching frequency is slightly increased,

being close to24 kHz. The resultant output

power variation as a function of the

switching frequency is depicted in Fig. 12.

International Journal of Pure and Applied Mathematics Special Issue

158

A. Optimum Devices Selection

This section is focused on the low-voltage

MOSFET selection in order to maximize the

efficiency of the inverter stage.The first step

consists on analyzing the effect of the

package in the final performance.

Considering the voltage and current

operation ranges, the packages commonly

available can be divided into two groups:

packages featuring classical bonding

connection (wire-bonding) and packages

using direct clipping (clip-packing). One of

the advantages of the direct clipping

connection is its increased connection area,

which minimizes both the parasitic

resistance and the package inductance. In

addition to this, the manufacturing process

results simplified, reducing the final device

cost. The effect of the device package in the

parasitic series resistance is quantified in

Fig. 13 for classical low-voltage MOSFETs.

It can be seen that the parasitic resistance is

in the milliohm range, which is comparable

to the low-voltage device on-state resistance

and, as a consequence, it results critical in

this application. The right-side devices, i.e.,

DPAK, TO-220 and D2PAK feature wire-

bonding connections, whereas the left-side

devices (LFPAK, CANPAK, and

DIRECTFET) use a direct-clipping method,

resulting in a reduced parasitic resistance.

As a consequence, the LFPAK package has

been selected and will beboard (PCB). Once

the LFPAK package has been selected, the

next step is to select the device that

maximizes the converter efficiency. As it

has been previously explained, due to the

reduced switching times of the MOSFET

devices, the main losses are caused by the

conduction term. Besides, according to (2),

the equivalent on-state resistance for the

same blocking voltage is reduced if the

number of series devices, N, is increased.

Nonetheless, the effect of the parasitic case

resistance leads to an optimum device

number, where the ratio of the on-state

resistance divided bythe maximum blocking

voltage [mΩ/kV] is minimized. As it is

shown in Fig. 14, considering only the

LFPAK package, the best series device

number results Nopt = 16, which

corresponds to a 30-V device (PSMN1R0),

where a 150% voltage safety margin has

been considered. B. Thermal Design Once

the device is selected, the power losses can

be calculated considering the design

restrictions. Beginning with the conduction

losses, the equivalent on-state resistance

results Ron,S = Nopt ·Ron,1 = 16·1.1 mΩ =

17.6 mΩ at Tj = 90 ◦C. Using (19),

22.2Wmaximum total conduction converter

losses are obtained. Then, in order to

calculate the switching losses, a current fall

time of tf = 37 ns is considered whereas the

equivalent snubber capacitance is Csnb =

20.6 nF (16 series 330-nF capacitors). As a

result, the switching losses obtained using

(26) allows to neglect them in the complete

operation range (<50 mW for the complete

converter). When the power losses are

determined, the next step is to compute the

required PCB area to dissipate the losses

(see Fig. 15). From the previous analysis, it

is clear that the maximum power losses in

the worst-case situation are 0.7 W per

device. Considering an ambient temperature

of Tamb = 90 ◦C, and a maximum junction

temperature of 150 ◦C, the required

maximum thermal resistance results 85.71

◦C/W. In order to design the required PCB

International Journal of Pure and Applied Mathematics Special Issue

159

to dissipate the power losses, finite-element

model (FEM) analyses have been performed

for different PCB sizes and number of

layers. The thermal resistance as a function

of the PCB area is shown in Fig. 15(b). As a

result, APCB = 500 mm2 has been

selected,obtaining an equivalent thermal

resistance of 39 ◦C/W by using a two-layer

design (see Fig. 16). As a result, the

maximum device temperature is ensured to

be below 125 ◦C.

Mode 1:

During positive half cycle and ON state of

the MOSFET in the boost circuit the flow is

shown in the diagram below, in this state the

inductor in the boost will get charged. At

that time itself the capacitor connected to the

boost converter will start to discharge. By

which the series resonant converter will get

a flow. The direction of the series resonant

circuit will be explained in mode 2.

Mode 2:

As explained above the flow of the boost

converter in the on state i.e. the MOSFET in

the boost converter is in ON state for the

previous mode. In this mode the MOSFET is

in OFF state, in this stage the inductor in the

will start to discharge. Due to this step the

voltage level will be increased to Vin+ Vl,

then the capacitor gets charged. Then during

the positive half cycle of the series resonant

converter the flow will from the upper half

i.e. MH1, MH2 and MH3 of the converter

then to the load. The switching capacitor

will get charged when its switch is opened

and the power will be flown through the

load. When the switch is closed the

capacitors will start to discharge.

Mode 3:

In this mode the negative half cycle of the

rectifier and the boost converter is been

explained. As explained above in the mode 1

the flow remains same but the direction of

the rectifier is changed because the mode 1

explained the positive half cycle. The circuit

power flow of the series resonant converter

will be explained in the mode 4.

International Journal of Pure and Applied Mathematics Special Issue

160

Mode 4:

In mode also we going to discuss about the

negative half cycle. In this mode the

inductor present in the boost circuit will start

to discharge due to the switch is been

opened at that time the voltage level is

increased to Vin+ Vl, then the capacitor

between the boost circuit and the series

converter gets charged. In the converter

section the flow is flown through the

negative detection i.e. the flow is through

the lower series switch ML1, ML2 and

ML3. Then the switching capacitor will get

charged when its switch is opened and the

power will be flown through the load. When

the switch is closed the capacitors will start

to discharge.

Simulation

International Journal of Pure and Applied Mathematics Special Issue

161

Conclusion:

In this paper, a novel approach based on the

series operation of low-voltage MOSFET

has been successfully proposed. By using

International Journal of Pure and Applied Mathematics Special Issue

162

low-voltage MOSFET devices, an

implementation capable of delivering up to 4

kW without fan and heat sink is achieved for

the domestic IH application. In addition to

this, the reduced switching times of

MOSFET devices decrease switching losses,

further increasing the conversion efficiency,

which reaches levels up to 98%, whereas the

maximum efficiency level in th classical

converter is 94.9%. A specific cost-effective

driver circuit has been proposed to correctly

activate each series devices. It has been

specifically designedto achieve good

performances considering the ZVS

operationmode of this resonant converter in

a cost-effective way Additionally, a detailed

analytical model has been introduced both

for the output power and the converter

losses, enabling an optimized design based

on the electrical model and the thermal

FEManalysis. Finally, a comparative

evaluation discussion, concerning the

classical high-voltage devices

implementation and the proposed low-

voltage series MOSFET approach, has been

carried out. As a conclusion, the proposed

complete and reliable design has been

proposed significantly improving the

performance of conventional IH designs.

REFERENCES

1. Nimal, R.J.G.R., Hussain, J.H.,

Effect of deep cryogenic treatment

on EN24 steel, International Journal

of Pure and Applied Mathematics,

V-116, I-17 Special Issue, PP-113-

116, 2017

2. Parameswari, D., Khanaa, V.,

Deploying lamport clocks and linked

lists, International Journal of

Pharmacy and Technology, V-8, I-3,

PP-17039-17044, 2016

3. Parameswari, D., Khanaa, V., Case

for massive multiplayer online role-

playing games, International Journal

of Pharmacy and Technology, V-8,

I-3, PP-17404-17409, 2016

4. Parameswari, D., Khanaa, V.,

Deconstructing model checking with

hueddot, International Journal of

Pharmacy and Technology, V-8, I-3,

PP-17370-17375, 2016

5. Parameswari, D., Khanaa, V., The

effect of self-learning epistemologies

on theory, International Journal of

Pharmacy and Technology, V-8, I-3,

PP-17314-17320, 2016

6. Pavithra, J., Peter, M.,

GowthamAashirwad, K., A study on

business process in IT and systems

through extranet, International

Journal of Pure and Applied

Mathematics, V-116, I-19 Special

Issue, PP-571-576, 2017

7. Pavithra, J., Ramamoorthy, R.,

Satyapira Das, S., A report on

evaluating the effectiveness of

working capital management in

googolsoft technologies, Chennai,

International Journal of Pure and

Applied Mathematics, V-116, I-14

Special Issue, PP-129-132, 2017

8. Pavithra, J., Thooyamani, K.P., A

cram on consumer behaviour on

International Journal of Pure and Applied Mathematics Special Issue

163

Mahindra two wheelers in Chennai,

International Journal of Pure and

Applied Mathematics, V-116, I-18

Special Issue, PP-55-57, 2017

9. Pavithra, J., Thooyamani, K.P.,

Dkhar, K., A study on the air freight

customer satisfaction, International

Journal of Pure and Applied

Mathematics, V-116, I-14 Special

Issue, PP-179-184, 2017

10. Pavithra, J., Thooyamani, K.P.,

Dkhar, K., A study on the working

capital management of TVS credit

services limited, International

Journal of Pure and Applied

Mathematics, V-116, I-14 Special

Issue, PP-185-187, 2017

11. Pavithra, J., Thooyamani, K.P.,

Dkhar, K., A study on the analysis of

financial performance with reference

to Jeppiaar Cements Pvt Ltd,

International Journal of Pure and

Applied Mathematics, V-116, I-14

Special Issue, PP-189-194, 2017

12. Peter, M., Dayakar, P., Gupta, C., A

study on employee motivation at

Banalari World Cars Pvt Ltd

Shillong, International Journal of

Pure and Applied Mathematics, V-

116, I-18 Special Issue, PP-291-294,

2017

13. Peter, M., Kausalya, R., A study on

capital budgeting with reference to

signware technologies, International

Journal of Pure and Applied

Mathematics, V-116, I-18 Special

Issue, PP-71-74, 2017

14. Peter, M., Kausalya, R., Akash, R.,

A study on career development with

reference to premheerasurgicals,

International Journal of Pure and

Applied Mathematics, V-116, I-14

Special Issue, PP-415-420, 2017

15. Peter, M., Kausalya, R., Mohanta, S.,

A study on awareness about the cost

reduction and elimination of waste

among employees in life line

multispeciality hospital, International

Journal of Pure and Applied

Mathematics, V-116, I-14 Special

Issue, PP-287-293, 2017

16. Peter, M., Srinivasan, V., Vignesh,

A., A study on working capital

management at deccan Finance Pvt

Limited Chennai, International

Journal of Pure and Applied

Mathematics, V-116, I-14 Special

Issue, PP-255-260, 2017

17. Peter, M., Thooyamani, K.P.,

Srinivasan, V., A study on

performance of the commodity

market based on technicalanalysis,

International Journal of Pure and

Applied Mathematics, V-116, I-18

Special Issue, PP-99-103, 2017

18. Philomina, S., Karthik, B., Wi-Fi

energy meter implementation using

embedded linux in ARM 9, Middle -

East Journal of Scientific Research,

V-20, I-12, PP-2434-2438, 2014

19. Philomina, S., Subbulakshmi, K.,

Efficient wireless message transfer

system, International Journal of Pure

and Applied Mathematics, V-116, I-

20 Special Issue, PP-289-293, 2017

20. Philomina, S., Subbulakshmi, K.,

Ignition system for vechiles on the

basis of GSM, International Journal

of Pure and Applied Mathematics,

V-116, I-20 Special Issue, PP-283-

286, 2017

21. Philomina, S., Subbulakshmi, K.,

Avoidance of fire accident by

wireless sensor network,

International Journal of Pure and

International Journal of Pure and Applied Mathematics Special Issue

164

Applied Mathematics, V-116, I-20

Special Issue, PP-295-299, 2017

22. Pothumani, S., Anuradha, C.,

Monitoring android mobiles in an

industry, International Journal of

Pure and Applied Mathematics, V-

116, I-20 Special Issue, PP-537-540,

2017

23. Pothumani, S., Anuradha, C., Decoy

method on various environments - A

survey, International Journal of Pure

and Applied Mathematics, V-116, I-

10 Special Issue, PP-197-199, 2017

24. Pothumani, S., Anuradha, C., Priya,

N., Study on apple iCloud,

International Journal of Pure and

Applied Mathematics, V-116, I-8

Special Issue, PP-389-391, 2017

25. Pothumani, S., Hameed Hussain, J.,

A novel economic framework for

cloud and grid computing,

International Journal of Pure and

Applied Mathematics, V-116, I-13

Special Issue, PP-5-8, 2017

26. Pothumani, S., Hameed Hussain, J.,

A novel method to manage network

requirements, International Journal

of Pure and Applied Mathematics,

V-116, I-13 Special Issue, PP-9-15,

2017

27. Pradeep, R., Vikram, C.J.,

Naveenchandra, P., Experimental

evaluation and finite element

analysis of composite leaf spring for

automotive vehicle, Middle - East

Journal of Scientific Research, V-12,

I-12, PP-1750-1753, 2012

28. Prakash, S., Jayalakshmi, V., Power

quality improvement using matrix

converter, International Journal of

Pure and Applied Mathematics, V-

116, I-19 Special Issue, PP-95-98,

2017

29. Prakash, S., Jayalakshmi, V., Power

quality analysis & power

system study in high voltage

systems, International Journal of

Pure and Applied Mathematics, V-

116, I-19 Special Issue, PP-47-52,

2017

30. Prakash, S., Sherine, S., Control of

BLDC motor powered electric

vehicle using indirect vector control

and sliding mode observer,

International Journal of Pure and

Applied Mathematics, V-116, I-19

Special Issue, PP-295-299, 2017

31. Prakesh, S., Sherine, S., Forecasting

methodologies of solar resource and

PV power for smart grid energy

management, International Journal of

Pure and Applied Mathematics, V-

116, I-18 Special Issue, PP-313-317,

2017

32. Prasanna, D., Arulselvi, S.,

Decoupling smalltalk from rpcs in

access points, International Journal

of Pure and Applied Mathematics,

V-116, I-16 Special Issue, PP-1-4,

2017

33. Prasanna, D., Arulselvi, S.,

Exploring gigabit switches and

journaling file systems, International

Journal of Pure and Applied

Mathematics, V-116, I-16 Special

Issue, PP-13-17, 2017

34. Prasanna, D., Arulselvi, S.,

Collaborative configurations for

wireless sensor networks systems,

International Journal of Pure and

Applied Mathematics, V-116, I-15

Special Issue, PP-577-581, 2017

35. Priya, N., Anuradha, C., Kavitha, R.,

Li-Fi science transmission of

knowledge by way of light,

International Journal of Pure and

International Journal of Pure and Applied Mathematics Special Issue

165

Applied Mathematics, V-116, I-9

Special Issue, PP-285-290, 2017

36. Priya, N., Pothumani, S., Kavitha,

R., Merging of e-commerce and e-

market-a novel approach,

International Journal of Pure and

Applied Mathematics, V-116, I-9

Special Issue, PP-313-316, 2017

37. Raj, R.M., Karthik, B., Effective

demining based on statistical

modeling for detecting thermal

infrared, International Journal of

Pure and Applied Mathematics, V-

116, I-20 Special Issue, PP-273-276,

2017

38. Raj, R.M., Karthik, B., Energy sag

mitigation for chopper, International

Journal of Pure and Applied

Mathematics, V-116, I-20 Special

Issue, PP-267-270, 2017

39. Raj, R.M., Karthik, B., Efficient

survey in CDMA system on the basis

of error revealing, International

Journal of Pure and Applied

Mathematics, V-116, I-20 Special

Issue, PP-279-281, 2017

40. Rajasulochana, P., Krishnamoorthy,

P., Ramesh Babu, P., Datta, R.,

Innovative business modeling

towards sustainable E-Health

applications, International Journal of

Pharmacy and Technology, V-4, I-4,

PP-4898-4904, 2012

41. Rama, A., Nalini, C., Shanthi, E., An

iris based authentication system by

eye localization, International

Journal of Pharmacy and

Technology, V-8, I-4, PP-23973-

23980, 2016

42. Rama, A., Nalini, C., Shanthi, E.,

Effective collaborative target

tracking in wireless sensor networks,

International Journal of Pharmacy

and Technology, V-8, I-4, PP-23981-

23986, 2016

43. Ramamoorthy, R., Kanagasabai, V.,

Irshad Khan, S., Budget and

budgetary control, International

Journal of Pure and Applied

Mathematics, V-116, I-20 Special

Issue, PP-189-191, 2017

44. Ramamoorthy, R., Kanagasabai, V.,

Jivandan, S., A study on training and

development process at Vantec

Logistics India Pvt Ltd, International

Journal of Pure and Applied

Mathematics, V-116, I-14 Special

Issue, PP-201-207, 2017.

45. Pradeep, R., Vikram, C.J.,

Naveenchandran, P., Experimental

evaluation and finite element

analysis of composite leaf spring for

automotive vehicle, Middle - East

Journal of Scientific Research, V-17,

I-12, PP-1760-1763, 2013

International Journal of Pure and Applied Mathematics Special Issue

166