Global Muon Trigger (Vienna)

description

Transcript of Global Muon Trigger (Vienna)

Global Trigger, Global Trigger, Global Muon TriggerGlobal Muon TriggerH. Bergauer, L. Boldizsar, A. Jeitler, P. Hidas, K. H. Bergauer, L. Boldizsar, A. Jeitler, P. Hidas, K.

Kastner, Kastner, S. Kostner, N. Neumeister, M. Padrta, P. Porth, H. S. Kostner, N. Neumeister, M. Padrta, P. Porth, H. Rohringer, H. Sakulin, J. Strauss, A. Taurok, C.-E. Rohringer, H. Sakulin, J. Strauss, A. Taurok, C.-E.

WulzWulz

Annual ReviewCERN, 13 Sep 2002

presented by

Claudia-Elisabeth WulzClaudia-Elisabeth Wulz

C.-E. Wulz 2 Annual Review, Sep. 2002

Global Muon Trigger (Vienna)

Solution with 1 logic board

C.-E. Wulz 3 Annual Review, Sep. 2002

GMT Logic FPGA

C.-E. Wulz 4 Annual Review, Sep. 2002

Main Findings of CMS Internal Note 2002/024 GMT: DT/CSC cancel-out unit

• old solution:– cancel-out at DT and

CSC track finder level– confirmation by RPC in

Global Muon Trigger– maximum over-all

efficiency is limited to the one of the RPC

• new solution:– duplication allowed at

track finder level– DT/CSC cancel-out unit

in GMT– ghosts are reduced

independent of RPC more robust

– some (tolerable) ghosting remains

C.-E. Wulz 5 Annual Review, Sep. 2002

Single muon trigger efficiency vs

(*)efficiency to find muon of any pT in flat pT sample

ORCA_6_2_2 || < 2.1

C.-E. Wulz 6 Annual Review, Sep. 2002

L1 single muon trigger rates

C.-E. Wulz 7 Annual Review, Sep. 2002

L1 single & di-muon trigger rates

20, 6;6W =82.3 %Z =99.6 %Bs= 9.9 %

25, 5;5W =74.1 %Z =99.5 %Bs=14.3 %

12, 8;8W =91.4 %Z =99.7 %Bs=14.5 %

14, -;-W =89.6 %Z =99.8 %Bs=27.1 %

L = 1034cm-2s-1L = 2x1033cm-2s-1ORCA_6_2_2working points compatible with current L1 pT binning

|| < 2.1Trigger rates in kHz 100 kHz DAQ 8 kHz for

50 kHz DAQ4 kHz for

C.-E. Wulz 8 Annual Review, Sep. 2002

GMT Status and Plans

Recent progress Logic design completed

• detailed design document & drawings Functionality improved

• added provision for Beam Halo Trigger during normal operation Documentation

• DT/CSC cancel-out unit improved performance in barrel/endcap overlap regionCMS Note 2002/024: H.Sakulin, “A Robust Solution to the Ghosting Problems of the CMS Level-1 Muon Trigger in the Barrel/Endcap Overlap Region”

Plans for 2002/2003– continue VHDL simulation of FPGA chips– VHDL simulation of GMT board– Synthesis / design of FPGAs

C.-E. Wulz 9 Annual Review, Sep. 2002

GMT Milestones

Milestone Dec. 2001: Logic design done -> Done

Milestone Dec. 2002: FPGA design done -> Delayed to Dec. 2003

Milestone Dec. 2003: VME board production done -> Delayed to June 2004

Milestone June 2004: VME board tested (GMT ready) -> Delayed to Oct. 2004

Milestone Jan. 2005: GMT integration tests done -> Planned on time

C.-E. Wulz 10 Annual Review, Sep. 2002

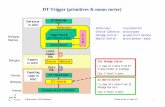

Global Trigger (Vienna)

PSB (Pipeline Synchronizing Buffer) Input synchronization (7 boards including GMT) GTL (Global Trigger Logic) Logic calculation (1-2 boards)FDL (Final Decision Logic) L1A decision (1 board)TCS (Trigger Control System Modeule) Central Trigger Control (1 board)NEW: L1A (Level-1 Accept Module) Delivery of L1A (1 board)TIM (Timing Board) Timing (1 board)GTFE (Global Trigger Frontend) Readout (1 board)

FromDetector

To TTC

Backplane andReadout links

PSB GTL FDL TCS L1A

ToDAQ

GTFE

FromTTC

TIM

FromPartitions

ToEVM

C.-E. Wulz 11 Annual Review, Sep. 2002

New layout of Global Trigger 9U Crate

C.-E. Wulz 12 Annual Review, Sep. 2002

Global Trigger Logic Prototype Board GTL-6U

• GTL-6U

Automatic chip design and setup procedure developed. Layout for a 20 channel GTL (4 , 4 isol. e/, 4 central jets, 4 fwd jets, ET, ET

miss, 8 jet multiplicities; other quadruplets can be connected alternatively for tests) has been finished! 1020-pin Altera FPGA 20k400E not yet included.

The layout of a conversion board to be used later in final 9U-crate is ready. It contains also memories in FPGA’s to send simulated test data to the GTL-6U board.

A decision on a redefinition of jet input groups has been taken. It was decided to keep the present best 4 central jets, 4 forward jets and 4 -jets and jet multiplicities for different ET thresholds. A new quantity HT giving the transverse energy sum of all good jets above threshold has been added. The exact definition of how to calculate the jet multiplicities (-range) still has to be taken at the level of the calorimeter trigger. More than 8 values could be necessary.

C.-E. Wulz 13 Annual Review, Sep. 2002

Global Trigger Logic Board GTL-9U

New: HT

C.-E. Wulz 14 Annual Review, Sep. 2002

GT Conversion Board

C.-E. Wulz 15 Annual Review, Sep. 2002

GTL-6U Prototype Schematics

Design simplified,board available by June 2003

C.-E. Wulz 16 Annual Review, Sep. 2002

Final Decision Logic FDL-9U

FPGA design has started. Board available by June 2003.

Monitoring of all algorithm and L1A bits

Prescaling of all algorithms

Trigger Mask

8 L1A’s in parallel for partition modes

Input of up to 64 technical trigger bits from PSB possible

C.-E. Wulz 17 Annual Review, Sep. 2002

FDL-9U

C.-E. Wulz 18 Annual Review, Sep. 2002

Timing Board TIM-6U

• TIM-6U

The board contains a TTCrx chip and provides all timing signals for the GT crate. It will also be used in the Drift Tube Track Finder crates.

An FPGA provides all necessary test functions to run the crate without the central TTC clock. It simulates also L1A requests for monitoring or to test the readout chain.

The schematic design is finished. The layout is in progress, decided to go ahead as planned with mezzanine TTCrx solution.

The final Timing Board will be 6U (previously 9U) and is expected for June 2003.

C.-E. Wulz 19 Annual Review, Sep. 2002

TIM-6U

C.-E. Wulz 20 Annual Review, Sep. 2002

Central Trigger Control System Board TCS-9U

• TCS-9U Its functions and the input / output cables are defined. Design of schematics and the TCS chip is in progress. The board is expected by April 2003. Trigger Partitions: The maximum number of subsystems is fixed (32).An almost final agreement about the output to the DAQ Event Manager has been reached.The input format of Fast Signals is fixed. 4 coded bits per subsystem, sent as LVDS parallel data, and RJ45 connectors are proposed. The TCS board provides data for the ”TTCci” (new CMS-TTCvi). A L1A driver module to be used with the TTCci has been conceived.

C.-E. Wulz 21 Annual Review, Sep. 2002

TCS within Global Trigger

New: 8 DAQ partitions(asynchronous TTS)

C.-E. Wulz 22 Annual Review, Sep. 2002

TCS board schematics

TCS monitoring chip

Clk,L1A,BC0...to 8 emulatorsTCS_fastsigs to 8DAQ_part

VME

L1A,BGo...to TTCci

TCS chip

Clock PLL

C.-E. Wulz 23 Annual Review, Sep. 2002

Begin of event BOR Identifier // Begin of record 32 bits

Trigger number Nr of all L1A sent since begin of run (8h with 100kHz =ABA9 5000hex) 32 bits

DAQ partition number 3 bits (30..28) , + Trigger Type 4bits (19..16),

+ Bunch crossing number 12 bits (11..0) 32 bits

Subdetector partitions // bit nn=1 Subd.-part. nn is connected to this DAQ-partition. 32 bits

Event Number // since last ‚Reset Event Counter‘; 28 bits (27-0) **) 32 bits

Orbit number // since last ‚Reset Orbit Counter‘; (29 bits=13.5h) **) 32 bits

Algo bits_0 Physics trigger algorithm bits 0...31 32 bits

Algo bits_1 Physics trigger algorithm bits 32...63 32 bits

Algo bits_2 Physics trigger algorithm bits 64...95 32 bits

Algo bits_3 Physics trigger algorithm bits 96...127 32 bits

Algo bits_4 reserved for optional upgrade 32 bits

Algo bits_5 reserved for optional upgrade 32 bits

Technical trigger bits bits 31...0 //also used for external test trigger signals 32 bits

End of Event EOR Identifier // End of record 32 bits

Data sources in Global Trigger crate:FDL = Final Decision boardTCS = Central Trigger Control board

PreliminaryVersion 28 Aug 2002

Note:GPS time in EVMrecord also foreseen

Subdetector partitions are combined in groups connected to a DAQ partition.

Only 1 DAQ partition triggers at a time due to DAQ restrictions.

The same trigger type is valid for all members (=subdetector partitions) of this DAQ-partition.* )

*) Therefore TCS does not send a (redundant) dedicated trigger type for each subdetector partition.

**) Reset Event/Orbit Counter can be sent at different times to each single DAQ-partition.

Preliminary GT event record for Event ManagerF

DL

TC

S

C.-E. Wulz 24 Annual Review, Sep. 2002

Global Trigger Setup Program Environment

Task of GT Setup Program:1) Configure chips

- via VME, JTAG (or from PROM) 2) Load registers, LUTs, memories

- via VME

Remarks:- For standard datataking, the trigger menu,setup of logic and thresholds from database (e.g. .xml) files, which are converted to HW format by custom or HAL device drivers.- For testing configuration files can also be loaded directly with Altera/Xilinx (e.g.MasterBlaster/ByteBlaster) hardware. - Run Control interfacing to be done.- JTAG programming not yet explored

BackplaneGlobal TriggerSetup Program

Database.sof, .pof.bit.xml.rbf, .bit, .rbt.vhd.vhd.sof, .pofHAL.rbf

C.-E. Wulz 25 Annual Review, Sep. 2002

Setup for GT Logic Configuration

GT

L-C

onve

rsio

n C

ard

VM

E-M

XI-

2

MXI Cable

VME Crate

Linux PC running XDAQequipped with PCI-MXI Card

VME-MXI-2 Crate Controller

VME-Bus

Thanks to J. Gutleber for help with XDAQ!

C.-E. Wulz 26 Annual Review, Sep. 2002

Crate for Global Trigger Tests

GTL Conversion Board

PSB-6U

VME MXI-2 Crate Controller

C.-E. Wulz 27 Annual Review, Sep. 2002

Global Trigger MilestonesGlobal Trigger Milestones

Oct. 2002 (orig. March 2002): System Test -> Delayed to June 2003•This includes the backplane-6U, the PSB-6U, GTL-6U, FDL-9U and TIM-6U. The GTFE and the GMT are not included. Oct. 2002: Backplane-9U tested -> Delayed to March 2003Oct. 2002 (orig. July 2002): TCS-9U tested -> Delayed to April 2003June 2003: GTFE-9U tested -> Delayed to Dec. 2003Dec. 2003: 20-channel Global Trigger tested -> Delayed to June 2004Milestone Dec. 2003: GMT ready -> Delayed to Jun. 2004July 2004: 12-channel PSB-9U availableNov. 2004: Complete 32-channel Global Trigger available•Includes GTL-9U module with all input channels (4 , 4 isol. e/, 4 non-isol. e/ , 12 jet channels, HT , ET, ET

miss, jet multiplicities).

C.-E. Wulz 28 Annual Review, Sep. 2002

Global Trigger Status Sept. 2002Global Trigger Status Sept. 2002

• Custom Backplane for VME 9U crate 6U Prototype: Channel Links ...exists MS 3/02*

– 9U Backplane: 80MHz GTLp and Channel Links, ...design in progress MS 10/02 03/03

• PSB Input board (synchronisation, monitoring) 6 channel 6U Prototype: Channel Link receivers ... board tested MS 3/02*

– 12 channel board: memories inside FPGAs ...conceptual design MS 7/04

• GTL Logic board: Conversion board for prototype ...board tested MS 3/02*

– GTL6U prototype: 20 channels ...layout done MS 3/02* 06/03

• 4, 4ie/, 4 cjets, 4 fjets, ETT,mET, 8 nr_of jets

• other quadruplets can be connected alternatively for tests

– GTL9U board: 32 channels ...conceptual design MS 11/04

• 4, 4ie/, 4e/, 4 cjets, 4 fjets, 4 tau_jets,ETT,mET, HT, nrs_of jets

• TIM Timing board ...layout in progress MS 3/02 06/03

– 6U size, TTCrx, clock and L1A distribution, also used by DTTF

• FDL-9U Final Decision board ...design in progress MS 3/02 06/03

• TCS-9U Central Trigger Control board ...design in progress MS 7/02 04/03

• GTFE-9U Readout board ...conceptual design MS 6/03 12/03

• *) Milestone (MS) Mar-02: All prototype boards except GTFE+GMT.

C.-E. Wulz 29 Annual Review, Sep. 2002

Progress since 2001Progress since 2001

• GTL-6U board: layout done

• GTL Conversion board: produced and tested

• Test program written in CVI with GUI

• Configuration program implemented using XDAQ.

• TIM board: FPGA and board design done, layout in progress

• TCS board:

• Final definition of functions and IO-signals done,

• Schematic and FPGA design in progress

• FDL board:

• Final definition of functions and IO-signals done,

• Schematic and FPGA design in progress

• Definition of requirements for the GT setup program in progress

C.-E. Wulz 30 Annual Review, Sep. 2002

ConclusionsGlobal Muon Trigger

Single board design for barrel and forward muons

Solution for overlap region with DT/CSC cancel-out unit in GMT

FPGA design startedGlobal Trigger

New processor crate layout, GTL layout finished, other boards well advanced, work on software requirements and solutions started

Trigger Control System

Interfaces to subsystems including Event Manager and partition handling definedThis talk can be found at:

http://wwwhephy.oeaw.ac.at/p3w/cms/trigger/globalTrigger/trans/

wulz_AnnRev_sep2002.ppt

• Detailed information about the Global Trigger and the Global Muon Trigger is available on the HEPHY Vienna web sites:

• http://wwwhephy.oeaw.ac.at/p3w/cms/trigger/globalTrigger

• http://wwwhephy.oeaw.ac.at/p3w/cms/trigger/globalMuonTrigger