GATE ARRAY S1L50000 SERIES DESIGN GUIDE - Epson · 6.7.3 Gate Count Estimation ... CMOS process...

Transcript of GATE ARRAY S1L50000 SERIES DESIGN GUIDE - Epson · 6.7.3 Gate Count Estimation ... CMOS process...

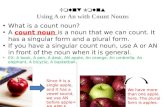

NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency. All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2007, All rights reserved.

The information of the product number change Starting April 1, 2001 the product number will be changed as listed below. To order from April 1, 2001 please use the new product number. For further information, please contact Epson sales representative.

Configuration of product number

• DEVICES S1 L 60843 F 00A0 00

*1 : Model name

K Standard Cell L Gate Array X Embedded Array

*2 : Shape

B Assembled on board, COB, BGA

M Plastic SOP

C Plastic DIP R TAB-QFP D Bare Chip T Tape Carrier (TAB) F Plastic QFP 2 TSOP (Standard Bent) H Ceramic DIP 3 TSOP (Reverse Bent) L Ceramic QFP

Comparison table between new and previous number

Previous number New Number Previous number New Number SLA50000H series S1L50000 series SLA525TH S1L52503 SLA5028H S1L50282 SLA525QH S1L52504 SLA502TH S1L50283 SLA5335H S1L53352 SLA502QH S1L50284 SLA533TH S1L53353

− S1L50552 SLA533QH S1L53354 − S1L50553 SLA5442H S1L54422 − S1L50554 SLA544TH S1L54423

SLA5075H S1L50752 SLA544QH S1L54424 SLA507TH S1L50753 SLA5506H S1L55062 SLA507QH S1L50754 SLA550TH S1L55063 SLA5099H S1L50992 SLA550QH S1L55064 SLA509TH S1L50993 SLA5668H S1L56682 SLA509QH S1L50994 SLA566TH S1L56683 SLA5125H S1L51252 SLA566QH S1L56684 SLA512TH S1L51253 SLA5815H S1L58152 SLA512QH S1L51254 SLA581TH S1L58153 SLA5177H S1L51772 SLA581QH S1L58154 SLA517TH S1L51773 SLA517QH S1L51774 SLA5250H S1L52502

Packing specifications Specifications Shape (*2)

Model number

Model name (*1)

Product classification (S1:Semiconductors)

Table of Contents

GATE ARRAY S1L50000 SERIES EPSON i DESIGN GUIDE

S1L50000 SERIES Table of Contents

Chapter 1 Overview ..................................................................................................................................... 1

1.1 Features........................................................................................................................................... 1 1.2 Master Lineup ................................................................................................................................. 2 1.3 Electrical Characteristics and Specifications .................................................................................. 3 1.4 Outline of Gate Array Development Flow.................................................................................... 10

Chapter 2 Gate Count Estimation and Master Selection............................................................................ 12 2.1 Circuit Partitioning........................................................................................................................ 12 2.2 Gate Count Estimation.................................................................................................................. 12 2.3 IO Pin Count Estimation............................................................................................................... 12 2.4 Master Selection............................................................................................................................ 12 2.5 Estimation of Usable BC Count for the Circuit with RAM .......................................................... 13

Chapter 3 Design Restrictions and Limitations ......................................................................................... 14 3.1 Basic Design Techniques .............................................................................................................. 14

3.1.1 Insertion of IO buffers........................................................................................................... 14 3.1.2 Avoid Excessive Fanout........................................................................................................ 14 3.1.3 Wired logic is prohibited....................................................................................................... 15 3.1.4 Synchronous Design Techniques .......................................................................................... 15

3.2 Differentiating Circuits are Prohibited.......................................................................................... 16 3.3 Clock Tree Synthesis..................................................................................................................... 17

3.3.1 Outline .................................................................................................................................. 17 3.3.2 Design Flow.......................................................................................................................... 18 3.3.3 How to implement................................................................................................................. 19 3.3.4 Constraints and notes .......................................................................................................... 20 3.3.5 Clock Tree Synthesis Check Sheet........................................................................................ 22 3.3.6 Reference .............................................................................................................................. 23

3.4 Designing High-Speed Circuits .................................................................................................... 27 3.5 Metastable ..................................................................................................................................... 28 3.6 Internal Bus Configuration............................................................................................................ 29 3.7 Avoid Contention with External Bus ............................................................................................ 31 3.8 Solution for Hazards ..................................................................................................................... 32 3.9 Oscillator Circuits ......................................................................................................................... 32

3.9.1 Oscillator circuit configurations.......................................................................................... 32 3.9.2 Notes when using oscillator circuits ..................................................................................... 33

3.10 Constraints on Verilog-HDL/VHDL Netlists ............................................................................ 35 3.10.1 Constraints on Verilog-HDL/VHDL netlists ..................................................................... 35 3.10.2 Constraints on Verilog netlists .............................................................................................. 36 3.10.3 Constraints on VHDL netlists ............................................................................................... 37 3.10.4 About descriptions of oscillator cells and AC/DC test circuit cell (TCIR2) ......................... 37 3.10.5 About descriptions of clock root buffers............................................................................... 38

Chapter 4 Types of I/O Buffers and Notes on Use..................................................................................... 40 4.1 Types of I/O Buffers ..................................................................................................................... 40

4.1.1 Selection of I/O buffers......................................................................................................... 40 4.1.2 Bus Hold Circuit ................................................................................................................... 41

4.2 I/O Buffers for Single Power Supply Operation ........................................................................... 41 4.2.1 Input Buffers ......................................................................................................................... 41 4.2.2 Output Buffers....................................................................................................................... 43 4.2.3 Bi-Directional Buffers........................................................................................................... 46 4.2.4 Fail-Safe Cells....................................................................................................................... 49 4.2.5 Gated Cells............................................................................................................................ 52

4.3 I/O Buffers for Dual Power Supply Operation.............................................................................. 55 4.3.1 Input Buffers ......................................................................................................................... 55 4.3.2. Output Buffers....................................................................................................................... 58 4.3.3 Bi-Directional Buffers........................................................................................................... 64

Table of Contents

ii EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

4.3.4 Fail-Safe Cell .........................................................................................................................71 4.3.5 Gated Cells.............................................................................................................................72

4.4 Notes on the Use of Dual Power Supplies .....................................................................................74 4.4.1 To Implement Dual Power Supply Designs...........................................................................74 4.4.2 Power Supply for Dual Power Supply Designs .....................................................................74 4.4.3 Power On-Off Sequence ........................................................................................................74

Chapter 5 RAM ..........................................................................................................................................75 5.1 Features..........................................................................................................................................75 5.2 Word-bit Configurations and Simulation Models ..........................................................................75 5.3 RAM Size Estimation ....................................................................................................................76 5.4 Embeddable RAM Size .................................................................................................................77 5.5 Function Examples ........................................................................................................................78 5.6 Delay Parameters ...........................................................................................................................81 5.7 Timing Chart..................................................................................................................................97 5.8 Access to Invalid Addresses ..........................................................................................................99

Chapter 6 Design for Testability...............................................................................................................100 6.1 Circuit Initialization.....................................................................................................................100 6.2 Shortening the Test Patterns.........................................................................................................100 6.3 Special Test Circuit Provisions for AC and DC Tests..................................................................100

6.3.1 Test Circuit Configuration ...................................................................................................101 6.4 Test Circuit for Memory Blocks ..................................................................................................108

6.4.1 Test Patterns for RAM Blocks .............................................................................................108 6.5 Test Circuit for Function Cells.....................................................................................................111

6.5.1 Test Circuit Configuration ...................................................................................................111 6.5.2 Test Patterns.........................................................................................................................111 6.5.3 Test Circuit Information.......................................................................................................111

6.6 Scan Design .................................................................................................................................112 6.6.1 Scan Circuit .........................................................................................................................112 6.6.2 Scan Design Flow................................................................................................................112 6.6.3 Design Rules........................................................................................................................114

6.7 Boundary Scan Design ................................................................................................................123 6.7.1 Boundary Scan Design Flow ...............................................................................................123 6.7.2 Instructions ..........................................................................................................................124 6.7.3 Gate Count Estimation.........................................................................................................124 6.7.4 Design Rules........................................................................................................................124

Chapter 7 Propagation Delay and Timing.................................................................................................129 7.1 Relationship between Ta and Tj...................................................................................................129 7.2 Calculation of Propagation Delay................................................................................................129 7.3 Input Capacitance Load (Load A)................................................................................................132 7.4 Wire Capacitance Load (Load B) ................................................................................................133 7.5 Estimation of Propagation Delay Time........................................................................................133 7.6 Output Buffer Delay Estimation ..................................................................................................135 7.7 Setup and Hold Time for Flip-Flops ............................................................................................135

Chapter 8 Test Pattern Generation ............................................................................................................138 8.1 Testability Considerations............................................................................................................138 8.2 Usable Waveforms.......................................................................................................................138 8.3 Constraints on Test Patterns.........................................................................................................139

8.3.1 Test Rate and Event Count...................................................................................................139 8.3.2 Input Delay ..........................................................................................................................139 8.3.3 Pulse Width..........................................................................................................................139 8.3.4 Input Waveform Format.......................................................................................................139 8.3.5 Strobe...................................................................................................................................139

8.4 Notes on DC Test.........................................................................................................................140 8.5 Notes When Using Oscillator Circuit ..........................................................................................142 8.6 AC Test ........................................................................................................................................143

8.6.1 Constraints on Test Events...................................................................................................143 8.6.2 Constraints on AC Test Points .............................................................................................143

Table of Contents

GATE ARRAY S1L50000 SERIES EPSON iii DESIGN GUIDE

8.6.3 Constraints on Test Path Delay ........................................................................................... 143 8.6.4 Other Constraints ................................................................................................................ 143

8.7 Constraints on Test Patterns of Bi-directional Pin ...................................................................... 143 8.8 Notes on High-Impedance State.................................................................................................. 144

Chapter 9 Calculating Total Power Consumption.................................................................................... 145 9.1 Calculating Power Consumption ................................................................................................ 145

9.1.1 Internal Cell (Pint) .............................................................................................................. 145 9.1.2 Input Buffers (Pi) ................................................................................................................ 146 9.1.3 Output Buffers (Po)............................................................................................................. 146 9.1.4 Low Power Cells................................................................................................................. 147 9.1.5 Low Noise Cells.................................................................................................................. 147

9.2 Limit on Power Consumption ..................................................................................................... 148 Chapter 10 Pinout and Simultaneous Output Switching.......................................................................... 150

10.1 Estimating Power Supply Pin Count........................................................................................... 150 10.2 Simultaneous Switching and Power Supply Addition................................................................. 152 10.3 Notes on Pinout........................................................................................................................... 154

10.3.1 Power Supply Pins in Fixed Locations ............................................................................... 154 10.3.2 Notes on Pinout................................................................................................................... 154 10.3.3 Recommended Pinout ......................................................................................................... 159

Appendix A1 Input/Output Buffer Characteristic Graphs........................................................................ 161 A1.1 5.0-V operation ........................................................................................................................... 161 A1.2 3.3-V operation ........................................................................................................................... 170 A1.3 2.0-V operation ........................................................................................................................... 179

Chapter 1 Overview

GATE ARRAY S1L50000 SERIES EPSON 1 DESIGN GUIDE

Chapter 1 Overview The S1L50000 Series gate arrays featuring high speed and high integration are fabricated on a 0.35um CMOS process with “sea-of-gates” architecture.

1.1 Features • Maximum gate count 815,468 (2-input NAND gates)

• Operating speed Internal logic gates: 140ps (3.3V, typical conditions), 210ps (2.0V, typical conditions) (2-input power NAND, F/O = 2, typical wire load capacitance and conditions)

Input buffers: 380ps (5.0V, typical conditions) using level shifter 400ps (3.3V, typical conditions), 1.30ns (2.0V, typical conditions) (F/O = 2, typical wire load capacitance and conditions)

Output buffers: 2.12ns (5.0V, typical conditions) using level shifter 2.02ns (3.3V, typical conditions), 3.90ns (2.0V, typical conditions) (CL = 15pF, typical conditions)

• Process 0.35um, 2-, 3-, and 4-layer aluminum interconnect

• I/F levels IO TTL, COMS, and LVTTL compatible

• Input modes TTL, CMOS, LVTTL, TTL Schmitt, CMOS Schmitt, LVTTL Schmitt, PCI, and fail-safe inputs With built-in pull-up and pull-down resistors (Each resistor has two resistance values)

• Output modes Normal, 3-state, bi-directional, PCI, and fail-safe outputs

• Output drive IOL = 0.1, 1, 3, 8, 12, 24mA selectable (when using 5.0V level shifter) IOL = 0.1, 1, 2, 6, 12mA selectable (at 3.3V) IOL = 0.05, 0.3, 0.6, 2, 4mA selectable (at 2.0V)

• RAM 1-port asynchronous, 2-port asynchronous

• Dual power supply operation by built-in level shifter Internal logic: Low voltage I/O buffers: High and low voltages mixed

Chapter 1 Overview

2 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

1.2 Master Lineup The following 14 masters are available for the S1L50000 Series:

Table 1-1 Master Lineup

BC Count Cell Utilization U: (%)*2 Masters Total BC

Count *1 PAD

Count Row Column 2-LM 3-LM 4-LM

S1L50062/50063/50064 5760 48 144 40 50 88 95

S1L50122/50123/50124 11948 56/64 206 58 50 88 95

S1L50282/50283/50284 28710 88/104 319 90 50 88 95

S1L50552/50553/50554 55500 124/144 444 125 47 85 95

S1L50752/50753/50754 75774 144/168 519 146 47 85 95

S1L50992/50993/50994 99198 168/192 594 167 47 85 95

S1L51252/51253/51254 125772 188/216 669 188 45 80 95

S1L51772/51773/51774 177062 224 794 223 45 75 95

S1L52502/52503/52504 250160 264 944 265 45 75 95

S1L53352/53353/53354 335858 308 1094 307 43 75 95

S1L54422/54423/54424 442112 352 1256 352 40 70 90

S1L55062/55063/55064 506688 376 1344 377 40 70 90

S1L56682/56683/56684 668552 432 1544 433 40 70 90

S1L58152/58153/58154 815468 480 1706 478 40 70 90

Notes: *1 : Add about 350 BCs to the estimation for the recommended test circuit. *2 : Values shown here are utilization when RAM and other macro cells are not embedded.

Since utilization is dependent not only on logic size, but also on the numbers of signal lines and nodes per signal, these values can be used only as reference.

Chapter 1 Overview

GATE ARRAY S1L50000 SERIES EPSON 3 DESIGN GUIDE

1.3 Electrical Characteristics and Specifications

Table 1-2 Absolute Maximum Ratings (Single power supply) (VSS = 0 V)

Parameter Symbol Limit Unit

Power Supply Voltage VDD -0.3 to +4.0 V

Input Voltage VI -0.3 to VDD+0.5*1 V

Output Voltage VO -0.3 to VDD+0.5*1 V

Output Current/Pin IOUT ±30 mA

Storage Temperature Tstg -65 to +150 °C

Note: *1: For N-channel open drain bi-directional buffers, input buffers prefixed with IDC and IDH, and fail-safe cells, the allowable voltage range is –0.3 to +7.0V.

Table 1-3 Absolute Maximum Ratings (Dual power supplies) (VSS = 0 V)

Parameter Symbol Limit Unit

HVDD*3 -0.3 to +7.0 V

Power Supply Voltage LVDD

*3 -0.3 to +4.0 V

HVI -0.3 to HVDD+0.5*1 V Input Voltage

LVI -0.3 to LVDD+0.5*1 V

HVO -0.3 to HVDD+0.5*1 V Output Voltage

LVO -0.3 to LVDD+0.5*1 V

Output Current/Pin IOUT ±30 (±50*2) mA

Storage Temperature Tstg -65 to +150 °C

Notes: *1 : For N-channel open drain bi-directional buffers, input buffers prefixed with LIDC, LIDH, HIDC and HIDH, and fail-safe cells, the allowable voltage range is –0.3 to +7.0V.

*2 : Applicable to buffers with 24mA output current *3: HVDD≥LVDD must be met.

Chapter 1 Overview

4 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

Table 1-4 Recommended Operating Conditions (for single power supply operation with VDD = 3.3V)

(VSS = 0 V)

Parameter Symbol Min. Typ. Max. Unit

Power Supply Voltage VDD 3.00 3.30 3.60 V

Input Voltage VI -0.3 - VDD+0.3*1 V

0 25 70*2 Ambient Temperature Ta

-40 25 85*3 °C

Normal Input Rising Time*4 tri - - 50 ns

Normal Input Falling Time*4 tfa - - 50 ns

Schmitt Input Rising Time*4 tri - - 5 ms

Schmitt Input Falling Time*4 tfa - - 5 ms

Notes: *1 : For N-channel open drain bi-directional buffers, input buffers prefixed with IDC and IDH, and fail-safe cells, the limit voltage is 5.55V or 5.80V.

*2: Temperature range recommended when Tj = 0 to +85°C *3: Temperature range recommended when Tj = -40 to +125°C *4: Period during which power supply voltage changes by 10 to 90%

Table 1-5 Recommended Operating Conditions (for single power supply operation with VDD = 2.0V)

(VSS = 0 V)

Parameter Symbol Min. Typ. Max. Unit

Power Supply Voltage VDD 1.80 2.00 2.20 V

Input Voltage VI -0.3 - VDD+0.3*1 V

0 25 70*2 Ambient Temperature Ta

-40 25 85*3 °C

Normal Input Rising Time *4 tri - - 100 ns

Normal Input Falling Time *4 tfa - - 100 ns

Schmitt Input Rising Time *4 tri - - 10 ms

Schmitt Input Falling Time *4 tfa - - 10 ms

Notes: *1 : For N-channel open drain bi-directional buffers, input buffers prefixed with IDC and IDH, and fail-safe cells, the allowable voltage range is 5.55V or 5.80V.

*2: Temperature range recommended when Tj = 0 to +85°C *3: Temperature range recommended when Tj = -40 to +125°C *4: Period during which the power supply voltage changes by 10 to 90%

Chapter 1 Overview

GATE ARRAY S1L50000 SERIES EPSON 5 DESIGN GUIDE

Table 1-6 Recommended Operating Conditions (for dual power supply operation) (VSS = 0 V)

Parameter Symbol Min. Typ. Max. Unit

Power Supply Voltage (High) HVDD 4.75 4.50

5.00 5.00

5.25 5.50 V

Power Supply Voltage (Low) LVDD 3.00 3.30 3.60 V

HVI -0.3 - HVDD+0.3*1 V Input Voltage

LVI -0.3 - LVDD+0.3*1 V

Ambient Temperature Ta 0 -40

25 25

70*2 85*3 °C

Normal Input Rising Time*4 tri - - 50 ns

Normal Input Falling Time*4 tfa - - 50 ns

Shumitt Input Rising Time*4 tri - - 5 ms

Shumitt Input Falling Time*4 tfa - - 5 ms

Notes: *1 : For N-channel open drain bi-directional buffers, input buffers prefixed with LIDC and LIDH, and fail-safe cells, the limit voltage is 5.55V or 5.80V.

*2: Temperature range recommended when Tj = 0 to +85°C *3: Temperature range recommended when Tj = -40 to +125°C *4: Period during which the power supply voltage changes by 10 to 90%

Table 1-7 Recommended Operating Conditions (for dual-power supply operation) (VSS = 0 V)

Item Symbol Min. Typ. Max. Unit

Power Supply Voltage (High Voltage) HVDD 3.00 3.30 3.60 V

Power Supply Voltage (Low Voltage) LVDD 1.80 2.00 2.20 V

HVI -0.3 HVDD+0.3*1 V Input Voltage

LVI -0.3 LVDD+0.3*1 V

Ambient Temperature Ta 0 -40

25 25

70*2 85*3 °C

Htri 50 Normal Input Rising Time *4

Ltfa 100 ns

Htri 50 Normal Input Falling Time *4

Ltfa 100 ns

Htri 5 Schmitt Input Rising Time *4

Ltfa 10 ms

Htri 5 Schmitt Input Falling Time *4

Ltfa 10 ms

Notes: *1 : For N-channel open drain bi-directional buffers, input buffers prefixed with LIDC, LIDH, HIDC, and HIDH, and fail-safe cells, the limit voltage is 5.55V or 5.80V.

*2: Temperature range recommended when Tj = 0 to +85°C *3: Temperature range recommended when Tj = -40 to +125°C *4: Period during which the power supply voltage changes by 10 to 90%

Chapter 1 Overview

6 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

Table 1-8 Electrical Characteristics (HVDD = 5V, VSS = 0V, Ta = -40 to +85°C)

Parameter Symbol Conditions Min. Typ. Max. UnitInput Leakage Current ILI - -1 - 1 µA Off State Leakage Current IOZ - -1 - 1 µA

High Level Output Voltage VOH

IOH = -0.1mA(Type S), -1mA(Type M)-3mA (Type 1), -8mA (Type 2) -12mA (Type 3, Type 4)

HVDD = Min.

HVDD-0.4 - - V

Low Level Output Voltage VOL

IOL = 0.1mA (Type S),1mA (Type M) 3mA (Type 1), 8mA (Type 2) 12mA (Type 3), 24mA (Type 4)

HVDD = Min.

- - 0.4 V

High Level Input Voltage VIH1 CMOS level, HVDD = Max. 3.5 - HVDD +0.3 V

Low Level Input Voltage VIL1 CMOS level, HVDD = Min. -0.3 - 1.0 V High Level Input Voltage VT1+ CMOS Schmitt 2.0 - 4.0 V Low Level Input Voltage VT1- CMOS Schmitt 0.8 - 3.1 V Hysteresis Voltage ∆V CMOS Schmitt 0.3 - - V

High Level Input Voltage VIH2 TTL level, HVDD = Max. 2.0 - HVDD +0.3 V

Low Level Input Voltage VIL2 TTL level, HVDD = Min. -0.3 - 0.8 V High Level Input Voltage VT2+ TTL Schmitt 1.2 - 2.4 V Low Level Input Voltage VT2- TTL Schmitt 0.6 - 1.8 V Hysteresis Voltage VH2 TTL Schmitt 0.1 - - V

High Level Input Voltage*2 VIH3 PCI level, HVDD = Max. 2.0 - HVDD +0.3 V

Low Level Input Voltage*2 VIL3 PCI level, HVDD = Min. -0.3 - 0.8 V

Type 1 30 60 (120)*1 144 kΩ

Pull-Up Resistor PPU VI = 0V Type 2 60 120 (240)*1

288 kΩ

Type 1 30 60 (120)*1 144 kΩ

Pull-Down Resistor PPD VI = HVDD

Type 2 60 120 (240)*1 288 kΩ

High Level Output Current*2 IOH3

PCI VOH = 1.4V, HVDD = Min.

VOH = 3.1V, HVDD = Max.

-44 -

- -

- -142 mA

Low Level Output Current*2 IOL3

PCI VOL = 2.20V, HVDD = Min. VOL = 0.71V, HVDD = Max.

95 -

- -

- 206 mA

High Level Bus Hold Current IBHH

Bus hold VIN = 2.0V HVDD = Min.

- - -80 µA

Low Level Bus Hold Current IBHL

Bus hold VIN = 0.8V HVDD = Min.

- - 33 µA

High Level Overdrive Current IBHHO To flip bus hold VIN = 0.8V

HVDD = Max. -550 - - µA

Low Level Overdrive Current IBHLO To flip bus hold VIN = 2.0V

HVDD = Max. 330 - - µA

Input Pin Capacitance CI f = 1MHz, HVDD = 0V - - 10 pF Output Pin Capacitance CO f = 1MHz, HVDD = 0V - - 10 pF IO Pin Capacitance CIO f = 1MHz, HVDD = 0V - - 10 pF

Notes: *1 : Values in parentheses are applicable when Ta = 0 to +70°C *2: Compliant with the PCI standard Rev. 2.2

Chapter 1 Overview

GATE ARRAY S1L50000 SERIES EPSON 7 DESIGN GUIDE

Table 1-9 Electrical Characteristics (VDD = 3.3 V ± 0.3 V, VSS = 0 V, Ta = -40 to 85°C)

Item Symbol Conditions Min. Typ. Max. UnitInput Leakage Current ILI ― -1 1 µA Off State Leakage Current IOZ ― -1 1 µA

High Level Output Voltage VOH IOH = -0.1mA (Type S), -1mA (Type M)

-2mA (Type 1), -6mA (Type 2) -12mA (Type 3)

VDD = Min.

VDD -0.4 V

Low Level Output Voltage VOL IOL = 0.1mA (Type S), 1mA (Type M)

2mA (Type 1), 6mA (Type 2) 12mA (Type 3)

VDD = Min.

0.4 V

High Level Input Voltage VIH1 LVTTL Level, VDD = Max. 2.0 VDD +0.3

V

Low Level Input Voltage VIL1 LVTTL Level, VDD = Min. -0.3 0.8 V High Level Input Voltage VT1+ LVTTL Schmitt 1.1 2.4 V Low Level Input Voltage VT1- LVTTL Schmitt 0.6 1.8 V

Hysteresis Voltage ∆V LVTTL Schmitt 0.1 V

High Level Input Voltage *2 VIH3 PCI Level, VDD = Max. 1.8 VDD +0.3 V

Low Level Input Voltage *2 VIL3 PCI Level, VDD = Min. -0.3 0.9 V

Type 1 20 50 (100)*1

120 kΩ Pull Up Resistor PPU VI = 0V

Type 2 40 100 (200)*1

240 kΩ

Type 1 20 50 (100)*1

120 kΩ Pull Down Resistor PPD VI = VDD

Type 2 40 100 (200)*1

240 kΩ

High Level Output Current *2 IOH3

PCI VOH = 0.90V, VDD = Min. VOH = 2.52V, VDD = Max.

-36

-115 mA

Low Level Output Current *2 IOL3

PCI VOL = 1.80V, VDD = Min. VOL = 0.65V, VDD = Max.

48

137 mA

High Level Maintenance Current IBHH Bus Hold

VIN = 2.0V, VDD = Min. -20 µA

Low Level Maintenance Current IBHL

Bus Hold VIN = 0.8V, VDD = Min. 17 µA

High Level Reversal Current IBHHO Bus Hold

VIN = 0.8V, VDD = Max. -350 µA

Low Level Reversal Current IBHLO Bus Hold

VIN = 2.0V, VDD = Max. 210 µA

Input Terminal Capacitance CI

f = 1MHz, VDD = 0V 10 pF

Output Terminal Capacitance CO f = 1MHz, VDD = 0V 10 pF

Input/Output Terminal Capacitance CIO f = 1MHz, VDD = 0V 10 pF

Notes: *1 : Values in parentheses are applicable when Ta = 0 to +70°C *2: Compliant with the PCI standard Rev. 2.2

Chapter 1 Overview

8 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

Table 1-10 Electrical Characteristics (VDD or LVDD = 2.0V±0.2V, VSS = 0V, Ta = -40 to +85°C)

Parameter Symbol Conditions Min. Typ. Max. UnitInput Leakage Current ILI - -1 - 1 µA Off State Leakage Current IOZ - -1 - 1 µA

High Level Output Voltage VOH

IOH = -0.05mA(Type S), -0.3mA (Type M)-0.6mA (Type 1), -2mA (Type 2) -4mA (Type 3)

VDD = Min.

VDD-0.2 - - V

Low Level Ouput Voltage VOL

IOL = 0.05mA(Type S), 0.3mA (Type M)0.6mA (Type 1), 2mA (Type 2) 4mA (Type 3)

VDD = Min.

- - 0.2 V

High Level Input Voltage VIH1 CMOS level, VDD = Max. 1.6 - VDD +0.3 V

Low Level Input Voltage VIL1 CMOS level, VDD = Min. -0.3 - 0.3 V High Level Input Voltage VT1+ CMOS Schmitt 0.4 - 1.6 V Low Level Input Voltage VT1- CMOS Schmitt 0.3 - 1.4 V Hysteresis Voltage ∆V CMOS Schmitt 0 - - V

Type 1 30 120 300 kΩ Pull-Up Resistor PPU VI = 0V Type 2 60 240 600 kΩ Type 1 30 120 300 kΩ Pull-Down Resistor PPD VI=VDD Type 2 60 240 600 kΩ

High Level Bus Hold Current IBHH Bus hold VIN = 1.6V

VDD = Min. - - -2 µA

Low Level Bus Hold Current IBHL

Bus hold VIN = 0.3V VDD = Min. - - 2 µA

High Level Overdrive Current IBHHO To flip bus hold VIN = 0.3V

VDD = Max. -100 - - µA

Low Level Overdrive Current IBHLO To fip bus hold VIN = 1.6V

VDD = Max. 100 - - µA

Input Pin Capacitance CI F = 1MHz, VDD = 0V - - 10 pF Output Pin Capacitance CO F = 1MHz, VDD = 0V - - 10 pF IO Pin Capacitance CIO F = 1MHz, VDD = 0V - - 10 pF

Chapter 1 Overview

GATE ARRAY S1L50000 SERIES EPSON 9 DESIGN GUIDE

Table 1-11 Static Current (With single power supply) (Tj = 85°C)

Master 3.3V ± 0.3V IDDS Max.

2.0V ± 0.2V IDDS Max. Unit

S1L50062/50063/50064 S1L50122/50123/50124 5 4 µA

S1L50282/50283/50284 S1L50552/50553/50554 S1L50752/50753/50754 S1L50992/50993/50994

35 31 µA

S1L51252/51253/51254 S1L51772/51773/51774 S1L52502/52503/52504

90 80 µA

S1L53352/53353/53354 S1L54422/54423/54424 S1L55062/55063/55064

170 150 µA

S1L56682/56683/56684 S1L58152/58153/58154 260 230 µA

Table 1-12 Static Current (With dual power supplies) (Tj = 85°C)

Master 5V ± 0.5V HIDDS Max.

3.3V ± 0.3V LIDDS Max.

3.3V ± 0.3V HIDDS Max.

2.0V ± 0.2V LIDDS Max. Unit

S1L50062/50063/50064 S1L50122/50123/50124 11 5 9 4 µA

S1L50282/50283/50284 S1L50552/50553/50554 S1L50752/50753/50754 S1L50992/50993/50994

30 35 25 31 µA

S1L51252/51253/51254 S1L51772/51773/51774 S1L52502/52503/52504

45 90 35 80 µA

S1L53352/53353/53354 S1L54422/54423/54424 S1L55062/55063/55064

65 170 50 150 µA

S1L56682/56683/56684 S1L58152/58153/58154 80 260 60 230 µA

HIDDS: Static current between HVDD and VSS

LIDDS: Static current between LVDD and VSS

Chapter 1 Overview

10 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

Use the following equation to obtain approximate static current when the temperature condition is other than Tj = 85°C. (The equation is applicable only when Tj = -40 to 85°C. When Tj = 125°C, apply temperature coefficient = 12. When Tj = 85°C to 125°C, contact Epson sale representative.)

IDDS = IDDS (Tj = 85°C) × Temperature Coefficient

= IDDS (Tj = 85°C) × 6085

10−Tj

(Example) When VDD = 3.3V±0.3V and Tj = 50°C, the approximate static current of S1L55062 is obtained as follows:

IDDS (Tj = 50°C) = IDDS(Tj = 85°C) × 608550

10−

= 170 × 0.261

= 44.37 (µA)

When the device is operated with dual power supplies, the sum of static currents that flow at voltages used is the total static current (HIDDS + LIDDS).

1.4 Outline of Gate Array Development Flow The customer and Epson work together to develop gate arrays. Using the cell libraries and various design information provided by Epson, the customer designs the system and logic, and creates test patterns. Then the customer is requested to present Epson the data and documents checked against the data release checklist attached in this Design Guide.

Simulation and simulation result analysis are performed by the customer using the EDA software available at the customer’s design site and the EPITS7* offered by Epson. Then Epson takes over the subsequent tasks starting from placement and routing.

* The EPITS7 is Epson specific ASIC library kit that is developed to run on the SUN-Solaris platform.

The EPITS7 currently supports the following EDA software:

• Verilog-XL, NC-Verilog *1

• Design Compiler *2

NOTE: *1 : Verilog-XL and NC-Verilog are registered trademarks of Cadence Design Systems Corporation, USA.

*2 : Design Compiler is a registered trademark of Synopsys Inc., USA.

For more information, contact Epson’s sales representative.

Chapter 1 Overview

GATE ARRAY S1L50000 SERIES EPSON 11 DESIGN GUIDE

The gate array development flow is shown below:

Chapter 2 Gate Count Estimation and Master Selection

12 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

Chapter 2 Gate Count Estimation and Master Selection This chapter describes how to select the right master to implement a given circuit on gate arrays. It discusses how to estimate the gate count of the circuit partitioned from the system designed by the customer. Points that the designer needs to pay attention to when selecting a master are also discussed.

2.1 Circuit Partitioning Care must be taken for the following points when partitioning a circuit from the system designed by the customer and implementing the partitioned circuit on gate arrays.

i. Gate count

ii. IO pin count

iii. Target package

iv. Power consumption

As the circuit size (gate count) increases, the power consumption and IO pin count normally increase. Because of this, partitioning the circuit into multiple chips may sometimes turn out to be more cost effective and power saving than forcibly implementing the circuit on a single chip.

2.2 Gate Count Estimation The circuit size is obtained by counting up all the basic cells (BC) comprising the pre-designed function cells used in the circuit. The BC count of each cell is described in the Gate Array S1L50000 Series MSI Cell Library. To obtain the total BC count of the circuit, refer to the library.

2.3 IO Pin Count Estimation Following the gate count estimation, the IO pin count must be estimated. In doing this, count in test pins for RAM and other macro cells as well as power supply pins. To estimate power supply pin count, refer to Chapter 10, Pinout and Simultaneous Switching Outputs.

2.4 Master Selection Considering the estimated BC count, IO pin count (including power supply pins) and the target package, select the best possible master from Table 1-1, Master Lineup in Chapter 1.

Usable gate count (BCA) for each design is obtained by the following formula using the raw gate count (BCG) of each master and the cell utilization (U) shown in Table 1-1:

BCA = U × BCG

When the design includes RAM cells, refer to the next section and Chapter 5, RAM.

Chapter 2 Gate Count Estimation and Master Selection

GATE ARRAY S1L50000 SERIES EPSON 13 DESIGN GUIDE

2.5 Estimation of Usable BC Count for the Circuit with RAM RAM blocks are extremely large compared to MSI cells, and have fixed sizes in height and width. There are cases where RAM blocks are actually not embeddable, though they appear to fit into the chip with the estimated BC count. Refer to Chapter 5, RAM and check first whether the RAM block is embeddable or not. When target masters are narrowed down, use the following formula to estimate usable BC count for random logic blocks (BCAWR), excluding RAM cell(s):

BCAWR = 0.9 × U × (BCG-BCRAM)

NOTE: The formula stated above may not be applicable in some cases depending on the geometry of random logic area left after the layout of RAM cell(s) regardless of RAM cell count. If the design includes RAM cell(s), contact Epson sales representative for confirmation.

Chapter 3 Design Restrictions and Limitations

14 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

Chapter 3 Design Restrictions and Limitations

3.1 Basic Design Techniques

3.1.1 Insertion of IO buffers

All LSI signals need to be input and output through IO buffers. Be sure to insert either input or output buffer between an external pin and an internal cell. This is because CMOS LSI devices are extremely vulnerable to static electricity and thus they need to be protected by IO buffers integrating a circuit to prevent static electricity.

3.1.2 Avoid Excessive Fanout

In CMOS circuits, as the output load capacitance increases, the signal propagation delay time (tpd) becomes longer together with the rising and falling times of signal waveforms (Tslew).

If the output load capacitance of any one logic gate becomes excessive, signal delays may occur at a specific circuit node. This lowers the operation speed and accuracy in delay simulation, and causes erroneous operations. Because the signal takes longer time to switch, it becomes more susceptible to noise effect.

To avoid excessive load on logic gates in the design phase, limit on connectable load called “fan-out limit” is specified. For each logic gate input pin, the input capacitance relative to the input capacitance of an inverter cell (IN1), called “fan-in” is specified. The fan-out limit is the total number of fan-ins connectable to the output pin of each logic gate. When designing a circuit, make sure that the total fan-ins do not exceed the fan-out of the gate output pin. For logic gate output pins that operate at high speed, such as high-speed clock pins (that operate at 60 MHz or higher), limit the fan-out to about half the normal fan-out value.

The actual load capacitance of a logic gate output pin includes the signal wire capacitance in addition to the input capacitance of the gate connected to the output pin. As the result of running the placement and routing tool, specific nodes may have large load capacitance. The load capacitance of each circuit node can be checked by Tslew output result. If any node capacitance exceeds the specified value, we may ask the customer to modify the circuit to meet the specification. Not to increase the load capacitance after layout, minimize the number of circuit branches from a single node, or use buffers with larger fan-out values.

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 15 DESIGN GUIDE

3.1.3 Wired logic is prohibited

Since CMOS transistors are used for the S1L50000 series, wired logic functions (see Figure 3-1) are prohibited unlike bi-polar transistors. The only permissible method for connecting the outputs of multiple gates is using a bus circuit.

Figure 3-1 Examples of prohibited wired logic

3.1.4 Synchronous Design Techniques

The most fundamental and essential ASIC design guideline is to make sure that all circuits are designed with synchronous logic. In synchronous designs, timings between registers are simple and thus suitable for high-speed circuit designs, a variety of EDA tools, such as those for clock tree synthesis, DFT and STA, are possible to use, and technology independent circuits are easily reusable.

Ideal synchronous circuits meet the following conditions:

1. The timing of all registers in the circuit remains synchronized with one clock.

2. No feedback paths by combinational logic (See Figure 3-2.)

3. No pulse generation using the circuit delay (See Figure 3-3)

4. Asynchronous set/reset is not used other than system reset

In reality, it is difficult to operate all registers synchronously with one clock. However, it is strongly recommended to reduce the number of clock signals. The more clock signals are used and the more complicated relationships between signals exist, the longer time EDA tools need to be run, and less chance the tools output accurate results.

Figure 3-2 Examples of feedback loop

Chapter 3 Design Restrictions and Limitations

16 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

Figure 3-3 Pulse generation using delay

3.2 Differentiating Circuits are Prohibited The propagation delay time (tpd) of each LSI element is dependent on the operating environment (voltage, temperature, etc.) and manufacturing conditions. Therefore, in differentiating circuits using relative tpd differences as the one shown in Figure 3-4, pulse widths may not be enough under certain operating environments or manufacturing conditions, and circuit malfunctions may result.

When using differentiating circuits, do no use the circuit design shown in Figure 3-4. Use the circuit with flip-flops as the one shown in Figure 3-5.

Figure 3-4 Bad example of differentiating circuit

CLK

CK

D Q

XQ

CK

D Q

XQ

Figure 3-5 Differentiating circuit using flip-flops

D

C

Q

XQR

DFR

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 17 DESIGN GUIDE

3.3 Clock Tree Synthesis

3.3.1 Outline

Epson offers the service of clock tree synthesis that automatically inserts a tree of buffers in order to optimize the clock skew and delay. Clock trees inserted by customers by themselves for clock line fan-out adjustment sometimes result in larger clock skew and delay. This is because the layout tool run later changes the layout of inserted buffers. To prevent this, customers are requested not to insert clock line buffers by themselves, but ask Epson to perform clock tree synthesis.

It is possible to optimize the skew and delay of gated clock lines as well.

For the clock tree synthesis service, Epson asks the customer to insert dedicated buffers or dedicated gating cells in clock lines for the following three reasons:

1. To decide the place to implement clock tree synthesis

2. To run pre-layout simulation, estimating the delay of clock tree buffers to be inserted

3. To back-annotate delay values to the inserted clock tree for running accurate post-layout simulation

Chapter 3 Design Restrictions and Limitations

18 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

3.3.2 Design Flow

P&R Clock Tree Synthesis

Post-layout netlist* SDF

Post-layout simulation

Post-layout simulation result Verify post-layout

simulation result

OK

NG

Circuit change Circuit verification

Netlist after circuit change

Pinout or

ppd ECO

(Enginnering Change Order)

Post-layout netlist*

Sign off

Clock Tree Synthesis Check Sheet

Initial netlist

Pinoutor

ppd

Customer Seiko Epson

(ECO is a technique to perform P&R only for places that require modifications.)

Notes:

• Post-layout netlists include buffers inserted by clock tree synthesis.

• To run post-layout simulation, netslists including buffers inserted by clock tree synthesis and sdf file are used.

• If the post-layout simulation result does not meet the design requirements, modify the post-layout netlists. If the initial netlists are modified, P&R needs to be iterated.

• If the circuits of clock nets (dedicated buffers, gating cells, and DFF) are modified, P&R needs to be iterated. If changes occurred to the clock nets, contact Epson.

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 19 DESIGN GUIDE

3.3.3 How to implement

Select dedicated buffers for clock tree synthesis from Table 3-2, and dedicated gating cells for gated clock tree synthesis from Table 3-3. Insert the selected buffers and gating cells considering the constraints described in Section 3.3.4 and Reference circuit 1 shown below.

In the case of the circuits created by logic synthesis, dedicated buffers and gating cells are not automatically inserted. They must be directly written to netlists. Also, not to synthesize other buffers in the clock lines where dedicated buffers or gating cells are inserted, execute the following command of Design Compiler:

set_dont_touch_network clock_name

Table 3-1 Skew values for reference

Fan-out count Without gating cells With gating cells 0 to 500 ± 200ps ± 300ps

500 to 3000 ± 250ps ± 400ps 3000 to 10000 ± 300ps ± 500ps Over 10000 ± 350ps ± 600ps

Notes:

• Skew values vary depending on the circuit size, wire congestion, and clock count.

• Do not use gating cells in series. Up to 20 gating cells are allowed to use.

• The skew values shown for reference are for the case where gating cells are not used in series and the number is 20 or less.

• If multiple gating cells are used in series or the total number exceeds the limit, post-layout simulation may output timing errors due to skew. To prevent delay in the development schedule, minimize the number of gating cells.

Table 3-2 Dedicated buffers

S1L50000 Series

Cell name T0 Max (ns) Guideline number of fan-outs

CRBF1 1.00 0 to 200 CRBF1H 1.50 0 to 300 CRBF2 2.00 0 to 500 CRBF3 3.00 500 to 3000 CRBF4 4.00 3000 to 10000 CRBF5 5.00 Over 10000 CRBF6 6.00 CRBF7 7.00 CRBF8 8.00

Chapter 3 Design Restrictions and Limitations

20 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

Notes:

• The K value (delay due to fan-out) of these cells is set to 0 for pre-layout simulation.

• The fan-out value of these cells is set to infinite.

• Delay values relative to fan-out count vary depending on the design size and the utilization. Use the values only for reference.

Table 3-3 Dedicated gating cells

Circuit configuration (Function) Cell name AND CAD2P OR COR2P

2-1 selector AND-OR CAO24A NAND CNA2P NOR CNO2P

2-1 selector AND-NOR CAN24A INVERTER CPV2

Latch-based AND CLAD2V Latch-based OR CLOR2V

Latch-based AND with test pin CLPSAD2V Latch-based OR with test pin CLPSOR2V

Latch-based gating cells are offered among the gating cells. The benefit of using the latch-based gating cells is that glitches that occur when signals switch in clock lines do not propagate, and thus clock signal is stable.

For the latch-based gating cell function structure, see the S1L50000 Cell Library.

Notes:

• The delay values of these cells (T0) are set to 0 for pre-layout simulation.

• The K value (delay due to fan-out) of these cells is set to 0 for pre-layout simulation.

• The fan-out values of these cells are set to infinite.

3.3.4 Constraints and notes

• Implementing clock tree synthesis increases the gate count by 10 to 30%.

• If too many gating cells are used, timing errors due to skew may occur in the post-layout simulation. Minimize the number of gating cells not to delay the development schedule.

• Dedicated buffers and gating cells are usable only for clock tree synthesis.

• Clock tree synthesis is possible to implement on data lines and other control signals. However, the increase of synthesized nets results in larger skew and delay values. Therefore, confine the implementation of clock tree synthesis up to 10 nets, which are critical and have large fan-out values.

• Implementing clock tree synthesis on nets with small fan-out may increase delay and skew. Limit clock tree synthesis only to nets with more than some dozen fan-out values.

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 21 DESIGN GUIDE

• Do not insert cells other than dedicated gating cells in the clock line. If cells other than dedicated gating cells are included in the clock line, skew occurs in the pre-layout simulation.

• Dedicated gating cells must be combined with dedicated buffers to use. If dedicated gating cells are used alone by mistake, skew and delay values are not optimized.

• As the number of dedicated gating cells inserted in one clock net increases, skew and delay values become larger. Up to 20 dedicated gating cells allowed.

• If multiple gating cells are used in series, skew and delay values increase. Do not use dedicated gating cells in series.

• The default skew adjustment covers cells with clock pin, such as DFF and latch cells. If skew must be adjusted for cells without clock pin, contact Epson.

• If the net covered by clock tree synthesis is connected to the input pin of a megacell, the skew up to the megacell input pin is adjusted.

• Do not use multiple dedicated buffers in series. If dedicated buffers are in clock nets, skew and delay values are not optimized.

Chapter 3 Design Restrictions and Limitations

22 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

3.3.5 Clock Tree Synthesis Check Sheet

To implement clock tree synthesis, the following information is required:

Target skew and delay values

Instance name of CRBF* Target Skew (Max.) (SIM condition: MAX)

Target Delay (Min./Max.) (SIM condition: MAX)

Notes:

• The target values will be used only as reference for synthesis. Care must be taken because the shown values are not guaranteed to meet.

1. The number of clock line is 10 or less Yes / No

2. Clock net has dedicated gating cell Yes / No If the answer to question 2 is “Yes,” answer questions 3 through 9.

3. The number of dedicated gating cells used in each clock net is 20 or less Yes / No

4. Dedicated gating cells are not used in series Yes / No

5. Clock net has dedicated buffer Yes / No

6. Clock net has cell other than dedicated gating cell Yes / No If the answer to question 6 is “Yes,” describe the cell name(s) below.

Notes: • If “3-input AND” is treated as a special gating cell, the cell is treated as a special gating cell

in all clock lines. • DFF and latch cells are not treated as special gating cells.

7. Skew adjustment on cells other than DFF and latch cells is desired Yes / No If the answer to question 7 is “Yes,” describe the cell name(s)/pin name(s) below.

Cell name: Pin name: Cell name: Pin name: Note:

• If the skew of an inverter is adjusted, the skew of inverter cells in all clock lines are adjusted.

8. The circuit configuration as the one shown in Reference circuit 2 exists. Yes / No Note:

• It is not possible to optimize the skew of DFF clock nets in both sections A and B. To adjust the skew of both DFF clock nets, add “CAO24A” as shown in Reference circuit 2.

9. The circuit configuration as the one shown in Reference circuit 3 exists. Yes / No Note:

• DFF in section A is driven by both clock roots A and B. It is not possible to adjust the skew of both clock roots. In Reference circuit 3, “CRBF” of clock root B must be deleted.

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 23 DESIGN GUIDE

3.3.6 Reference

3.3.6.1 Circuits before and after clock tree synthesis

D

C

Q

XQ R

DFR

P

CAD2P

CRBF2 Clock Root

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

Before executing Clock Tree Synthesis

Clock tree synthesis optimizes the skew of the thick clock lines.

D

C

Q

XQ R

DFR

P

CAD2P

CRBF2 Clock Root

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

After executing Clock Tree Synthesis

Reference circuit 1

As shown in the above circuit, executing clock tree synthesis inserts buffers in the dotted circles.

Chapter 3 Design Restrictions and Limitations

24 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

3.3.6.2 Solution for problematic circuit 1

D

C

Q

XQ R

DFR

CAO24A

CRBF2 Clock Root A

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

Clock Root B CRBF2

Original circuit

D

C

Q

XQ R

DFR

CAO24A

CRBF2 Clock Root A

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

Clock Root B CRBF2

After modification

PDW

CAO24A

Dummy Cell ↓

Reference circuit 2

The DFFs in the dotted circle in the original circuit are driven by clock roots A and B. Clock tree synthesis is not applicable to circuits like this. In this case, insert dummy “CAO24A” as shown in the modified circuit. Clock tree synthesis optimizes the skew of thick clock lines shown in the above diagram.

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 25 DESIGN GUIDE

3.3.6.3 Solution for problematic circuit 2

D

C

Q

XQ R

DFR

CAO24A

CRBF2Clock Root A

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR Clock Root B CRBF2

Reference circuit 3

The DFFs in the dotted circle in the original circuit are driven by clock roots A and B. Clock tree synthesis is not applicable to circuits like this. In this case, delete the “CRBF” cell in clock root B.

3.3.6.4 Solution for problematic circuit 3

D

C

Q

XQ R

DFR

P

CAD2P

CRBF2

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

D

C

Q

XQ R

DFR

CRBF2

Reference circuit 4

Chapter 3 Design Restrictions and Limitations

26 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

In the above circuit, two dedicated buffer cells, CRBF2 and CAD2P, are connected in series. Delete CRBF2 connected to CAD2P, as it is not required.

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 27 DESIGN GUIDE

3.4 Designing High-Speed Circuits In high-speed operation (operating frequency higher than 60MHz), one cycle time is short and thus allowable propagation delay becomes small. Care must be taken for the following points in the design phase to minimize propagation delay values.

<To minimize propagation delay values>

• Avoid using NOR gates, but use NAND gates to build logic*1.

• Avoid using too many logic elements with multiple inputs*1.

• Use a tree structure at points where one element drives many nodes*2. Limit the number of nodes to drive to 10.

• For the output pins of logic elements driven at high speed (the operating frequency of 60MHz or higher) and circuits where very limited delay is allowed, reduce the fan-out values to one-half or one-third of typical values*2

• Use high drivability type logic elements for those connected to modules, macros and I/Os*2.

• Exclude the paths with ample timing margin from the design constraints. (Synthesis tools tend to start optimization from the paths most difficult to meet the constraints. Therefore, eliminating unnecessary timing constraints reduces the synthesis tool run time. If it is unavoidable that the circuit has a very small timing margin or timing errors, contact Epson in advance.)

NOTE: *1: Since high- and low-level drivability is different, NAND gates can build circuits with less delay time than NOR gates. Avoiding the use of logic elements with multiple inputs also help reduce delay time.

*2: In the actual layout of LSI circuit, load capacitance includes not only the input capacitance of the cell connected but also wire capacitance. Accurate wire capacitance is known only after the circuit layout, and a specific node may have large capacitance as the result of layout. To limit the increase in post-layout load capacitance, reduce the number branches driven by a single node.

Chapter 3 Design Restrictions and Limitations

28 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

3.5 Metastable In the case of FF and latch cell input signals, if they violate timing rules, such as clock and data setup time, hold time, and release or removal time of clock set and reset, the FF and latch cell output signals may go neither high or low level. This unstable state of output signals is called “metastable.”

The metastable state ends after some time and output signals enter the defined state of either high or low level. However, the defined levels are not dependent on the data input level, and thus outputs are in unknown state.

When setup/hold and release/removal timing specifications are not met, take appropriate measures to prevent the metastable state from propagating to the whole circuit.

In the S1L50000 Series, the metastable time is estimated by the following formula, when setup/hold, and release/removal time specifications are not met:

Metastable time = Tpd x 6

Where Tpd is the delay time from the active edge of FF, latch cell clock, set, and reset signals to output change.

Logic simulation does not consider the delay of signals in the metastable state. Ensure that the design meets the timing specifications.

Fugure 3-6 DF metastable state

D

C

Q

XQ CLOCK

Seup Hold

DATA

CLOCK

Output expected value: Q

Tpd

Output: Q Metastable state

Meatastable state/unknown state

DF

DATA Q

XQ

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 29 DESIGN GUIDE

3.6 Internal Bus Configuration The bus circuit is composed of tri-state logic buffers. By operating the bus control signal, one of the outputs connected to the bus circuit is set active (other outputs are in the high-impedance state), and the one signal line is shared by allocating accessible time.

The following are the points to pay attention when building an internal bus circuit using internal tri-state buffers.

• Use bus cells only for bus circuits. (See Table 3-4 for the S1L50000 series bus cells)

• When building a bus, attach the bus latch cell BLT* to the bus.

• Among the bus cells connected to a bus, only one output is set active (0 or 1); other bus cell outputs must be set to high-impedance state (Z)*1.

• The fun-out of the bus cell connected to a bus must be the specified value or less*2.

• Bus circuits tend to increase propagation delay due to fan-out values and thus not suitable for high-speed operation*2.

• Data held by the bus latch cell should be used only to prevent floating; do not use it as a logic signal*3.

• Generate test patterns that can easily initialize bus circuits*4.

• The bus control signal is allowed to switch only once per cycle.

Notes: *1: If multiple bus cells connected to a bus are simultaneously become active (either 0 or 1), the output voltage level goes unstable and a flow-through current continually flows from VDD to GND. To avoid this, this rule must be met.

*2: If the load on the internal bus is large, the rising and falling times of signals extend due to longer wiring and more connections. This lowers the accuracy of logic simulation.

*3: Even when all the bus cells connected to a bus are set in the high-impedance state (Z), data is held by the bus latch cell. However, the latch function is limited not to affect the circuit in operation. Therefore, do not use the data held in the latch cell as valid data.

*4: Enhance testability by adding a test pin for better control of bus circuits or other means.

Table 3-4 S1L50000 Series Bus Cells

Cell nmae Cell type

1-bit 4-bit 8-bit

Bus latch BLT1 BLT4 BLT8

Bus driver TSB, TSBP T244H T244

Inverting bus driver TSV, TSVP T240H T240

Transparent latch with reset and 3-state output - T373H T373

D flip-flop with reset and 3-state output - T374H T374

1-bit RAM RM1 - -

Chapter 3 Design Restrictions and Limitations

30 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

TSB

TSB

BLT1

IN 1

NA2

Figure 3-7 Bus cell circuit example

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 31 DESIGN GUIDE

3.7 Avoid Contention with External Bus When a gate array and other LSI are connected on a system by bus, possible solutions for bus contention, such as adding pull-up and pull-down registers, must be considered in addition to the notes described in the previous section, Internal Bus Configuration. Also, to prevent the external bus floating, IO cells with pull-up or pull-down resistor and those with bus-hold function* are available.If no measures are taken for bus contention, the input levels may be unstable, and cause erroneous operations and increase input current leakage.

* : Bus-hold circuit:

In the S1L50000 series library, IO buffers with bus-hold function that holds the output pin data are available to prevent output or bi-directional pins from going to the high-impedance state. However, the function to hold data is limited not to affect the normal operation. The data held by the bus-hold function is easily affected by external data if supplied. See the section of Electrical Characteristics for the output current held by the bus-hold circuit.

Output signal

Enable signal

Test pins Output pin

(a) Output buffer

Input signal

Output signal

Enable signal

Test pins

Bi-directional pin

(b) Bi-directional buffer

Figure 3-8 Example of bus-hold circuit symbol

Chapter 3 Design Restrictions and Limitations

32 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

3.8 Solution for Hazards In the case of circuits combining NAND and NOR gates or decoder cells, a very short pulse may occur because of the difference in timing delay of gates. This short pulse is called “hazard” and it causes erroneous operations if it is input to the clock or reset pin of flip-flops.

Therefore, care must be taken to design circuits that do not propagate hazards. When using a decoder circuit, for example, use the circuit with “enable” pin.

D

C

Q

D

C

Q

D

C

Q

D

C

Q

D

C

Q

D

C

Q

Figure 3-9 Solution examples for hazard

3.9 Oscillator Circuits

3.9.1 Oscillator circuit configurations

There are two types of cells dedicated to oscillation circuits. One is for the crystal oscillation and the other, for the CR oscillation. Further, the crystal oscillation circuits are divided into two types – continuous and intermittent types. Each type has those for the internal cell area and those for the I/O cell area. The following illustrates that the oscillation circuit configurations differ depending on the oscillator cell used.

G X

D

LIN LOT

Rf

X ’tal Rd

Cg Cd

Inside IC

OSC c ell

C ontinuous osc illation

G

E

X

D

LIN LOT

Rf

X ’tal Rd

Cg Cd

Inside IC

O SC cell

Interm itten t oscillation

Figure 3-10 Crystal oscillator circuits (for internal cell area)

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 33 DESIGN GUIDE

RfX’tal

Rd

Cg

Cd

Inside IC

LIN

Oscillator cell

G

X

PAD

Continuous oscillation

Figure 3-11 Crystal oscillation circuit (for I/O cell area)

G X

R

C

LIN LOT LOT

R

C

Inside IC

Oscillator cell

Figure 3-12 CR oscillation circuit

3.9.2 Notes when using oscillator circuits

(1) Pinout

• Place the input and output pins of the oscillator circuit next to each other and enclose them with the power supply pins (VDD, VSS) on both sides.

• Place the input and output pins of the oscillator circuit away from other output pins, especially from those in-phase or out-of-phase of the oscillation waveform. Place such output pins on the opposite side of the package.

• Place the input and output pins of the oscillator circuit away from the input pins that operate at high speed, such as clock.

• Place the input and output pins of the oscillator circuit at the center of one of the four package sides.

• When multiple oscillator circuits are embedded, place them away from one another to prevent interference.

Chapter 3 Design Restrictions and Limitations

34 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

• When using an area array package such as BGA, contact our sales representative regarding the pinout.

(2) Test pattern generation

For how to generate test patterns for the circuit with an oscillator, refer to Section 8.5 of Chapter 8, “Notes When Using Oscillation Circuit.”

(3) How to select oscillator cells

The oscillation frequency ranges from several tens of KHz to several tens of MHz. For details, contact our sales representative.

(4) How to determine the external resistance and capacitance

The oscillator circuit characteristics are dependent on the elements of the circuit (IC, crystal, Rf, Rd, Cg, Cd, and the board). Therefore, determine the values of external Rf, Rd, Cg, and Cd, by mounting the components on the actual board and testing them fully.

(5) Guarantee level

The oscillator circuit characteristics are dependent on the elements of the circuit (IC, crystal, Rf, Rd, Cg, Cd, and the board). Therefore, Seiko Epson cannot guarantee the oscillation operation or characteristics. It is recommended that the customer spend ample time on the evaluation and confirm the oscillation characteristics using ES samples.

(6) Oscillator circuits with dual power supplies

The oscillator circuit configuration with dual power supplies is basically the same as that with single power supply. Since the oscillator cell is connected to LVDD power supply, use LLIN and LLOT for the LIN and LOT cells respectively.

(7) About the clock signal input to the IC internal circuit

Because it is difficult to specify the waveform of the clock signal to be generated (signal of the oscillator cell X) in advance, what the logic simulator can accurately handle is only the clock frequency. For example, the actual clock duty of the IC differs from the simulation result.

Therefore, avoid using the circuit utilizing both rising and falling times of the generated clock signal. Circuits with errors not detected by the simulation may be produced. Use the circuit only utilizing either rising or falling time of the generated clock signal.

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 35 DESIGN GUIDE

3.10 Constraints on Verilog-HDL/VHDL Netlists The Verilog-HDL/VHDL netlists to be transferred to Epson for further design processes must be pure gate-level netlist (without functional or behavioral descriptions). The restrictions and constraints on the development of Epson ASICs using Verilog HDL/VHDL will follow.

3.10.1 Constraints on Verilog-HDL/VHDL netlists

1. External pin names (I/O pins)

• Use only uppercase letters

• Number of characters allowed: 2 to 32

• Bus descriptions are prohibited

• Legal characters: Alpha-numeric characters and underscore, _; only a letter of the alphabet is allowed to use for the initial character

• Examples of illegal character strings:

2INPUT: Starts with a numeric character

¥2INPUT: Starts with a symbol

InputA: Includes lowercase characters

_INPUTA: Starts with an underscore

INA [3:0]: Bus description

INA [3]: Bus description

2. Internal pin names (including bus nets)

Mixing uppercase and lowercase characters are allowed, but names must be unique; thus using both “RESET” and “Reset” is not allowed.

• Number of characters allowed: 2 to 32

• Legal characters: Alpha-numeric characters, underscore, _, and square brackets, [ ] (Verilog bus brackets), and parentheses, ( ) (VHDL bus brackets). Only uppercase characters for initial characters.

3. Module names

Module names are case-sensitive on the system, but mixing uppercase and lowercase characters is prohibited by the design rule.

e.g. “TOPMODULE” and “TopModule”

Pay attention to cell names as they are case-sensitive.

4. Bus description is prohibited in the top module.

e.g. DATA [0:3], DATA [3], DATA[2] are prohibited. DATA0, DATA1, DATA2 are allowed.

5. Keep using the same series library for IO cells throughout the design; do not mix other series IO cells.

6. Behavioral, RTL, and C language descriptions are not allowed. Such descriptions in netlists are invalid.

7. The time scale accuracy of library is 1 ps in all series.

Chapter 3 Design Restrictions and Limitations

36 EPSON GATE ARRAY S1L50000 SERIES DESIGN GUIDE

3.10.2 Constraints on Verilog netlists

1. The “assign” and “tran” statements are prohibited in the gate-level Verilog netlist.

2. Use cell pin names to describe connections in the Verilog netlists.

e.g.

Legal: IN2 inst_1 (.A(inst_2),.X(inst_3)); Illegal: IN2 inst_1 (net1,net2);

3. Verilog commands such as “force” are not allowed to describe the behavior of flip-flops. e.g. force logic.signal = 0;

4. The time scale is described at the head of the gate-level netlists compiled by the Synopsys Design Compiler. For this time scale, describe the value shown in the Seiko Epson’s Verilog library. The time scale is 1 ps in all series.

e.g. `timescale 1ps/1ps

5. Single port bus names and those with “escape” character (¥) are not allowed to use together in the same module by the Epson design rules.

e.g. input A[0]; wire ¥A[0];

6. The following character strings are Verilog reserved words and thus prohibited to use as user defined names.

always and assign begin buf bufif0 bufif1 case design default defparam disable else end endcase endfunction endmodule endtask event for force forever fork function highz0 highz1 if initial inout input integer join large medium module nand negedge nor not notif0 notif1 or output parameter posedge pull0 pull1 reg release repeat scalared small specify strong0 strong1 supply0 supply1 task time tri tri0 tri1 trinand trior trireg vectored wait wand weak0 weak1 while wire wor xor xnor

Chapter 3 Design Restrictions and Limitations

GATE ARRAY S1L50000 SERIES EPSON 37 DESIGN GUIDE

3.10.3 Constraints on VHDL netlists

1. In addition to the constraints listed in Section 3.10.1, the following character strings are prohibited to use. Since Epson uses TEXTIO package to run simulation, the function names used by the TEXTIO package are prohibited to use for user definitions.

INPUTA_: Ends with an underscore, _

INPUT_ _A: Uses two consecutive underscores, _ _

Read: Used by TEXTIO package

Write: Used by TEXTIO package

2. The following character strings are VHDL reserved words and thus prohibited to use as user defined names.

abs access after alias all and architecture array assert attribute begin block body buffer bus case component configuration constant disconnect downto else elsif end entity exit file for function generate generic guarded if in inout is label library linkage loop map mod nand new next nor not null of on open or others out package port procedure process range record register rem report return select severity signal subtype then to transport type units until use variable wait when while with xor

3. To use Epson’s tools and utility programs, VHDL format files must be converted into Verilog format. Therefore, the Verilog reserved words listed in Section 3.10.2 are also prohibited.

3.10.4 About descriptions of oscillator cells and AC/DC test circuit cell (TCIR2)

Instantiate oscillator cells and add the “dont_touch” attribute using the “set_dont_touch” command to the input and output nets to prevent the synthesis tool from inserting buffers to the nets connecting the external pins of the oscillator cells.

Since the AC/DC test circuit cell, TCIR2, is a hard macro, gate descriptions as those shown below are required: