Gain Cell Embedded DRAM for Ultra-Low Power … 6, 2015 1 Gain Cell Embedded DRAM for Ultra-Low...

Transcript of Gain Cell Embedded DRAM for Ultra-Low Power … 6, 2015 1 Gain Cell Embedded DRAM for Ultra-Low...

May 6, 2015 1

Gain Cell Embedded DRAM for Ultra-Low Power Applications at scaled CMOS Nodes

May 6, 2015

Robert Giterman

EnICS Labs Nanoelectronics Program

Faculty of Engineering, Bar-Ilan University, Israel

May 6, 2015 2

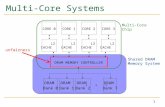

Increasing Need for Embedded Memories in VLSI SoCs

• Memories often consume >50% of area & power

• 1st point of failure under voltage scaling

• Limit yield

Intel Xeon

Intel AMD Opteron 6300

May 6, 2015 3

Evolution of Total Cache Size Over Time

www.anandtech.comsource:

2MB

10MB

5X in 4 years

50x increase in 25 years [ITRS’11]

May 6, 2015 4

The 6T SRAM Bit Cell

• Several standby leakage paths.

• Dense, symmetric layout, but still six transistors.

• Supply voltage limited due to ratioed operation.

• Single-ported.

May 6, 2015 5

Advantages and Drawbacks of Gain Cells

In light of technology and voltage scaling, gain-cells have several advantages over conventional 6T SRAM and 1T-1C eDRAM:

• Smaller cell size than SRAM, less bitcell leakage

• Compared to 1T-1C eDRAM:

– Logic-compatible, i.e., no special processing steps, and no extra cost.

– Non-destructive read operation.

• Naturally two-port.

• Optimize for read-ability AND write-ability.

Drawbacks:

• Dynamic. Energy-costly refresh cycles?!

• May have lower retention (refresh + leakage) power than SRAM (leakage only)

Chun, VLSI’09

SRAM

Gain-cells

Trench cap Stacked caps

Kang, McGraw-Hill’03

May 6, 2015 6

Gain Cells : Basic Topologies

MW MS

MR

RWLWWL

WB

L

RB

L

3T Gain Cell

MRMW

RWLWB

L

WWL

RB

L

2T Gain Cell

Somasekhar, et al. JSSC 2009 Chun, et al. JSSC 2011

• Dynamic memory cell, built from MOS transistors (& MOS caps), write port (WWL & WBL), storage cap, and read port (RWL & RBL).

May 6, 2015 8

Main Leakage Components • Conventional 2T gain cell

implementations in sub-100nm technologies display very low retention times, due to substantially higher leakage currents.

• Depending on the type of write transistor (WT), one of the data levels has a much higher retention time than the other (‘1’ for a PMOS WT, ‘0’ for a NMOS WT).

Level ‘1’ is stored

Level ‘0’ is stored

May 6, 2015 9

Main Leakage Components • Conventional 2T gain cell

implementations in sub-100nm technologies display very low retention times, due to substantially higher leakage currents.

• Depending on the type of write transistor (WT), one of the data levels has a much higher retention time than the other (‘1’ for a PMOS WT, ‘0’ for a NMOS WT).

May 6, 2015 10

4T Gain Cell • The ‘weaker’ data level is strengthened by the addition of a buffer node (BN) and a

feedback device to the basic configuration, which conditionally discharges node BN according to the stored data level.

• The data retention time (DRT) estimation is higher by an order of magnitude than that of a conventional 2T gain cell.

May 6, 2015 11

4T Gain Cell • The ‘weaker’ data level is strengthened by the addition of a buffer node (BN) and a

feedback device to the basic configuration, which conditionally discharges node BN according to the stored data level.

• The data retention time (DRT) estimation is higher by an order of magnitude than that of a conventional 2T gain cell.

• The proposed gain cell layout is only 60% of a redrawn 6T SRAM cell in the same 65nm node.

May 6, 2015 12

Comparison With other Embedded Memory Options

May 6, 2015 13

Questions and Open Discussion