FinFET technologies for Digital Systems with Radiation ... · Photos placed in horizontal position...

Transcript of FinFET technologies for Digital Systems with Radiation ... · Photos placed in horizontal position...

Photos placed in horizontal position

with even amount of white space

between photos and header

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly

owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy’s National Nuclear Security Administration under contract DE-NA0003525.

FinFET technologies for Digital Systems with Radiation Requirements: TID, SEE, Basic

Mechanisms, and Lessons Learns

Michael P. King

Motivation

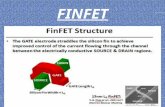

Most commercial fabs have migrated to FinFETs below 20-nm gate length feature sizes

FinFETs exhibit improved electrostatic control of the channel and improved reliability compared to equivalent scaled planar CMOS

Some work on the TID response of FinFETs has been presented at IRPS, NSREC, and RADECs

T. Hook, FDSOI Conference, Taiwan, 2013

Outline

Technology overview

A very basic review of radiation effects in CMOS devices

Total ionizing dose (TID) in 14/16-nm FinFET devices

Single-event upset (SEU) in 14/16-nm FinFETs: data and discussion of mechanisms

Observation of single-event latchup (SEL) in a 14/16-nm FPGA?

Conclusions

3

Current Technology Engagements

GlobalFoundries

14-nm FinFETs

22-nm FDSOI

NVM

Optane / 3D CrossPoint

IBM

32-nm PDSOI

22-nm PDSOI

TSMC

16-nm FPGAs (Xilinx)

TECHNOLOGY PROGRESSION

1995 1997 1999 2001 2004 2006 2008 2010 2012 2014

350

nm

250

nm

180

nm

130

nm

90

nm

65

nm

45

nm

32

nm

22

nm

14

nm

Technology Scaling Trends

Path to FinFET Technology

7

Bulk FinFET Processing Technology

8

A. Yagishita (Toshiba), SOI Short Course (2009)

Increasing processing complexity

More challenging lithography

Quad patterning

Soon EUV

Line edge roughness

Isolation steps STI

CSD/SSRW

Advantages / Challenges

9

M. G. Bardon (IMEC) ICICDT (2015)

Uppal (GF), IIRW (2016)

Gate length shrink

Performance scaling

FET is on edgeDual gate

Recuces Ioff

110 not 100

Performance ⬆ 20 %

Power ⬇ 35%

Reliability Outlook

FinFET TDDB shows improvement over planar

pMOS FinFET NBTI did show some regression; improved in second gen. overall BTI improved

HCD does degrade some for FinFETs

pMOS

NBTI

nMOS

TDDBnMOS

HCD

RADIATION EFFECTS IN SEMICONDUCTORS

Brief review

Total Ionizing Dose Degradation Mechanisms

Shifts in threshold voltage changes drive current in on-state

Increased leakage current at STI sidewalls causes higher power dissipation

Timing / switching mismatch for digital systems

Traditionally preferential impact on nMOSFETs

12

Chatterjee, IEEE TNS, 2013.

Single Event Latchup (SEL)

A high current state sustained by a positive feedback loop in a n-p-n-p junction resulting from charge injection in cross-coupled bipolar junction transistor

Similar to electrical latchup except initiated by a charged particle interaction

13

Why do we care?

• Well it requires a power-

down event to quench

• Can be destructive if not

handled quickly

• Parts that exhibit such

behavior are high risk

Single Event Upset (SEU)

A possible circuit response to a charged particle interacting in specific regions of a memory (SRAM depicted) leading to an erroneous data state

Problem because of data integrity and fault propagation up to the system level

14

RESULTS

And now for some data…

15

TID vs Technology Scaling

16

Scaling trends of off-state leakage vs technology node

PDSOI exhibits very low leakage for 45- and 32-nm at 1 Mrad

Migration to FinFETs resulted in a dramatic increase in post-irradiation leakage (early look)

FDSOI shows leakage comparable to older technologies

Hughes (NRL) REDW NSREC (2015)

Description of Test Structures

Single logic and IO transistors in all Vth

flavors

Special Structures

Ring oscillator (RO) (RF) transistors

Static random access memory (SRAM) transistors

17

Experimental Methods

Information extracted from Ids-Vgs curves Vth – linear region approximation

gm = dIds/dVgs

Ids,on = Ids @ Vgs = 0.9 V, Vds = 50 mV

Ids,off = Ids @ Vgs = 0 V, Vds = 50 mV

Bias Conditions Off-state: Vd = 1.0 V, Vg = Vs = Vb = 0 V

On-state: Vg = 1.0 V, Vd = Vs = Vb = 0 V

Half-on-state: Vg = 0.5 V, Vd = Vs = Vb = 0 V

Devices irradiated at 525 rad(SiO2)/s

18

Low-Vth Device Bias Dependence

19

Large changes in Ids,off

Gate-controlled leakage component

On-state condition gives largest degradation

Minimal change in Vth

TID Irradiation Bias Dependence

DIds,off shows most degradation for on-state condition

DVth fairly similar for all bias conditions (and small)

Lower operating voltage (half-on-state) shows marginal improvement in DIds,off and DVth

compared to full on-state

20

High-Vth Device Bias Dependence

21

Less off-state leakage compared to low-Vth device

Reduced operating voltage has a greater impact on TID degradation for higher Vthdevice

Different Vth Devices – On-State

22

Increasing Vth shows less Ids,off degradation for equivalent dose

Process level decisions will clearly impact TID impact on devices, circuits, and ICs

Comparison of TID Variability for Different Vth

23

High-Vth device shows less DIds,off compared to Low-Vthdevices

On-state appears to be the worst case for device leakage response

A Tale of Two Commercial Processes

Typically comes about when they fix a leakage problem

Impossible to say if TID resilience remains a permanent feature of the technology going forward

-0.4 -0.2 0.0 0.2 0.4 0.6 0.8 1.0 1.210-6

10-5

10-4

10-3

10-2

10-1

100

101

102

103

104

Medium-Vth Device

On-state

Vgs = 1.0 V

Dra

in C

urr

ent (m

A/m

m)

Gate Voltage (V)

Initial

100 krad(SiO2)

200 krad(SiO2)

300 krad(SiO2)

500 krad(SiO2)

1000 krad(SiO2)

Two snapshots of a commercial

14/16-nm FinFET technology

show very different TID results

-0.2 0.0 0.2 0.4 0.6 0.810-8

10-7

10-6

10-5

10-4

10-3

10-2

10-1

100

LVT Dev 1

I ds (

mA

)

Vgs (V)

pre

100 krad

200 krad

300 krad

400 krad

500 krad

1 Mrad

Vg = 0.8 V

Vd = Vs = Vb = 0 V

W = 0.192 m

L = 0.014 m

Narrow width nFET

• Device shows more leakage in the on-state consistent with previous

experimental results

• Response to TID is much less severe than original observations

-0.2 0.0 0.2 0.4 0.6 0.810-8

10-7

10-6

10-5

10-4

10-3

10-2

10-1

100

LVT Dev 1

I ds (

mA

)Vgs (V)

pre

100 krad

200 krad

300 krad

400 krad

500 krad

1 Mrad

Vg = 0.8 V

Vd = Vs = Vb = 0 V

W = 0.192 m

L = 0.014 m

-0.2 0.0 0.2 0.4 0.6 0.810-8

10-7

10-6

10-5

10-4

10-3

10-2

10-1

100

W = 0.192 m

L = 0.014 m

LVT Dev 1

Vd = 0.8 V

Vg = Vs = Vb = 0 V

I ds (

mA

)

Vgs (V)

pre

100 krad

200 krad

300 krad

400 krad

500 krad

1 Mrad

Change in irradiated leakage and Vth

Drive current tracks Vth with irradiation

Leakage current shift smaller than previous evaluations

Results not consistent between foundries! – recent VU paper at NSREC 26

0.0 0.2 0.4 0.6 0.8 1.0

94.0

94.5

95.0

95.5

96.0

96.5

97.0

97.5

98.0

98.5

I ds,o

n (

A)

Total Dose (Mrad(SiO2))

Y

0.0 0.2 0.4 0.6 0.8 1.00.0

0.2

0.4

0.6

0.8

1.0

I ds,o

ff (

nA

)

Total Dose (Mrad(SiO2))

X

0.0 0.2 0.4 0.6 0.8 1.0250

255

260

265

270

275

280

Vth

(m

V)

Total Dose (Mrad(SiO2))

VTH

Not all is well in the land of Oz

• Largest device shows much more leakage than either of previous

two devices

• May be some dependence on total width/number of fingers

-0.2 0.0 0.2 0.4 0.6 0.810-7

10-6

10-5

10-4

10-3

10-2

10-1

100

101

102

W = 100 m

L = 0.014 m

RVT Dev 4

Vd = 0.8 V

Vg = Vs = Vb = 0 V

I ds (

mA

)

Vgs (V)

pre

100 krad

200 krad

300 krad

400 krad

500 krad

1 Mrad

-0.2 0.0 0.2 0.4 0.6 0.810-7

10-6

10-5

10-4

10-3

10-2

10-1

100

101

102

W = 100 m

L = 0.014 m

RVT Dev 4

Vg = 0.8 V

Vd = Vs = Vb = 0 V

I ds (

mA

)

Vgs (V)

pre

100 krad

200 krad

300 krad

400 krad

500 krad

1 Mrad

Xilinx UltraScale+ (16-nm) FPGA - SEU

28

0 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32

10-12

10-11

10-10

10-9

SE

U C

ross S

ection (

cm

2/b

it)

LET (MeV cm2 / mg)

SNL - SN2 - Config

SNL - SN2 - BRAM

NSWC Config

SNL SN3 - Config

SNL SN3 - BRAM

• Parts exhibit a fairly low SEU cross section

• For some environments 3D geometry effectively lowers

expected error rates even with higher bit density

Early Neutron SER Report

Industry looks at SER from alphas, muons, and neutrons for terrestrial environment reliability

Several reports of reduced SER from geometry change in FinFET vs planar

No reports of destructive effects due to neutrons to 109 n/cm2 from Broadcom or Intel

Mechanisms of SEU in FinFETs

3D geometry allows increasing drive without increase in Drain-Body/Well area

Most charge is collected from subfin/well region this implies a higher Qcrit without impacting the sensitive volume dimensions

30

Additional SEU Mechanisms

SER/SEU response ultimately will depend on things beyond our control

Channel stop doping

Well doping

Some control from layout and memory architecture

Effective transistor width

Spatial separation of critical nodes

DICE vs regular latch31

Xilinx UltraScale+ (16-nm) FPGA – “SEL”

0 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 3210-7

10-6

10-5

10-4

10-3

10-2

SE

L C

ross S

ection (

cm

2)

LET (MeV cm2/mg)

NSWC

SNL

Latchup

Parts exhibit SEL-like behavior at relatively low LET

Unclear if this is a circuit design issue or actual latchup

There are reports of SEL in 14/16-nm that exhibit the correct temperature dependence but none have such low threshold LET

Conclusions

On-state bias condition appears to be the worst case for Ids,off for all the transistor variations evaluated in this work

More recent studies indicate TID may be less of an issue, however, some big questions still remain

SEU shows some benefit for terrestrial environments even with higher memory density error rates can decrease

Several design parameters can lead to lower TID impact and SEU rates

We saw “SEL” and were not happy about it33