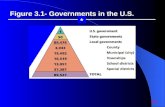

Figure 3.1 Digital logic technologies .

-

Upload

valentine-petty -

Category

Documents

-

view

24 -

download

2

description

Transcript of Figure 3.1 Digital logic technologies .

Full Custom

Standard Logic

Progammable Logic (FPLDs) ASICs

Digital Logic

TTL 74xx

CMOS 4xxx

PLDs FPGAs

Gate Arrays

Microprocessor & RAM

Standard Cell

CPLDs

Figure 3.1 Digital logic technologies.

PLDs

ASICs

Full CustomVLSI Design

Speed,Density,Complexity,MarketVolumeneeded forProduct

Engineering Cost, Time to Develop Product

CPLDsFPGAs

Figure 3.2 Digital logic technology tradeoffs.

Figure 3.3 Using a PLA to implement a Sum of Products equation.

Figure 3.4 Examples of FPLDs and advanced high pin count package types.

Product-TermSelectMatrix

ClearSelect

Clock/EnableSelect

VCC

PRN

CLRN

ENA

D Q

GlobalClear

GlobalClock

To I/OControl

Block

To PIA

This respresents amultiplexercontrolled by theconfigurationprogram

ProgrammableRegister

36 Signalsfrom PIA

16 ExpanderProduct

Shared LogicExpanders

LAB Local Array

Parallel LogicExpanders(from othermacrocells)

Figure 3.5 MAX 7000 macrocell.

Input/GCLK1Input/OE2/GCLK2

Input/OE1

LAB A

Macrocells1-166-

6-16

16

6-16

I/OControlBlock

6-16I/O Pins

3

LAB C

Macrocells33-486-

6-16

16

6-

I/OControlBlock

6-16I/O Pins

3

LAB B

LAB D

Macrocells17-32

Macrocells49-64

6-16

1

3

6-16

1

3

6-16I/O Pins

6-16I/O Pins

I/OControlBlock

I/OControlBlock

6

6

6

6

PIA

6 OutputInput/GCLRn

6 Output

6-

6-16

6-

6-

Figure 3.6 MAX 7000 CPLD architecture.

Figure 3.7 FLEX 10K100 FPLD die photo, PIA interconnects are visible.

PRN

CLRN

ENA

D Q

Programmable Register

DATA1DATA2DATA3DATA4

LABCTRL1LABCTRL2

Chip-WideReset

LABCTRL3LABCTRL4

Look-UpTable(LUT)

CarryChain

CascadeChain

To FastTrackInterconnect

To LAB LocalInterconnect

Clear/PresetLogic

Clock Select

CarryOut

CascadeOut

Register BypassCarry

InCascade

In

Figure 3.8 FLEX 10K Logic Element (LE).

4 InputLUT

(16 x 1 RAM)

ABCD

F

A

B

C

D

F

RAM Contents Address Data

A B C D F 0 0 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 1 0 1 0 1 0 1 1 0 1 1 0 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1

Figure 3.9 Using a lookup table (LUT) to model a gate network.

LE1LE1

LE2

LE3

LE4

LE5

LE6

LE7

LE8

Carry-In andCascade-In Column-to-Row

Interconnect

Row Interconnect

Dedicated Inputs &Global Signals

LogicBlockArray(LAB)

4

4

4

4

4

4

4

4

4

8

616

4

Carry-Out and Cascade-Out2

2

4

8 24

168

Figure 3.10 FLEX 10K Logic Array Block (LAB).

I/O Element(IOE)

IOE IOE IOE IOE IOE IOE IOE IOE IOE IOE

IOE IOE IOE IOE IOE IOE IOE IOE IOE IOE

IOE

IOE

IOE

IOE

IOE

IOE

IOE

IOERow

LocalInterconnect

Logic Element(LE)

Logic ArrayBlock (LAB)

EAB

EAB

Logic Array

EmbeddedArray Block(EAB)2K Bits RAM

Row

Figure 3.11 FLEX 10K CPLD architecture.

Figure 3.12 Silicon wafer containing XC4010E 10,000 gate FPGAs.

Figure 3.13 Single XC4010E FPGA die showing 20 by 20 array of logic elements and interconnect.

Look-UpTable(LUT)

G4G3G2G1

Look-UpTable(LUT)

F4F3F2F1

Look-UpTable(LUT)

S/RControl

S/RControl

H1 DIN/H2 ECSR/H0

1

1

D

EC

SD

RD

Q

D

EC

SDQ

RD

RegisterBypass

RegisterBypass

ProgrammableRegister

ProgrammableRegister

YQ

Y

XQ

X

4C1 • • • C4

K(Clock)

Figure 3.14 Xilinx 4000 Family Configurable Logic Block (CLB).

DeviceProgrammingSimulationDevice

FittingTranslationDesign

EntryOptimization &

Synthesis

Figure 3.15 CAD tool design flow for FPLDs.

![1. INTRODUCTION - NRICH · 2008-09-12 · 3.1 Solution of Part [1]9 Figure 3.1 Labels for Part [1]. Source: Made by the author. Thesis: All four triangles in the vecten (Figure 3.1)](https://static.fdocuments.us/doc/165x107/5f8a66ac79b30f78f4345b83/1-introduction-nrich-2008-09-12-31-solution-of-part-19-figure-31-labels.jpg)