DreamWork Animation DWA

-

Upload

intel-software -

Category

Software

-

view

1.770 -

download

4

Transcript of DreamWork Animation DWA

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Anson Chu (presenter) & Alex Wells,

& Martin Watt (DWA)

August 11 & 13, 2015

DreamWork Animation (DWA):

How We Achieved a 4x Speedup of Skin Deformation

with SIMD

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.Intel does not control or audit the design or implementation of third party benchmarks or Web sites referenced in this document. Intel encourages all of its customers to visit the referenced Web sites or others where similar performance benchmarks are reported and confirm whether the referenced benchmarks are accurate and reflect performance of systems available for purchase. Relative performance is calculated by assigning a baseline value of 1.0 to one benchmark result, and then dividing the actual benchmark result for the baseline platform into each of the specific benchmark results of each of the other platforms, and assigning them a relative performance number that correlates with the performance improvements reported. SPEC, SPECint, SPECfp, SPECrate. SPECpower, SPECjAppServer, SPECjbb, SPECjvm, SPECWeb, SPECompM, SPECompL, SPEC MPI, SPECjEnterprise* are trademarks of the Standard Performance Evaluation Corporation. See http://www.spec.org for more information. TPC-C, TPC-H, TPC-E are trademarks of the Transaction Processing Council. See http://www.tpc.org for more information.Hyper-Threading Technology requires a computer system with a processor supporting HT Technology and an HT Technology-enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. For more information including details on which processors support HT Technology, see here Intel® Turbo Boost Technology requires a Platform with a processor with Intel Turbo Boost Technology capability. Intel Turbo Boost Technology performance varies depending on hardware, software and overall system configuration. Check with your platform manufacturer on whether your system delivers Intel Turbo Boost Technology. For more information, see http://www.intel.com/technology/turboboostNo computer system can provide absolute security. Requires an enabled Intel® processor and software optimized for use of the technology. Consult your system manufacturer and/or software vendor for more information.Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families: Go to: Learn About Intel® Processor Numbers Intel product plans in this presentation do not constitute Intel plan of record product roadmaps. Please contact your Intel representative to obtain Intel’s current plan of record product roadmaps.Copyright © 2014 Intel Corporation. All rights reserved. Intel, the Intel logo, Xeon and Intel Core are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. All dates and products specified are for planning purposes only and are subject to change without notice*Other names and brands may be claimed as the property of others.

Legal Disclaimers

2

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

The above statements and any others in this document that refer to plans and expectations for the third quarter, the year and the future are forward-looking statements that involve a number of risks and uncertainties. Words such as “anticipates,” “expects,” “intends,” “plans,” “believes,” “seeks,” “estimates,” “may,” “will,” “should” and their variations identify forward-looking statements. Statements that refer to or are based on projections, uncertain events or assumptions also identify forward-looking statements. Many factors could affect Intel’s actual results, and variances from Intel’s current expectations regarding such factors could cause actual results to differ materially from those expressed in these forward-looking statements. Intel presently considers the following to be the important factors that could cause actual results to differ materially from the company’s expectations. Demand could be different from Intel's expectations due to factors including changes in business and economic conditions; customer acceptance of Intel’s and competitors’ products; supply constraints and other disruptions affecting customers; changes in customer order patterns including order cancellations; and changes in the level of inventory at customers. Uncertainty in global economic and financial conditions poses a risk that consumers and businesses may defer purchases in response to negative financial events, which could negatively affect product demand and other related matters. Intel operates in intensely competitive industries that are characterized by a high percentage of costs that are fixed or difficult to reduce in the short term and product demand that is highly variable and difficult to forecast. Revenue and the gross margin percentage are affected by the timing of Intel product introductions and the demand for and market acceptance of Intel's products; actions taken by Intel's competitors, including product offerings and introductions, marketing programs and pricing pressures and Intel’s response to such actions; and Intel’s ability to respond quickly to technological developments and to incorporate new features into its products. The gross margin percentage could vary significantly from expectations based on capacity utilization; variations in inventory valuation, including variations related to the timing of qualifying products for sale; changes in revenue levels; segment product mix; the timing and execution of the manufacturing ramp and associated costs; start-up costs; excess or obsolete inventory; changes in unit costs; defects or disruptions in the supply of materials or resources; product manufacturing quality/yields; and impairments of long-lived assets, including manufacturing, assembly/test and intangible assets. Intel's results could be affected by adverse economic, social, political and physical/infrastructure conditions in countries where Intel, its customers or its suppliers operate, including military conflict and other security risks, natural disasters, infrastructure disruptions, health concerns and fluctuations in currency exchange rates. Expenses, particularly certain marketing and compensation expenses, as well as restructuring and asset impairment charges, vary depending on the level of demand for Intel's products and the level of revenue and profits. Intel’s results could be affected by the timing of closing of acquisitions and divestitures. Intel's results could be affected by adverse effects associated with product defects and errata (deviations from published specifications), and by litigation or regulatory matters involving intellectual property, stockholder, consumer, antitrust, disclosure and other issues, such as the litigation and regulatory matters described in Intel's SEC reports. An unfavorable ruling could include monetary damages or an injunction prohibiting Intel from manufacturing or selling one or more products, precluding particular business practices, impacting Intel’s ability to design its products, or requiring other remedies such as compulsory licensing of intellectual property. A detailed discussion of these and other factors that could affect Intel’s results is included in Intel’s SEC filings, including the company’s most recent reports on Form 10-Q, Form 10-K and earnings release.

Risk Factors

3

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

DWA Character with Skin Deformation

4

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

The Algorithm

Vectorization– Basic techniques

– SBB Integration

– Indirect Access

– Data padding

– Manage uniform data

Results

Summary

How we got 4x SIMD speedup

5

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Skin Deformation Videos

6

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

DWA’s largest and most complex deformation kernel

C++ Object-Oriented– Up to 3 levels of indirect access

Loop body– Many levels of nested function calls– Multiple source files across multiple libraries– 8625 instructions executed per iteration

Double-precision math Parallel, but no SIMD

Skin Deformation Algorithm - Overview

7

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

8

Motion System Skin Deformation

Hierarchy Joints Control Points Curve,Offsets,

& Attachment Bindings

Skin MeshAttachments boundto Skin Vertices

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Compute deformed vertex positions and offsets of skin mesh– Control Points are on a curve

Curve driven by character’s motion system

– Each vertex Attachment 1-4 “Control Point(s)”

– Shared (e.g. 3 out of 4)

Weights, offsets, scales, …

Skin Deformation Algorithm - Detail

0 1 2 3 2 3 4 51 2 3 4

Control Points (Curve)

Skin Mesh

Attachment

0

12

34

5

9

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

SIMD instructions – Can process multiple data lanes in a single

operation

One vector register can hold multiple data values– SSE4 : 128-bit

2 doubles or 4 floats

– AVX : 256-bit 4 doubles or 8 floats

Vector operations compute math (+, -, *, /) on all of data lanes at the same time

SIMD = Single Instruction Multiple Data

vector_register_10 1 2 3

vector_register_20 1 2 3

Step 4vector_register_10 1 2 3

SIMD += operation

vr1[0]+=vr2[0]

vr1[1]+=vr2[1]

vr1[2]+=vr2[2]vr1[3]+=vr2[3]

10

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

No function calls

– Inlined all calls made from loop body (i.e. “inline” keyword)

– Removed non-inlineable calls (e.g. print statements)

– “#pragma inline recursive” scoping entire loop body

Single entry, single exit

– Removed data-dependent exit conditions (e.g. early outs)

– Removed exception throwing

Intel® C++ Composer XE (ICC) Vectorization

11

https://software.intel.com/sites/default/files/8c/a9/CompilerAutovectorizationGuide.pdf

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Straight-line code Removed conditionals

– No “switch” statements

– “if” statements supported (as masked or blended assignments) But best to avoid

Created templatized inlined functions– To handle conditionals at compile time

– Branch outside loop instead of at each iteration

ICC Vectorization (Part 2)

12

Code example on next slide

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Templates to avoid conditionals inside loopvoid compute() {

switch (mAlgorithm->mVersion){case 0:

computeHelper<0>(); break;case 1:

computeHelper<1>(); break;default:};

}

template<int VersionT>void computeHelper() {

for (int i = 0; i<mCount; ++i) {mAlgorithm->computePosition<VersionT>(data[i]);

}}

template<int VersionT>inline void computePosition(Data d) {

if (VersionT < 1) {// support older version

} else {// run newer version of algorithm

}}

void compute() {for (int i=0; i<mCount; ++i) {

mAlgorithm->computePosition(data[i]);}

}

void computePosition(Data d) {if (this->mVersion < 1) {

// support older version} else {

// run newer version of algorithm}

}13

Converted “Version” to template argument VersionT

Dead code elimination will remove one of these branches at compile time

“VersionT” (known at compile time) creates separate code paths

Hoisted conditional to outside loop

Main Loop

Loop Body

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

SIMD Building Blocks (SBB)

C++ template library

Abstracts out aspects of creating an efficient data parallel (SIMD + threading) program– Via concepts of Containers, Accessors, Kernels, and Engines

– Helps avoid common pitfalls of writing efficient SIMD code

Compatibility– Compatible with Intel® Threading Building Blocks (TBB) and

OpenMP*

– Generates correct code with a C++11 compiler

What is SBB?

14

Developed by Alex Wells ([email protected])

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Let compiler (ICC) handle privatization of local variables in a SIMD loop– Each SIMD lane gets a private instance of the variable

“SBB Primitives” restrict objects to help the compiler succeed in privatization– Plain Old Data

– Inlined object members

– No nested arrays in objects

– No virtual functions

Follow SBB’s Vectorization Strategy

15

Code example on next slide

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Converting to a SBB Primitive (Example)

class Vec3 {//...double length();

double v[3];//...

};

class Vec3 {//...inline double length();

double x;double y;double z;//...

};

Individual data members

16

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

ICC optimization report on vectorization– Compile with flag: “-qopt-report=5 -qopt-report-phase=vec”

– Provides per loop summary of vectorization and estimated performance impact

– Helps isolate what prevented vectorization of a loop

Intel® VTune™ Amplifier XE– Analyzed performance (used Task API)

– Inspected assembly that actually executes

Useful Tools

17

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

ICC compiler tells us…

– “Could vectorize but may be inefficient”

Successfully forced vectorization with #pragma simd

– Actual runtime showed essentially no improvement

Opt-report

– “Estimates” a slowdown

Needed investigate into why

“Could vectorize but may be inefficient”

18

Use Opt-Report to investigate obstacles to efficient SIMD code

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Indirect memory addressing– Gather : indexed reads (“loads”)

– Scatter : indexed writes (“stores”)

Gathers or scatters can degrade SIMD performance

We want to avoid indirect accesses

So, is there any loop-invariant data that we can treat as uniform across loop?

Opt-report littered w/ “indirect access” remarks

// Gatherfor (i = 0; i<N; ++i)

x[i] = y[idx[i]];

// Scatterfor (i = 0; i<N; ++i)

y[idx[i]] = x[i];

19

Loop index is used to look up another index

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Most data is accessed via ControlPoint index

– Up to 3 levels of indirection

– Causing chains of gathers

Can we refactor algorithm such that ControlPoint indices would be loop invariant?

Algorithm Has Too Many Indirections

AttachmentData array

ControlPoint array

XformData array

Matrix3, Vec3, double, int, …XformData

i

j

k

20

Example on next slide

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

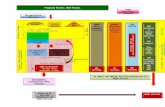

Sort, Hoist Uniform Data, & Sub-Loop

21

Original AttachmentsNo uniformity

0 1 2 3

2 3 4 5

2 3 4 5

2 3 4 5

1 2 3 4

0 1 2 3

1 2 3 4

0 1 2 3

0 1 2 3

0

1

2

8

Trip count = 9

Sorted: Each sub-loop has uniform ControlPoints.

Sub-loop #3Uniform: (2,3,4,5)

2 3 4 5

2 3 4 5

8

6

0 1 2 3

0 1 2 3

0 1 2 3

0 1 2 3

0

1

2

Sub-loop #1Uniform: (0,1,2,3)

3

1 2 3 4

1 2 3 4 Sub-loop #2Uniform: (1,2,3,4)

5

4

Control Point Indexes

2 3 4 57

6

3

5

4

7

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Introduced data sorting…

– To break up Attachments into many sub-loops, Each with uniform set of ControlPoints

– Vectorize over each sub-loop Eliminating many indirect accesses

Attachment data is non-changing

– So only have to do sort once

Algorithm with uniform ControlPoints

Pull loop-invariant data outside loop

22

Code example on next slide

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Hoisting ControlPoints outside loop (Example)

// Vectorized loopfor (int i = 0; i < count; i++){

AttachmentData& a = mAttachments[i];ControlPoint& cp0 = mControlPoints[a.index0];ControlPoint& cp1 = mControlPoints[a.index1];ControlPoint& cp2 = mControlPoints[a.index2];ControlPoint& cp3 = mControlPoints[a.index3];

computePosition(a, cp0, cp1, cp2, cp3);}

for (int i = ; i < mSubLoops.count; i++){

SubLoop& ss = mSubLoops[i];ControlPoint& cp0 = mControlPoints[ss.index0];ControlPoint& cp1 = mControlPoints[ss.index1];ControlPoint& cp2 = mControlPoints[ss.index2];ControlPoint& cp3 = mControlPoints[ss.index3];

// Vectorized sub-loop over Attachments with// loop-invariant ControlPointsfor (int j = ss.begin; j < ss.end; j++) {

AttachmentData& a = mAttachments[j];computePosition(a, cp0, cp1, cp2, cp3);

}}

Loop over unsorted Attachments

1. Added sub-loop2. Hoisted ControlPoints outside vectorized sub-loop

23

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Resolved all “indirect access” remarks

– No more gather instructions

Impact of Uniform ControlPoints

Mine input data for Uniformity

XformData array

XformData

ControlPoint

Matrix3, Vec3, double, int, …

Set of (1-4) ControlPoint’sare uniform over loop

24

2x Speedup (AVX)

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Main SIMD loop always starts and ends on SIMD boundaries– Processes N SIMD Lane Count (e.g. 4 doubles) iterations at a time

Peel loop - any iterations up to before first SIMD boundary

Remainder loop - any iterations from after the last SIMD boundary to the end of the iteration space

Anatomy of a SIMD Loop

25

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

Loop from 3 through 18

Peel Loop(scalar)

Remainder Loop(scalar or masked SIMD)

Main SIMD Loop

Example of 4 Vector Lanes

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

VTune Shows Execution TimeScreenshot from Intel® VTune Amplifier XE

26

Main Loop (vectorized)

Remainder Loop

Peel Loop

Blue marks alongside scrollbar

indicate where execution time is spent in assembly

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Investigated trip counts of the sub-loops

And observed short trip counts

– We had 4 to 32 or more iterations

– Enough to cover vectorization

Start and end of iteration space of sub-loops did not align with SIMD lane boundaries

– Spending over 35% in Peel and Remainder loops

Short Trip Counts

27

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Added padded entries into our input data stream

Ensured iterations started and ended on a SIMD lane boundary

– 2 (SSE4.2), 4 (AVX)

– Attachment data is non-changing, so only have to do padding once

For padded entries, just repeat work

– Scatter result to same output address

Implemented data padding

28

Example on next slide

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Padded Attachments

0 1 2 3

0 1 2 3

0 1 2 3

0 1 2 3

1 2 3 4

1 2 3 4

0

1

2

1 2 3 4

0 1 2 3

0 1 2 3

8

Not padded

Sub-loop #1Trip count = 6

Sub-loop #2Trip count = 3

0 1 2 3

0 1 2 3

0 1 2 3

0 1 2 3

1 2 3 4

1 2 3 4

0

1

2

1 2 3 4

1 2 3 4

0 1 2 3

0 1 2 3

0 1 2 3

0 1 2 3

3

4

5

6

7

8

9

10

11

Padded to 4 data lanes

Sub-loop #1 Trip count = 8

Sub-loop #2 Trip count = 4

Padded Entries

Control PointIndexes

29

3

4

5

6

7

Main SIMD Loop

Remainder Loop

Peel Loop

Example of 4 Vector Lanes

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Execution Time : Not Padded vs. Padded

Screenshots from Intel® VTune Amplifier XE

30

PaddedNot Padded

All time spentin Main SIMDLoop

Blue marks alongside scrollbar indicates

where executed time is spent in assembly

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Allowed all of the time to be spent in our aligned vectorized code

Speedup overcame the processing overhead of padded data

Data Padding Impact

Pad data to align with SIMD lane boundaries

31

14% more speedup

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

After padding, compiler (icc14) chose to unroll our vectorized AVX loop

– Caused it to iterate by 8 element rather than 4

Since our we are padding to boundary of 4

– Once again, spending time in the peel and remainder loops

Resolved by explicitly setting SIMD length

– #pragma simd vectorlength(4)

Encountered obstacle to padding

Avoid surprises. Explicitly set vector length.

32

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Inspecting assembly (VTune), we noticed room for improvement

Data is uniform for entire loop,

– But is still accessed via indirection at each loop iteration

So we refactored algorithm to manually manage allindirect accesses (from ControlPoint indexes) outside of loop

– Pre-populate all indirect data into uniform data structure

Uniform Indirection Overhead

33

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Before entering a SIMD loop– For each uniform value the compiler may

Load scalar value into register

Broadcast scalar value in register to all lanes of SIMD register

Store SIMD register to new location on stack for use inside the SIMD loop body

– Multiply overhead by up to 59 doubles per Control Point

For long trip counts, overhead easily amortized

– But short trip counts can not

Overhead of Uniform Data in SIMD Loops

34

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

sbb::UniformSoaOver1d

– Store loop invariant data in a SIMD ready format

SIMD loops can directly access the data without conversion

– Decouples SIMD conversion overhead from the loop

Puts user in control of when to incur the overhead

– Over multiple sub-loops

Enables partial updates of Uniform Data

Enables reuse of Uniform Data

Uniform Data & SBB

35

Example on next slide

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Partial Updating of Uniform data

0 1 2 3

0 1 2 3

0 1 2 3

0 1 2 3

1 2 3 4

1 2 3 4

0

1

2

1 2 3 4

1 2 3 4

3

4

5

6

7

Loop #1 : Load uniform data for ControlPoints (0,1,2,3)

Loop #2 : Reuse uniform data for (1,2,3). Load (4).

2 3 4 5

2 3 4 5

2 3 4 5

2 3 4 5

8

9

10

11

Loop #3 : Reuse uniform data for (2,3,4). Load (5).

AttachmentIndexes

Control PointsSub-Loop #

36

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

From one sub-loop to the next, on average, we only update ¼ of the UniformData

– Save 75% of overhead involved in setting up uniform data

Impact of Managing Uniform Data

Explicitly manage uniform data

37

13% more speedup

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Performance data collected using VTune– CPU Time– Instructions Executed

Hardware: SandyBridge, Xeon (dual-socket, 16-core) Single-threaded execution Comparison definitions

– Baseline Original algorithm

– New algorithm Scalar - Vectorization disabled SIMD - Vectorization enabled

Results

38

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Results: Same Work, Less Instructions

39

8.5x improvement (AVX)

Lower is better

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Results: Algorithm Speedups

Higher is better

4.2x total speedup (AVX)

40

1.5x Scalar speedup

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Results: Do More in Less Time

41

SIMD,Double Resolution

Lower is better

Original algorithm,1x Vertices

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Biggest payoff was from eliminating all indirection

Padded data to align with SIMD lane boundaries

Explicitly managed and re-used uniform data

Summary

42

4.2x total speedup!

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Anson Chu : [email protected]

Alex Wells : [email protected]

For SBB inquiries, contact Alex!

Thank you!

43

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Optimization Notice

44

Optimization Notice

Intel® compilers, associated libraries and associated development tools may include or utilize options that optimize for instruction sets that are available in both Intel® and non-Intel microprocessors (for example SIMD instruction sets), but do not optimize equally for non-Intel microprocessors. In addition, certain compiler options for Intel compilers, including some that are not specific to Intel micro-architecture, are reserved for Intel microprocessors. For a detailed description of Intel compiler options, including the instruction sets and specific microprocessors they implicate, please refer to the “Intel® Compiler User and Reference Guides” under “Compiler Options." Many library routines that are part of Intel® compiler products are more highly optimized for Intel microprocessors than for other microprocessors. While the compilers and libraries in Intel® compiler products offer optimizations for both Intel and Intel-compatible microprocessors, depending on the options you select, your code and other factors, you likely will get extra performance on Intel microprocessors.

Intel® compilers, associated libraries and associated development tools may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include Intel®

Streaming SIMD Extensions 2 (Intel® SSE2), Intel® Streaming SIMD Extensions 3 (Intel® SSE3), and Supplemental Streaming SIMD Extensions 3 (Intel® SSSE3) instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors.

While Intel believes our compilers and libraries are excellent choices to assist in obtaining the best performance on Intel® and non-Intel microprocessors, Intel recommends that you evaluate other compilers and libraries to determine which best meet your requirements. We hope to win your business by striving to offer the best performance of any compiler or library; please let us know if you find we do not.

Notice revision #20101101

C o p y r i g h t © 2 0 1 5 , I n t e l C o r p o r a t i o n . A l l r i g h t s r e s e r v e d . * O t h e r n a me s a n d b r a n d s ma y b e c l a i me d a s t h e p r o p e r t y o f o t h e r s .

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Backup Slides

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Manually define copy constructor for objects

– Compiler had trouble with some objects

– Even though logically equivalent to compiler provided default

Allows privatization of local variable instances inside vector loop

Replaced ‘bool’ with ‘int’

– ‘bool’ is not supported for SIMD privatization

Opt-report “unsupported data type” remark

May need to manually define copy constructor

47

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

__builtin_expect

– Added to conditionals when control flow follows a known path

– Allows compiler to test all data lanes to see that the expression was zero and skip a code block

Faster than following a masked blended code path

– Used carefully, and verified doesn’t hurt performance

Other incremental improvements

48

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Okay to divide by zero

– Result will be NAN

Any subsequent operations with NAN, results in NAN

– Removed multiple conditional tests for zero when dividing

Continue computation

Test final result for NAN (if necessary)

– Hint: combine with ‘__builtin_expect’

Other incremental improvements (Part 2)

49

#define IS_NAN(val) \((val == val) == false)

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

If you store bool values as anything other than 32-bit, compiler needs to do extra work to test for true/false– In C++, a Boolean is:

False, when 0x0

True, when anything else

– But in SSE/AVX SIMD, True when 'high bit set‘

False otherwise

So we used int instead of bool– Tested explicitly against integer (0 or 1)

Other incremental improvements (Part 3)

50

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Let SBB Containers & Accessors…

– Automatically handle data transformation and alignment

Let SBB Engines…

– Handle loop iteration

Let SBB Primitive and underlying compiler (ICC)…

– Handle privatization of local variables in a SIMD loop

Such that a private instance exists for each SIMD lane

SBB Integration

51

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Converted data containers– sbb::Soa1dContainer (instead of std::vector) – Use SBB Accessors to read/write data from/to Containers

Converted algorithm loop– SBB Kernels

Define unit of work (i.e. loop body)

– SBB Engines Control code generation (e.g Scalar vs. Simd)

– Control peel or remainder loop generation– Set number of SIMD lanes

Control threading model (Single-threaded, TBB, OpenMP) and grain size.

SBB Integration – Containers, Kernels, Engines

52

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Converted objects in DWA’s 3D math library

– Meet SBB Primitive requirements

– Example:

SBB Integration

// Math library’s 3D Vectorclass Vec3 {

//...protected:

double v[3];//...

};

#include <SBB/Primitive.h>class Vec3 {

//...public:

double x;double y;double z;//...

};SBB_PRIMITIVE(Vec, x, y, z)

53

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

SBB Primitive Nesting(Example)

#include <SBB/Primitive.h>class Vec3 {public:double x;

double y;double z;

};SBB_PRIMITIVE(Vec3, x, y, z)

struct AttachmentData {double weight;math::Vec3 offset;double scale;…

};

SBB_PRIMITIVE(AttachmentData,weight,offset,scale,…);

Primitives can be nested

54

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Provides familiarity of AOS Object-Oriented programming,

– But stores data in SIMD efficient format internally (e.g. SOA)

– API similar to std::vector<Struct>

Used sbb::Soa1dContainer

SBB Integration: Container

class AttachmentPartition{

// Array of structures (AOS)std::vector<Attachment> mData;

}

class AttachmentPartition{

// Easily switch between types of memory layout//typedef sbb::Aos1dContainer<Attachment> SbbContainer;typedef sbb::Soa1dContainer<Attachment> SbbContainer;

SbbContainer mData;}

55

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Converted loop to SBB kernel

Use SBB Accessors

– To read/write data from/to Containers, from within loop

SBB Integration: Kernel and Accessors// SBB accessors to input and output arraysauto sbbInputs = mPartition.mData->access();sbb::Aos1dAccessor<AffectedPosition, sbb::AccessByStride>

sbbOutputs(&(mAffectedPositions.rawDataArray()[0]), mCount);

// Define SBB Kernel (loop body)SBB_KERNEL_BEGIN(kernel)

SBB_ITER_D1_BEGIN(index){

// Get SBB accessor to individual elementauto attachment = sbbInputs[index];

gmath::Vec3d affectedPos;affectedPos = mAlgorithm->computePosition(attachment);affectedPos *= attachment.weight();

sbbOutputs[index] = affectedPos;}SBB_ITER_END

SBB_KERNEL_END

auto is your SBB friend

56

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Used SBB Engine to…

Control code generation (e.g Scalar vs. Simd)

– Control peel or remainder loop generation

– Set number of SIMD lanes

Control threading model (and grain size)

– TBB, OpenMP, or single-threaded

[Example on next slide…]

SBB Integration: Engine

57

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

SBB Integration : Engine (example)

SBB_KERNEL_BEGIN(loop)…

SBB_KERNEL_END

// SBB Enginesbb::Block1dBounds bounds(0, count);sbb::Block1dSize blockSize(16);Engine engine;engine.run(loop, bounds, blockSize);

// Easily switch between Code Strategy (i.e. SIMD vs. non-SIMD)typedef sbb::SimdCode<SimdLaneCount, sbb::BoundsAreSimdAlignedYes> CodeGen;//typedef sbb::VectorCode<SimdLaneCount, sbb::BoundsAreSimdAlignedYes> CodeGen;//typedef sbb::ScalarCode<SimdLaneCount, sbb::BoundsAreSimdAlignedYes> CodeGen;

// Easily switch between SBB Enginestypedef sbb::Tbb1dEngine<CodeGen> Engine;//typedef sbb::SingleThreaded1dEngine<CodeGen> Engine;

typedef’s are useful for debugging and performance tuning

58

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Array of Structures (AOS)– Ex. std::vector<gmath::Vec3d> A

– Multiple (load, shuffles, or gather) instructions to get data into a vector register

– Possibly access multiple cache lines

Structures of Arrays (SOA)– Ex. struct A {double x[N], y[N], z[N]}

– All ‘x’ is adjacent in memory

– Often, single vector load instruction

AOS vs. SOA

X

A[i+0]

Y Z X

A[i+1]

Y Z X

A[i+2]

Y Z X

A[i+3]

Y Z

vector_register_10 1 2 3

AOS in Memory Layout

vector_register_10 1 2 3

A

Z[i+0] Z[i+1] Z[i+2] Z[i+3]

Y[i+0] Y[i+1] Y[i+2] Y[i+3]

X[i+0] X[i+1] X[i+2] X[i+3]

SOA in Memory Layout

59

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Definitely, improves assembly inside a vectorized loop

But, there’s a cost to adding a separate AOS to SOA conversion

– Would likely eat up any improvements

– Could be worth it,

If data is accessed multiple times or by a multi-pass algorithm

Ideally, avoid doing any conversion

– Keep the data as SOA the entire time

Is converting to SOA worthwhile?

60

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Intel® C++ Composer XE (ICC) can generate SIMD code for us implicitly or explicitly:

– Implicit

Compiler decides its safe to do so and just does it

aka “auto-vectorization”

– Explicit

Programmer declares its safe and/or worthwhile

Ex. “#pragma simd”

Intel® C++ Composer XE (ICC) : Vectorization

61

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Find and replace ‘size_t’ with ‘int’

– Help avoid 64-bit indexes

– Got rid of “64bit indexed” remarks for a single level of indirection

Resolved opt-report “64bit indexed” remarks

62

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Results: Vectorization Efficiency

AVX (scalar & vector) gains efficiency due to 3 operand instructions, so more work represented in fewer instructions

Higher is better

63

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Results: SIMD Speedups

Higher is better

64

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

ICC opt-report

– Diagnostic messages do not always report exact culprit or line number

– Errors and remarks are sometimes vague and ambiguous

– But, ICC continues to improve this in newer versions

Inlined code from several different files

– So it was guesswork, looking at line number of each file for suspect code

Difficulties

65

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Inlining code can change execution order of math operations – Still correct, but results may differ

Due to floating point rounding differences

Bloated compile time– Enormous size of inlined loop body (likely uncommon)

– Workaround was to separate our several variations of loop into multiple compilation units, to allow parallel compilation

Intel® Advisor XE 2016 with Vectorization Advisor– Was not available at the time

– May have been useful tool for vectorization of this algorithm

Difficulties (Part 2)

66

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

Try various instruction sets (SSE4.2, AVX, AVX2).

– May get additional diagnostics

– e.g. AVX2 reported “indirect access” and “64bit indexed” remarks

Try both ‘#pragma simd’ and ‘#pragma vector’ with opt-report’s

– ‘#pragma ivdep’ with ‘#pragma vector’ proved more useful than ‘#pragma simd’

Things To Try When Vectorizing

67

Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.Copyright © 2015, Intel Corporat ion. Al l r ights reserv ed. *Other names and brands may be claimed as the property of others.

68

Try different compiler versions

– ICC 15 improved formatting over ICC 14

– And sometimes more useful information

If line numbers are vague from opt-report

– Try commenting out lines to isolate culprit line number

– Try commenting out code blocks until it works

E.g. binary search strategy

Things to try when vectorizing (Part 2)