Double Gate Mos

description

Transcript of Double Gate Mos

-

Under the guidance of Seminar Topic by S.R.P Sinha Daya Nand GuptaAssociate Professor M.Tech Micro-electronics(ECE Department)III Sem

-

The number of transistors in a dense integrated circuit doubles approximately every 18 months.

-

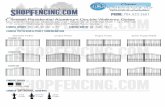

n-channel MOSFETSymbol of MOSFETDrain characteristics of n-channel MOS

-

When channel length decreases, roll-off in the value of VtTunneling through Gate oxide (off state current)Wastage area increases as density increases

-

By moving to DG MOSFETsBetter control of channel from the gatesReduced short-channel effectsBetter Ion /Ioff Improved (low) sub-threshold slope (60mV/decade)

-

Fig.: DGT is comprised of a conducting channel (usually un-doped), surrounded by gate electrodes on either side.

-

The voltage applied on the gate terminals controls the electric field, determining the amount of current flow through the channel. The most common mode of operation is to switch both gates simultaneously.Another mode is to switch only one gate and apply a bias to the second gate (this is called ground plane (GP) or back-gate (BG))GENERAL DGT OPERATIONSFig: DGT operations

-

Different structuresSymmetrical and AsymmetricalFig. Symmetric and Asymmetric structure

-

Fig: Symmetrical DGFET (Work Function)Fig. Asymmetrical DGFET (Work Function)

-

DGT Design Objectives

Reduction of short channel effects (SCEs) -Decreased VT due to reduced channel depletion chargeMaintaining good electrical characteristics -High Ion/Ioff ratio -Sharp I-V slope -Keeping fabrication process simple

-

It is an effect whereby a MOSFET in which the channel length is the same order of magnitude as the depletion layer widths of source & drain junctions, behaves differently from the other MOSFETs.

As the channel length L is reduced to increase both the operation speed and the number of components per chip, the so called SCE occurs

Fig- Short channel effect in MOSFETS

-

Drain-induced barrier loweringorDIBLis ashort-channel effectinMOSFETsreferring originally to a reduction ofthreshold voltageof thetransistorat higher drain voltages.Thus increased in Ioff Fig-DIBL in MOSFETS

-

Ioff is defined as the drain current at Vgs = 0 V and Vds = Vdd. Ideally, Ioff = 0By placing a second gate on the opposite side of the device, the gate capacitance of the channel is doubled and the channel potential is better controlled by the gate electrode, thus limiting Ioff.

-

Reduced channel and gate leakage

Short channel effects are seen in standard silicon MOS devicesDGFET offers greater control of channel because of double gate Gate leakage current is prevented by a thick gate oxide

-

Silicon MOS Transistor Increased body doping used to control VT for short channelSmall number of dopant atoms for very short channelLowest VT achievable is 0.5 V

Double Gate FET Increased body dopingAsymmetric gate work functions (n+ /p+ gates)VT of .1 V achievable through work function engineering

-

Increase Carrier MobilitySilicon MOS Transistor Carrier scattering from increased body doping Transverse electric fields from the source and drain reduce mobilityDouble Gate FET Lightly doped channel in a DGFET results in a negligible depletion charge Asymmetrical gate experiences some transverse electric fields

-

Reduced Power Consumption

Double gate coupling allows for higher drive currents at lower supply voltage and threshold voltageEnergy is quadratic function of supplyReduced channel and gate leakage currents in off state translate to huge power savingsSeparate control of each gate allows dynamic control of VT

-

Reduction of off current Ioff , higher Ion currentUn-doped channel eliminates intrinsic parameter fluctuations and minimizes impurity scattering.Double gate allows for higher current drive capabilityBetter control of short channel effectsLower sub-threshold currentLower gate leakage

-

Scaling trend in CMOS approaching physical limits prompts the need for alternative device structures, such as DGT.DGT is more robust to SCE, such as Ioff.Major design challenge consists of achieving good VT control, while keeping low Rseries.Several structures have been proposed: planar, vertical, and DG-FETDGFET structure is so far the most promising.Still major challenges remain ahead, specially issues related to fabrication.