Digital Electronics Lab (17ECL38) 2018-19To add four bits need four full adders arranged in...

Transcript of Digital Electronics Lab (17ECL38) 2018-19To add four bits need four full adders arranged in...

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 1

Verification:

1)

2)

A B A.B A.B

0 0 0 1

0 1 0 1

1 0 0 1

1 1 1 0

A B A B A + B

0 0 1 1 1

0 1 1 0 1

1 0 0 1 1

1 1 0 0 0

A B A+B A+B

0 0 0 1

0 1 1 0

1 0 1 0

1 1 1 0

A B A B A . B

0 0 1 1 1

0 1 1 0 0

1 0 0 1 0

1 1 0 0 0

A+B = A . B

A.B = A + B

7404

7404

7404

7404

7404

7404

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 2

Experiment No: 1(A) Date:

Demorgan’s Theorem for 2 variables

Aim: To verify Demorgan’s theorem for 2 variables

Components required: IC7404, 7432, 7408, Digital IC Trainer Kit, Patch

cords

Theory:-

Theorem 1:

The compliment of the product of two variables is equal to the sum of the

compliment of each variable. Thus according to De-Morgan’s laws or De-

Morgan's theorem if A and B are the two variables or Boolean numbers.

Then accordingly,

Theorem 2:

The compliment of the sum of two variables is equal to the product of the

compliment of each variable. Thus according to De Morgan’s theorem if A

and B are the two variables then,

De-Morgan's laws can also be implemented in Boolean algebra in the

following steps:-

1. While doing Boolean algebra at first replace the given operator.

That is (+) is replaced with (.) and (.) is replaced with (+).

2. Compliment of each of the term is to be found.

Procedure:

1. Realize the Demorgans theorem using logic gates.

2. Connect VCC and ground as shown in the pin diagram.

3. Make connections as per the logic gate diagram.

4. Apply the different combinations of input according to the truth tables.

Verify that the results are correct.

A.B = A + B

A+B = A . B

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 3

Given problem:

Truth table: Switching Expressions

A B C D Y Y= f(A,B,C,D)=Σm(5,6,7,13,14,15)

0 0 0 0 0 Y= f(A,B,C,D)=ΠM(0,1,2,3,4,8,9,10,11,12)

0 0 0 1 0

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 1

0 1 1 0 1

0 1 1 1 1

1 0 0 0 0

1 0 0 1 0

1 0 1 0 0

1 0 1 1 0

1 1 0 0 0

1 1 0 1 1

1 1 1 0 1

1 1 1 1 1

K-map Simplification:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 4

Experiment No: 1(B) Date:

Sum of Product and Product of Sum

Aim: To design sum-of product and product-of-sum expressions using Basic

gates and Universal gates.

Components Required: IC 7408 (AND), IC 7404 (NOT), IC 7432 (OR), IC

7400(NAND), IC 7402 (NOR), IC 7486 (EX-OR), IC Trainer Kit, Patch cords

Theory:

Canonical Forms (Normal Forms): Any Boolean function can be

written in disjunctive normal form (sum of min-terms) or conjunctive

normal form (product of max-terms).A Boolean function can be

represented by a Karnaugh map in which each cell corresponds to two

minterm. Sum of minterms : Sum Of Product (SOP) Product of maxterms : Product Of Sum (POS) Procedure: 1. Verify that the gates are working.

2. Construct a truth table for the given problem.

3. Draw a Karnaugh Map corresponding to the given truth table.

4. Simplify the given Boolean expression manually using the Karnaugh Map.

A. Implementation Using Logic Gates: 5. Realize the simplified expression using logic gates.

6. Connect VCC and ground as shown in the pin diagram.

7. Make connections as per the logic gate diagram.

8. Apply the different combinations of input according to the truth tables.

Verify that the results are correct.

B. Implementation Using Universal Gates:

1. Convert the AND-OR logic into NAND-NAND and NOR-NOR logic.

2. Realize the simplified Boolean expressions using only NAND gates, and

then using only NOR gates.

3. Connect the circuits according to the circuit diagrams, apply inputs

according to the truth table and verify the results.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 5

Simplified Boolean expression:

(i) Simplification using Basic Gates:

(ii) Simplification using NAND Gate:

(iii) Simplification using NOR Gate:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 7

1. Half Adder

Truth Table:

A B S C

0 0 0 0 S =AB

0 1 1 0

C = A.B

1 0 1 0

1 1 0 1

Realization of Half Adder:

i). Using Basic gates

ii). Using NAND gates

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 8

Experiment No: 2 Date:

ADDERS AND SUBTRACTORS Aim:(i) To realize half/full adder using Logic gates & NAND gates

(ii) To realize half/full Subtractor using Logic gates & NAND gates Components Required: IC 7408, IC 7432, IC 7486, IC 7404, IC 7400, Patch cords Theory: Half-Adder: A combinational logic circuit that performs the addition of two

data bits, A and B, is called a half-adder. Addition will result in two output

bits; one of which is the sum bit S, and the other is the carry bit, C. The

Boolean functions describing the half-adder are: S =AB

C = A.B Full-Adder: The half-adder does not take the carry bit from its previous

stage into account. This carry bit from its previous stage is called carry-in

bit. A combinational logic circuit that adds two data bits, A and B, and a

carry-in bit, Cin , is called a full-adder. The Boolean functions describing

the full-adder are:

S = A B Cin

C = A.B+ Cin (A B) Half Subtractor: Subtracting a single-bit binary value B from another A

(i.e. A-B) produces a difference bit D and a borrow out bit Br. This operation

is called half subtraction and the circuit to realize it is called a half

subtractor. The Boolean functions describing the half-Subtractor are:

D =A B

Br= A’.B Full Subtractor: Subtracting two single-bit binary values, B, Cin from a

single-bit value A produces a difference bit D and a borrow out Br bit. This

is called full subtraction. The Boolean functions describing the full-

subtractor are:

D = A B Cin

Br= A’.B + A’ .Cin + B . Cin

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 9

2. Full Adder

Truth Table:

A B Cin S C

0 0 0 0 0

0 0 1 1 0 S = A B Cin

0 1 0 1 0 C = A.B+ Cin (A B)

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Realization of Full Adder:

(i) Using logic gates

(ii) Using Nand gates

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 10

Procedure:

1. Verify for working of the gates.

2. Make the connections as per the circuit diagram for the half adder circuit, on the trainer kit.

3. Switch on the VCC power supply and apply the various combinations

of the inputs according to the respective truth tables.

4. Verify that the outputs are according to the expected results.

5. Repeat the procedure for the full adder circuit, the half subtractor

and full subtractor circuits.

6. Verify that the sum/difference and carry/borrow bits are according to

the expected values.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 11

3. Half Subtractor

Truth Table:

Realization of Half Subtractor:

(i) Using logic gates

ii) Using NAND gates

A B D Br

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

D =AB

Br = A.B

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 12

4. Full Subtractor

Truth Table:

A B Cin D Br

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

D = A B Cin

0 1 1 0 1

Br= A’.B + A’.Cin + B.Cin

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

Realization of Full Subtractor:

(i) Using logic gates:

(ii) Using NAND gates

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 13

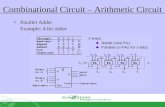

1. 4-BIT BINARY ADDER

Example: 7+2=09 which is equal to (1001)2 • 7 is realized at A3 A2 A1 A0 = 0111 • 2 is realized at B3 B2 B1 B0 = 0010

Sum = (1001)2 Circuit diagram:

MSB LSB

INPUTS Cin

A3 A2 A1 A0

B3 B2 B1 B0

OUTPUT Cout S3 S2 S1 S0

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 14

Experiment No: 3 Date:

PARALLEL ADDER AND SUBTRACTOR USING 7483

Aim: To design and set up the following circuit using IC 7483.

i) A 4-bit binary parallel adder.

ii) A 4-bit binary parallel subtractor.

Components Required: IC 7483, IC 7486, Patch Cords etc. Theory:

The Full adder can add single-digit binary numbers and carries. The

largest sum that can be obtained using a full adder is (11)2. Parallel adders

can add multiple-digit numbers. If full adders are placed in parallel, we can

add two- or four-digit numbers or any other size desired. Figure below uses

STANDARD SYMBOLS to show a parallel adder capable of adding two digit

binary numbers. The addend would be input on the A inputs (A2 = MSD,

A1 = LSD), and the augend input on the B inputs (B2 = MSD, B1 = LSD).

To add four bits need four full adders arranged in parallel. IC 7483 is a 4-

bit parallel adder is used.

Procedure for Adding two 4-Bit data:

1. Check all the components for their working. 2. Insert the appropriate IC into the IC base. 3. Make connections as shown in the circuit diagram. 4. Apply augend and addend bits on A and B and cin=0. 5. Verify the results and observe the output of ADDER CIRCUIT

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 15

2. 4-Bit Binary Subtractor.

(i) 4 bit subtraction operation using 7483 for A>B and Cin=1

Example: 8 – 3 = 5 which is equal to (0101)2

• 8 is realized at A3 A2 A1 A0 = 1000

• 3 is realized at B3 B2 B1 B0 through X-OR gates = 0011

• Output of X-OR gate is 1’s complement = 1100

• 2’s Complement can be obtained by adding Cin = 1

Therefore Cin =1

A3 A2 A1 A0 = 1 0 0 0

B3 B2 B1 B0 = 1 1 0 0

S3 S2 S1 S0 = 0 1 0 1 Cout = 1 (Ignored)

(ii) 4 bit subtraction operation using 7483 for A<B and Cin=1

Example: 14 – 15 = -1 (1111)2

• 14 is realized at A3 A2 A1 A0 = 1110

• 15 is realized at B3 B2 B1 B0 through X-OR gates = 1111

• Output of X-OR gate is 1’s complement of 15 = 0000

• 2’s Complement can be obtained by adding Cin = 1

Therefore Cin = 1

A3 A2 A1 A0 = 1 1 1 0

B3 B2 B1 B0 = 0 0 0 0

S3 S2 S1 S0 = 1 1 1 1

Since the most significant bit of the result is 1, this is a negative number, so form the two's complement of (1111)=-(0001)2

Circuit diagram:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 16

Procedure for subtracting two 4-Bit data:

1. Check all the components for their working. 2. Insert the appropriate IC into the IC base. 3. Make connections as shown in the circuit diagram. 4. Apply Minuend and subtrahend bits on A and B and cin=1. 5. Verify the results and observe the outputs.

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 17

5-Bit Comparator

Truth Table:

A4 A3 A2 A1 A0 B4 B3 B2 B1 B0 A>B A<B A=B

1 0 0 0 0 0 0 0 0 1 1 0 0

0 1 0 0 0 1 0 0 0 0 0 1 0

0 0 1 1 0 0 0 1 1 0 0 0 1

Circuit diagram:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 18

Experiment No: 4 Date:

COMPARATOR Aim: To realize 5 Bit magnitude comparator using IC 7485.

Components required: IC 7485, Patch Cords & IC Trainer Kit. Theory:

Magnitude Comparator is a logical circuit, which compares two

signals A and B and generates three logical outputs, whether A > B, A = B,

or A < B. IC 7485 is a high speed 4-bit Magnitude comparator, which

compares two 4-bit words. The A = B Input must be held high for proper

compare operation.

Procedure:

1. Check all the components for their working. 2. Insert the appropriate IC into the IC base. 3. Make connections as shown in the circuit diagram.

4. Apply 0 for the bits A5, A6, A7, B5, B6, B7 OR ground them.

5. Apply given data to the rest of the bits.

6. Verify the results and observe the outputs. Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 19

A. Adder & Subtractor using IC 74153 (i) Half Adder:

Truth Table: Circuit diagram:

(ii)Full Adder:

Truth Table: Circuit diagram:

A B Cin S C

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

A B S C

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 20

Experiment No: 5(a) Date:

REALIZATION OF ADDER AND SUBTRACTOR USING IC 74153

Aim: To design adder and subtractor using IC 74153 Components Required: IC 74153, Patch Cords & IC Trainer Kit.

Theory:

Multiplexers are very useful components in digital systems. They

transfer a large number of information units over a smaller number of

channels, (usually one channel) under the control of selection signals. Multiplexer means many to one. A multiplexer is a circuit with many inputs

but only one output. By using control signals (select lines) we can select any

input to the output. Multiplexer is also called as data selector because the

output bit depends on the input data bit that is selected. The general

multiplexer circuit has 2n input signals, n control/select signals and 1

output signal. Procedure: 1. The connection is made as shown in the diagram.

2. Here, S1 and S0 are the channel selection lines,I0, I1, I2, I3 are the

respective data lines of the channels and Y is the output.

3. Based on the selection lines one of the inputs will be selected at the

output, and thus the truth table is verified.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 21

(iii) Half Subtractor: Truth Table: Circuit diagram:

(iv) Full Subtractor:

Truth Table: Circuit diagram:

A B D Br

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

A B Bin D Br

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

0 1 1 0 1

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 23

B. 3 Variable function using IC 74151

Truth table:

Select Lines Output

C B A Y

0 0 0 0

0 0 1 1

0 1 0 1

0 1 1 0

1 0 0 0

1 0 1 0

1 1 0 0

1 1 1 1

+Vcc

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 24

Experiment No: 5(b) Date:

REALIZATION OF 3 VARIABLE FUNCTION USING IC 74151

(8:1 MUX)

Aim: To design and set up the following circuit

3 variable function using IC 74151 (8:1 MUX)

Components Required: IC74151, Patch Cords & IC Trainer Kit.

Procedure: 1. For the given expression, a truth table is to be written.

2. An expression in SOP format is to be written.

3. The connection is made according to the obtained expression.

4. The truth table is verified for that particular expression.

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 25

Realize a Boolean expression using decoder IC 74139

Truth table:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 26

Experiment No: 6 Date:

REALIZE A BOOLEAN EXPRESSION USING DECODER

IC 74139

Aim: To realize a Boolean expression using decoder IC 74139

Components Required: IC74139, Patch Cords & IC Trainer Kit.

Theory:

A decoder is a combinational circuit that connects the binary information

from “n” input lines to a maximum of 2n unique output lines. Decoder is

also called a min-term generator/maxterm generator. A min-term generator

is constructed using AND and NOT gates. The appropriate output is

indicated by logic 1 (positive logic). Max-term generator is constructed using

NAND gates. The appropriate output is indicated by logic 0 (Negative logic).

The IC 74139 accepts two binary inputs and when enable provides 4

individual active low outputs. The device has 2 enable inputs (Two active

low).

Procedure: 1. For the given Boolean expression, a truth table is to be written.

2. An expression in SOP format is to be written.

3. The connection is made according to the obtained expression.

4. The truth table is verified for that particular expression.

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 27

1. J-K MASTER FLIPFLOP:

Truth Table:

Circuit diagram:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 28

Experiment No: 7 Date:

FLIP FLOPS Aim: To realize the following Flip-flops using NAND gates:

Master slave JK , D and T Flip-flops. Components required: IC 7410, IC7400, Patch Cords

Theory:

A flip-flop is a circuit that has two stable states and can be used to

store state information. A flip-flop is a bistable multivibrator. The circuit

can be made to change state by signals applied to one or more control

inputs and will have one or two outputs. It is the basic storage element in

sequential logic. Flip-flops and latches are a fundamental building block of

digital electronics systems used in computers, communications, and many

other types of systems.

A flip–flop is a “bit bucket”; it holds a single binary bit .Flip flops are

actually an application of logic gates. With the help of Boolean logic we can

create memory with them. Flip flops can also be considered as the most

basic idea of a Random Access Memory [RAM].

The most commonly used application of flip flops is in the

implementation of a feedback circuit. As a memory relies on the feedback

concept, flip flops can be used to design it.

Procedure:

1. Make the connections as shown in the circuit diagrams. 2. Apply inputs as shown in the truth tables,

3. Check the outputs of the circuits; verify that they match with the truth

tables.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 29

2. D – FLIPFLOP:

Truth Table:

Circuit diagram:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 30

3. T – FLIPFLOP:

Truth Table:

Circuit diagram:

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 31

1. SERIAL INPUT SERIAL OUTPUT (SISO): Procedure:

1. Connections are made as shown in the SISO circuit diagram. 2. Make sure the 7495 is operating in SISO mode by ensuring Pin 6 (Mode)

is set to LOW, and connect clock input to Clk 1(Pin 9).

3. The shift register is loaded with 4 bits of data one by one serially. 4. At the end of the 4thclock pulse, the first data ‘d0’ appears at QD.

5. Apply another clock pulse, to get the second data bit, ‘d1’ at QD. Applying yet another clock pulse gets the third data bit, ‘d2’ at QD, and so on.

Truth Table: Circuit diagram:

CLK Serial

I/P QA QB QC QD

1 do=0 0 X X X

2 d1=1 1 0 X X

3 d2=1 1 1 0 X

4 d3=1 1 1 1 0=do

5 X X 1 1 1=d1

6 X X X 1 1=d2

7 X X X X 1=d3

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 32

Experiment No: 8 Date:

SHIFT REGISTERS

Aim: To study IC 74S95, and the realization of Shift left, Shift right, SIPO,

SISO, PISO, PIPO operations using the same. Components required: IC 7495, patch cords etc. Theory:

• A shift register is a group of flip-flops (typically 4 or 8) that are

arranged so that the values stored in the flip-flops are shifted from

one flip-flop to the next for every clock.

• Shift registers are used extensively in logic circuits to control digital

displays.

• A classic example is numbers being typed into a calculator. As the

numbers are entered, the digits shift to the left one position. This

shifting is controlled by a shift register.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 33

2. SERIAL INPUT PARALLEL OUTPUT (SIPO/Right Shift): Procedure:

1. Connections are made as shown in the SISO circuit diagram.

2. Make sure the 7495 is operating in SIPO mode by ensuring Pin 6 (Mode) is set to LOW, and connect clock input to Clk 1(Pin 9).

3. Apply the first data at pin 1 (SD1) and apply one clock pulse. We observe that this data appears at pin 13 (QA).

4. Now, apply the second data at SD1. Apply a clock pulse. We now observe that the earlier data is shifted from QA to QB, and the new data appears at QA.

5. Repeat the earlier step to enter data, until all bits are entered one by one.

6. At the end of the 4th clock pulse, we notice that all 4 bits are available at the parallel output pins QA through QD.

Truth Table: Circuit diagram:

CLK Serial I/P

QA QB QC QD

1 1 1 X X X

2 0 0 1 X X

3 1 1 0 1 X

4 1 1 1 0 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 34

3. SERIAL INPUT PARALLEL OUTPUT (SIPO/Left Shift): Procedure: 1. Connections are made as shown in the SISO circuit diagram.

2. Make sure the 7495 is operating in Parallel mode by ensuring Pin 6

(Mode) is set to HIGH, and connect clock input to Clk 2(Pin 8).

3. Apply the first data at pin 5 (D) and apply one clock pulse. We

observe that this data appears at pin 10 (QD).

4. Now, apply the second data at D. Apply a clock pulse. We now

observe that the earlier data is shifted from QD to QC, and the new

data appears at QD.

5. Repeat the earlier step to enter data, until all bits are entered one by

one.

6. At the end of the 4th clock pulse, we notice that all 4 bits are

available at the parallel output pins QA (MSB), QB, QC, QD (LSB).

Truth Table: Circuit diagram:

CLK Serial I/P

QA QB QC QD

1 1 X X X 1

2 0 X X 1 0

3 1 X 1 0 1

4 1 1 0 1 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 35

4. PARALLEL INPUT PARALLEL OUTPUT (PIPO): Procedure:

1. Connections are made as shown in the PIPO mode circuit diagram.

2. Set Mode Control M to HIGH to enable Parallel transfer.

3. Apply the 4 data bits as input to pins A, B, C, D.

4. Apply one clock pulse at Clk 2 (Pin 8). 5. Note that the 4 bit data at parallel inputs A, B, C, D appears at the

parallel output pins QA, QB, QC, QD respectively.

Truth Table:

Parallel I/P Parallel O/P

CLK A B C D QA QB QC QD

1 1 0 1 1 1 0 1 1 Circuit diagram:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 36

5. PARALLEL INPUT SERIAL OUTPUT (PISO): Procedure: 1. Connections are made as shown in the PISO circuit diagram.

2. Now apply the 4-bit data at the parallel I/P pins A, B, C, D (pins 2

through 5).

3. Keeping the mode control M on HIGH, apply one clock pulse. The data

applied at the parallel input pins A, B, C, D will appear at the parallel

output pins QA, QB, QC, QD respectively.

4. Now set the Mode Control M to LOW, and apply clock pulses one by one.

Observe the data coming out in a serial mode at QD.

5. We observe now that the IC operates in PISO mode with parallel inputs

being transferred to the output side serially.

Truth Table:

Mode Clock Parallel I/P O/P

M CLK A B C D QA QB QC QD

1 1 1 0 1 1 1 0 1 1

0 2 X X X X X 1 0 1

0 3 X X X X X X 1 0

0 4 X X X X X X X 1 Circuit diagram:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 37

6. RING Counter: 7.JHONSON Counter:

Truth Table: Truth Table:

Circuit diagram: Circuit diagram:

M CLK QA QB QC QD

1 1 1 0 0 0

0 2 1 1 0 0

0 3 1 1 1 0

0 4 1 1 1 1

0 5 0 1 1 1

0 6 0 0 1 1

0 7 0 0 0 1

0 8 0 0 0 0

0 9 1 0 0 0

0 10 1 1 0 0

M CLK QA QB QC QD

1 1 1 0 0 0

0 2 0 1 0 0

0 3 0 0 1 0

0 4 0 0 0 1

0 5 1 0 0 0

0 6 0 1 0 0

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 38

Theory: A ring counter is a circular shift register which is initiated such that

only one of its flip-flops is the state one while others are in their zero states. A ring counter is a Shift Register with the output of the last one connected

to the input of the first, that is, in a ring. Typically, a pattern consisting of a

single bit is circulated so the state repeats every n clock cycles if n flip-flops

are used. It can be used as a cycle counter of n states.

A Johnson counter (or switch tail ring counter, twisted-ring counter,

walking-ring counter, or Moebius counter) is a modified ring counter, where

the output from the last stage is inverted and fed back as input to the first

stage. The register cycles through a sequence of bit-patterns, whose length

is equal to twice the length of the shift register, continuing indefinitely.

These counters find specialist applications, including those similar to the

decade counter, digital-to-analog conversion, etc. They can be implemented

easily using D- or JK-type flip-flops. Procedure: 1. Make the connections as shown in the respective circuit diagram.

2. Initial condition is set by setting up the circuit as shown in the figure.

3. There after all Pr and Clr pins of all F/Fs should be connected to VCC.

4. Apply clock and observe the output after each clock pulse, record the

observations and verify that they match the expected outputs from the

truth table.

5. Repeat the same procedure as above for the Johnson Counter circuit and

verify its operation

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 39

1. MOD 10 Asynchronous Counter: Truth Table: Circuit diagram:

CLK QD QC QB QA

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

Waveforms:

2. MOD 8 Asynchronous Counter:

Truth Table: Circuit diagram:

CLK QD QC QB QA

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 40

Experiment No: 9 Date:

REALIZE I) MOD N ASYNCHRONOUS COUNTER USING IC7490

II) MOD N SYNCHRONOUS COUNTER USING IC74192 Aim: To rig up Mod N asynchronous counter using IC 7490 and

synchronous counter using IC 74192.

Components required: IC7490, Patch cords, trainer kit, etc.

Procedure:

1. Check all the components for their working.

2. Make connections as shown in the circuit diagram.

3. Clock pulses are applied one by one at the clock input and output is

observed at QA,QB ,QC and QD 4. Verify the Truth Table and observe the outputs.

Note: Internal block diagram of IC 7490

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 41

Circuit diagram: Count up from 3 to 8

Truth table:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 42

Circuit diagram: Count down from 12 to 5

Truth table:

Note: IC 74192 is BCD Counter and IC 74193 is Binary Counter.

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 43

Truth Table:

Karnaugh Map: Circuit diagram:

D = QCQD + QCQD

QAQB

QCQD

00 01 11 10

00

01

1 1 1 1

11

10

1 1 1 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 44

Experiment No: 10 Date:

DESIGN PSEUDO RANDOM SEQUENCE GENERATOR USING

IC 7495 Aim: To design and study the operation of a pseudo random Sequence

generator using 7495.

Components required: IC 7495, IC 7486, Patch Cords & IC Trainer kit. Procedure: 1. Truth table is constructed for the given sequence, and Karnaugh maps

are drawn in order to obtain a simplified Boolean expression for the circuit. 2. Connections are made as shown in the circuit diagram.

3. Mode M is set to LOW (0), and clock pulses are fed through Clk 1 (pin 9).

4. Clock pulses are applied at CLK 1 and the output values are noted, and

checked against the expected values from the truth table.

5. The functioning of the circuit as a sequence generator is verified.

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 45

Simulation of Full Adder

Circuit diagram:

Truth Table:

A B Cin S C

0 0 0 0 0

0 0 1 1 0 S = A B Cin

0 1 0 1 0 C = A.B+ Cin (A B)

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 46

Experiment No: 11 Date:

FULL ADDER USING SIMULATION TOOL

Aim: To rig up a full adder circuit using basic gates

Procedure to enter schematic and to simulate:

1. Switch on the computer and open the simulation software.

2. Select new file to draw the circuit diagram

3. Select the required components to the circuits from the library and

place them on the window in required position

4. Wire the circuit according to the circuit diagram.

5. Connect the power supply and ground.

6. Save the circuit diagram with file name.

7. Click on simulation button and observe the led on and off condition

and compare with truth table.

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 47

Simulation of Synchronous Up/Down Counter using simulation tool

Circuit diagram:

Truth Table:

CLK UP COUNTER

DOWN COUNTER

QC QB QA QC QB QA

0 0 0 0 1 1 1

1 0 0 1 1 1 0

2 0 1 0 1 0 1

3 0 1 1 1 0 0

4 1 0 0 0 1 1

5 1 0 1 0 1 0

6 1 1 0 0 0 1

7 1 1 1 0 0 0

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 48

Experiment No: 12 Date:

MOD 8 SYNCHRONOUS UP/DOWN COUNTER

USING SIMULATION TOOL Aim: To rig up mod 8 synchronous up/down counter using simulation tool

Procedure to enter schematic and to simulate:

1. Switch on the computer and select Simulation and software.

2. Select new file to draw the circuit diagram

3. Select the required components to the circuits from the library and

place them on the window in required position

4. Wire the circuit according to the circuit diagram.

5. Connect the power supply, clock and ground.

6. Save the circuit diagram with file name.

7. Click on simulation button and observe the led on and off condition

and compare with truth table.

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 49

1. Binary to Gray Conversion:

Truth Table:

Binary inputs Gray outputs

B3 B2 B1 B0 G3 G2 G1 G0

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 0

0 1 0 0 0 1 1 0

0 1 0 1 0 1 1 1

0 1 1 0 0 1 0 1

0 1 1 1 0 1 0 0

1 0 0 0 1 1 0 0

1 0 0 1 1 1 0 1

1 0 1 0 1 1 1 1

1 0 1 1 1 1 1 0

1 1 0 0 1 0 1 0

1 1 0 1 1 0 1 1

1 1 1 0 1 0 0 1

1 1 1 1 1 0 0 0

Karaungh maps:

G3 = B3 G2 = B3 + B2

B1B0

B3B2

00 01 11 10

00

01

11

1 1 1 1

10 1 1 1 1

B1B0

B3B2

00 01 11 10

00

01

1 1 1 1

11

10

1 1 1 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 50

Experiment 1: BINARY TO GRAY CODE CONVERTER Aim: To realize:

i. Binary to Gray Converter using logic gates, NAND gates.

ii. Gray to Binary Converter using logic gates, NAND gates. Components Required: IC 7486, IC 7400 and IC 7408. Theory:

Binary to gray code conversion is a very simple process. There are

several steps to do this types of conversions. Steps given below elaborate on

the idea on this type of conversion. (1) The M.S.B. of the gray code will be exactly equal to the first bit of the

given binary number. (2) Now the second bit of the code will be exclusive-or of the first and second

bit of the given binary number, i.e if both the bits are same the result will be

0 and if they are different the result will be 1. (3)The third bit of gray code will be equal to the exclusive -or of the second

and third bit of the given binary number. Thus the Binary to gray code

conversion goes on. One example given below can make your idea clear on

this type of conversion.

Gray code to binary conversion is again very simple and easy

process. Following steps can make your idea clear on this type of conversions. (1) The M.S.B of the binary number will be equal to the M.S.B of the given

gray code. (2) Now if the second gray bit is 0 the second binary bit will be same as the

previous or the first bit. If the gray bit is 1 the second binary bit will alter. If

it was 1 it will be 0 and if it was 0 it will be 1. (3) This step is continued for all the bits to do Gray code to binary

conversion.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 51

G1 = B2 + B1 G0 = B1 + B0 (i)Realization using Basic Gates:

B1B0

B3B2

00 01 11 10

00

1

1

01

1 1

11 1 1

10

1 1

B1B0

B3B2

00 01 11 10

00

1

1

01 1 1

11 1 1

10 1 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 52

Procedure: 1. Verify that the gates are working.

2. Write the proper truth table for the given Binary to Gray /Gray to binary

Converter.

3. Draw Karnaugh maps for each bit of output. Simplify the Karnaugh

maps to get simplified Boolean Expressions. 4. Make connections on the trainer kit as shown in the circuit diagram for

the Binary to Gray /Gray to Binary converter. 5. Check the outputs for the corresponding inputs.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 53

2. Gray to Binary Conversion: Truth Table:

Gray Inputs Binary outputs

G3 G2 G1 G0 B3 B2 B1 B0

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 1 0 0 1 0

0 0 1 0 0 0 1 1

0 1 1 0 0 1 0 0

0 1 1 1 0 1 0 1

0 1 0 1 0 1 1 0

0 1 0 0 0 1 1 1

1 1 0 0 1 0 0 0

1 1 0 1 1 0 0 1

1 1 1 1 1 0 1 0

1 1 1 0 1 0 1 1

1 0 1 0 1 1 0 0

1 0 1 1 1 1 0 1

1 0 0 1 1 1 1 0

1 0 0 0 1 1 1 1

Karnaugh maps:

B3 = G3 B2 = G3 + G2

G1G0

G3G2

00 01 11 10

00

01

11

1 1 1 1

10 1 1 1 1

G1G0

G3G2

00 01 11 10

00

01

1 1 1 1

11

10

1 1 1 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 54

B1 = G3 + G2 + G1 B0 = G3 + G2 + G1 + G0 (i)Realization using Basic Gates: Result:

G1G0

G3G2

00 01 11 10

00

1

1

01

1

1

11

1

1

10

1

1

G1G0

G3G2

00 01 11 10

00 1 1

01 1 1

11 1 1

10 1 1

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 55

1. BCD to Excess-3-code: Truth Table:

BCD Input Excess 3 outputs

B3 B2 B1 B0 E3 E2 E1 E0

0 0 0 0 0 0 1 1

0 0 0 1 0 1 0 0

0 0 1 0 0 1 0 1

0 0 1 1 0 1 1 0

0 1 0 0 0 1 1 1

0 1 0 1 1 0 0 0

0 1 1 0 1 0 0 1

0 1 1 1 1 0 1 0

1 0 0 0 1 0 1 1

1 0 0 1 1 1 0 0 Circuit diagram:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 56

Experiment 2: BCD TO EXCESS- 3 CODE CONVERTERS. Aim: To design and realize the following using IC 7483.

(i) BCD to Excess- 3 Code

(ii) Excess-3 to BCD Code.

Components Required: IC 7483, IC 7486, Patch Cords & IC Trainer Kit.

Theory:

Code converter is a combinational circuit that translates the input

code word into a new corresponding word. The excess-3 code digit is

obtained by adding three to the corresponding BCD digit. To Construct a

BCD-to-excess-3-code converter with a 4-bit adder feed BCD code to the 4-

bit adder as the first operand and then feed constant 3 as the second

operand. The output is the corresponding excess-3 code. To make it work as a excess-3 to BCD converter, we feed excess-3 code as

the first operand and then feed 2's complement of 3 as the second operand.

The output is the BCD code.

Procedure: 1. Check all the components for their working. 2. Insert the appropriate IC into the IC base. 3. Make connections as shown in the circuit diagram. 4. Apply BCD code as first operand (A) and binary 3 as second operand (B)

and cin=0 for Realizing BCD-to-Excess-3-code.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 57

2. Excess-3-code to BCD: Truth Table:

Excess -3 Inputs BCD Outputs

E3 E2 E1 E0 B3 B2 B1 B0

0 0 1 1 0 0 0 0

0 1 0 0 0 0 0 1

0 1 0 1 0 0 1 0

0 1 1 0 0 0 1 1

0 1 1 1 0 1 0 0

1 0 0 0 0 1 0 1

1 0 0 1 0 1 1 0

1 0 1 0 0 1 1 1

1 0 1 1 1 0 0 0

1 1 0 0 1 0 0 1 Circuit diagram:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 58

Procedure: 1. Check all the components for their working.

2. Insert the appropriate IC into the IC base.

3. Make connections as shown in the circuit diagram.

4. Apply Excess-3-code code as first operand (A) and binary 3 as second

operand (B) and Cin=1 for realizing Excess-3-code to BCD.

Result:

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 63

VIVA QUESTIONS

1. What are Analog Systems? Give Examples.

2. What are Digital Systems? Give Examples.

3. Mention the disadvantages of Analog systems over Digital systems. 4. Explain Boolean algebra.

5. State Principle of Duality.

6. State De – Morgan’s Law.

7. Define Positive Logic and Negative Logic.

8. Define Literal. 9. Define MINTERM and MAX TERM.

10. Define a complementary function.

11. Explain Shannon’s reduction theorem.

12. Which are the basic gates and universal gates. 13. Define combinational network with example.

14. Define Sequential Network with example.

15. Define Double-Rail and Single -Rail logic.

16. When a Boolean Expression is called completely specified? 17. Explain the significance of a Don’t care function.

18. Explain the criteria of minimality.

19. Define implies, Subsumes, implicants.

20. What are Prime Implicants? 21. What is irredundant disjunctive normal formula?

22. What is an implicate?

23. What is a Map?

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 64

24. Explain the significance of Map.

25. What is a Minimal Sum and Minimal product?

26. Explain Quine - McClusky method. 27. Explain VEM method of reduction.

28. Explain Binary Adder and Subtractor.

29. Explain various scales of integration.

30. Define Carry Look Ahead Adder. 31. Define Comparator, Decoder and Encoder.

32. Give an example for Min-term generator.

33. Give an example for Max-term generator.

34. Define priority encoder. 35. Explain Multiplexing action.

36. Define PAL, PLA and PROM.

37. Differentiate between ROM and RAM.

38. What is a Memory? 39. What is internal state and secondary state?

40. Define Flip Flop and Latch.

41. Explain Basic Bi-stable element.

42. What is a metastable state?

43. Define setting and clearing in terms of flip-flop. 44. Explain SR Latch and Give an application.

45. Explain gated SR Latch and gated D Latch.

46. Explain Timing Diagram.

47. Explain Propagation Delay in gates. 48. Explain Set and Hold time in latches.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 65

49. Explain Master-Slave Flip-Flop.

50. Explain the significance of edge-triggering.

51. Explain Data Lock Out.

52. Give the characteristic equations of JK, D and T Flip Flops. 53. Define Registers with example.

54. Define Counters with example.

55. Explain ripple, asynchronous and synchronous counters.

56. Explain Race Around Condition.

57. List the basic logic series. 58. Explain Semiconductor diode behavior.

59. What is Saturating Logic?

60. Explain Fan-Out and Fan-in in gates.

61. Explain DTL and TTL. 62. What is wired logic?

63. What is Totem pole Output?

64. Explain Schottky TTL.

65. Explain Emitter-Coupled Logic. 66. Which is the fastest of all the logic families?

67. What is a MOSFET?

68. Explain Enhancement and Depletion Mode in MOSFET‟s.

69. Explain Threshold voltage. 70. Explain MOSFET as Resistor.

71. Clearly differentiate between PMOS and NMOS Logic.

72. Explain CMOS Logic.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 66

73. State Moore’s Law.

74. Differentiate between Moore and Mealy Law.

75. Define FPGA. 76. Define PLD.

77. Define CPLD.

78. Define Simulation.

79. State the application of Sequence Generator.

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 67

Question Bank

1. Simplify and realize Demorgan’s theorem for 2 variables.

2. Simplify and realize the given Boolean Expression using Universal Gates and verify the truth table. (Two expressions to be given).

3. Realize and verify the truth table of full adder basic gates only.

4. Realize and verify the truth table of a full Subtractor using basic gates only.

5. Realize and verify the truth table of full adder NAND gates only.

6. Realize and verify the truth table of a full Subtractor using NAND gates only.

7. Conduct a suitable experiment on 7483 IC to realize the following operation on the given 4 bit data addition and subtraction.

8. Realize and verify 5 bit magnitude comparator using IC 7485

9. Realize and verify the truth table of a half & full adder using IC 74153.

10. Realize and verify the truth table of a half & full subtractor using IC 74153.

11. Realize 3-Variable function using IC 74151(8:1 MUX)

12. Realize and verify a Boolean expression using IC 74139

13. Realize and verify the truth Table of Master Slave JK Flip Flop using NAND gates

14. Realize and verify the truth Table of Master Slave D Flip Flop using NAND gates

15. Realize and verify the truth Table of Master Slave T Flip Flop using NAND gates

16. Realize and verify Ring & Johnson counter using IC 7495

17. Use IC 7495 Shift registers to implement the following operations

a) SIPO b) PIPO

Digital Electronics Lab (17ECL38) 2018-19

Dept. of ECE, CIT, Gubbi Page 68

18. Use IC 7495 Shift registers to implement the following operations a) PISO b) SISO

19. Design and realize a Modulo N asynchronous counter using IC 7490.

20. Design and realize a Modulo N synchronous counter using IC 74192.

21. Design Pseudo Random Sequence generator using IC 7495. 22. Simulate full adder using simulation tool.

23. Simulate MOD 8 Synchronous up / down counter using simulation

tool.

----------------------------------*****------------------------------