Design Benchmarking to 7nm with FinFET Predictive...

Transcript of Design Benchmarking to 7nm with FinFET Predictive...

Design Benchmarking to 7nm with FinFET Predictive Technology Models

Saurabh Sinha, Brian Cline, Greg Yeric, Vikas Chandra, Yu Cao*

ARM Inc., *Arizona State University, Tempe, AZ [email protected]

ABSTRACT

The coming ten years promise great changes in silicon technology, with the end of planar bulk CMOS and the rise of interconnect parasitics to true significance. With such shifts in the underlying technology, the simple extrapolation of performance metrics may lead to pronounced prediction errors in design pathfinding. In this work, we utilize newly developed Predictive Technology Models for FinFETs aligned to the 2011 ITRS. Together with predictive interconnect models, we project performance and power landscape for the technology nodes from 20nm to 7nm. We present an overview of models, assess the advantage of FinFET over bulk CMOS devices, benchmark the scaling of critical design metrics, and illustrate major design barriers toward the 7nm node.

Categories and Subject Descriptors B.7.2 [Hardware]: Integrated Circuits – Design Aids, Simulation.

General Terms Performance, Design.

Keywords Predictive Technology Models, FinFET, power, performance, integrated circuits, scaling trends, BEOL.

1. INTRODUCTION Device-circuit technology forecasts such as [1] in 2009 provide valuable insight into design prediction and help guide design pathfinding. With similar intent, we update to follow the 2011 International Technology Roadmap for Semiconductors (ITRS) [2]. The time period examined, 2012-2020, encompasses the transition from planar bulk CMOS to silicon FinFET, so a key supporting initiative for this update has been the development of Predictive Technology Models for Multi-Gate transistors (PTM-MG). The details of these PTM-MG models are discussed in [3], and the models are available at the PTM website [4]. In this work we employ these models to assess possible scaling of circuit-based power and performance metrics. We overlay simulation results from 32nm and 22nm planar PTM models for continuity.

In spite of the performance gain by moving to a 3D multi-gate structure with FinFETs and continued dimension scaling, interconnect and FEOL (front end of line) RC are expected to

have an increasingly degrading impact on the power performance metrics of future circuits [5][6]. This work explores the potential of low power FinFETs by incorporating the effects of intra-cell and interconnect parasitic, allowing early-stage design-technology co-optimization (DTCO).

Section 2 discusses the PTM-MG model development and the methodology used to obtain FEOL and BEOL parameters. Linear scaling of interconnect resistance and capacitance according to the ITRS 2011 roadmap is used in conjunction with the predictive multi-gate models to quantify the behavior of representative design modules such as standard cells, ring oscillators, stacked devices and interconnect repeater design. We discuss the results of our simulation study in Section 3 where the advantages and limits of technology scaling are quantified providing us an insight into process and design choices.

2. PREDICTIVE TECHNOLOGY MODELING

2.1 PTM-MG Device Models The PTM-MG model parameters have been developed using the BSIM-MG model format [7] based on MOSFET scaling theory, the ITRS roadmap and early stage silicon data available from publications. Predictive models corresponding to the years 2012-2020 on the 2011 version ITRS roadmap have been developed. Details of the model development and verification with published data are presented in [3]. The BSIM-CMG model includes up-to-date FinFET modeling parameters, including the ability to perform geometry-based parasitic resistance and fringing capacitance calculation [7].

Figure 1 shows the trend of IDSAT vs. technology node for PTM-MG HP (high performance) and LSTP (low stand-by power)

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. ISLPED’12, July 30–August 1, 2012, Redondo Beach, California, USA. Copyright 2012 ACM 978-1-4503-1249-3/12/07...$10.00.

Figure 1. IDSAT vs. technology node/year for PTM-MG HP and LSTP devices. The IDSAT from the ITRS 2011 roadmap are plotted for comparison.

15

Figure 2. Schematic of sample inverter (1X strength) netlist with parameterized FEOL parasitics.

Table 1. Key Technology Parameters

Year 2012 2014 2016 2018 2020

Technology 20nm 16nm 14nm 10nm 7nm

VDD (V) 0.9 0.85 0.8 0.75 0.7

M1 Pitch (nm) 64 48 38 30 24

Fin Pitch (nm) 60 42 32 28 22

Effective Width (nm)

71 64 56 50 38.5

3D Factor 1.2 1.524 1.75 1.78 1.75

model versions. While the PTM predictions for HP transistors have been set to closely match the ITRS values, we have chosen to target an IOFF=0.1nA/um for PTM LSTP devices while ITRS LSPT targets IOFF=0.01nA/um. Any single device target will be inadequate to estimate SoC power/performance scaling due to increasing use of multiple VT options in design, but in our judgment the higher performance 0.1nA/um target is more useful. For these PTM models, we have tuned the leakage simply by adjusting the metal work function, and at [4] we document the work function adjustments that would more closely align to the ITRS LSPT targets. Note that the ITRS roadmap curves have three separate trend lines associated with planar transistors, FDSOI and FinFETs respectively, while all pathfinding simulations in this work use the LSTP transistor models.

2.2 FEOL / BEOL parameter assumptions The ITRS 2011 roadmap forms the primary basis for determining the technology node and BEOL parameters. Table 1 lists the important technology parameters such as M1 pitch and supply voltage. The ITRS does not provide guidance for Fin pitch or fin 3D-factor. The effective fin-width is calculated as 2*HFIN+TFIN where HFIN is fin-height and TFIN is fin-thickness. Our choices here have been guided by PTM-MG modeling insights [3] and trends from publications [8][9]. Achieving a fin-pitch smaller than the effective fin-width allows higher FinFET width than the corresponding planar area (3D

factor greater than one). Moving from a planar technology to 3D FinFETs impacts standard cell characterization, power and performance as will be seen in the subsequent sections.

In order to account for FEOL parasitics, a parameterized netlist incorporating the important coupling capacitances and contact resistances is used for simulation. Figure 2 shows a sample inverter schematic with the relevant parasitics. This inverter is referred to as “1X” because it contains one gate finger per device. A standard cell with twice the drive strength would contain 2 gate fingers per device and be referred to as “2X”, and the corresponding parameterized netlist would be expanded to reflect the increase in physical complexity. The coupling capacitances are layout dependent and values for the 20nm node are obtained from TCAD based experiments presented in [10] and listed in Table 2, which lists the key FEOL RC parameters as they scale through the ITRS nodes. Also missing from the ITRS is guidance regarding the contact resistance, so we have obtained values from [6], [11] for the 20nm node and have extended using simple extrapolation. Methods to reduce this resistance by replacing the tungsten via with copper, which offers lower resistivity, have been proposed [12], and are generally reflected in the relaxed scaling trend we have assumed for RS/D.

To scale the other parameters in Table 2 beyond the 20nm node, we scale the R and C values according to ITRS M1-pitch scaling trend of about 0.75 ~ 0.8 from 2012-2020.

3. RESULTS AND DISCUSSION

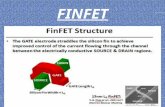

3.1 FinFET-based transistor scaling FinFETs will be the technology of choice for extending CMOS scaling beyond the 20nm node. Improved short channel control through a fully-depleted fin, reduced random dopant fluctuation, improved mobility and area efficiency are some of the primary advantages of FinFETs over planar transistors [13].

Figure 3 shows normalized delay vs. fan-out for Inverter, NAND2 (2-input) gate and NAND3 (3-input) gate comparing 22nm planar PTM and 20nm PTM-MG devices. All delay lines are annotated with their respective logical efforts. FinFET based NAND2 and NAND3 have lower logical effort, closer to their ideal values compared to their planar counterparts. The PTM planar device models have been tuned to have IOFF=0.1nA/um similar to the PTM-MG LSTP models for a fair comparison and both simulations were run with identical effective device width and FEOL parasitics.

Table 2. FEOL Parameters

Year 2012 2014 2016 2018 2020

Technology 20nm 16nm 14nm 10nm 7nm

RGCONT [12] 150 180 210 250 280

RWPT [2] 1.7 2.6 3.7 5.4 8.2

RSDCONT [6] 100 133 168 213 267

CIN-OUT (aF) [11] 37.5 28.1 22.3 17.6 14.1

CIN-RAILS(aF) [11] 29.5 22.1 17.5 13.8 11.1

COUT-RAILS (aF) [11] 38 28.5 22.6 17.8 14.3

16

Near ideal sub-threshold characteristics allowing lower VT and better gate overdrive, significantly lower DIBL in FinFETs compared to planar transistors, and negligible body effect are the main effects resulting in excellent stacked device performance [14][15]. Comparing FinFET 20nm NAND3 to planar 22nm NAND2, we see that using higher fan-in circuits with FinFETs can be considered, giving area savings with minimal delay penalty.

To understand the impact of fin 3D factor, Figure 4 shows a plot of the planar transistor width (PFET and NFET) for a 9-track standard cell library, where “9-track” refers to the space occupied by 9 M1 pitches. A 75% fill ratio has been assumed, meaning that 75% of the standard cell height is occupied by active transistors and the remaining 25% is isolation between transistors. For reference, we extend the planar trend according to M1 pitch scaling. The effective FinFET width for a 9-track

cell is also plotted in Figure 4. Based on the effective fin width and fin-pitch assumptions in Table 1, we find that a 9-track inverter can accommodate about 8 active device fins (4 fins per NFET/PFET). Transitioning from planar technology to FinFETs, the total transistor width in a 9-track cell can be much higher owing to the 3D structure of the transistors, e.g., the 16nm node standard cell FinFET transistor width could be equal to or greater than the 20nm node standard cell planar width. This translates to standard cells with significantly higher drive strength as compared to standard process scaling assumptions, although practical issues associated with sub-20nm lithography will also be important. This has implications to the end SoC power. Smaller size standard cells could potentially be deployed to reduce power but yet maintain performance, and the need for larger drive strength cells in loaded critical paths can be reduced. These SoC-level implementation aspects are examples of technology pathfinding which can be considered in future studies, as enabled by these new PTM-MG models.

3.2 Pathfinding Design Analysis Using PTM-MG model files for FinFET transistors and the FEOL and BEOL assumptions described in Section 2.2, we conducted SPICE simulations of inverter ring oscillators (RO) with different wire-loading to understand the active device and interconnect scaling trends.

Figure 5 shows delay vs.VDD across 10-stages of an inverter based ring oscillator with a light 10-track wire loading for different technology nodes using our BSIM-MG models. For comparison, delay trends with supply voltage scaling using 32nm and 22nm PTM planar models were simulated as well. We have tuned the device planar model parameters for IOFF=0.1nA/um, similar to the PTM-MG models. As demonstrated in previous work [13][14], FinFETs show excellent delay vs. VDD scaling owing to superior electrostatics. Scaling VDD from 1V to 0.6V, FinFET delay degrades by about 3X, while 32nm/22nm planar technologies suffer a corresponding degradation of up to 7X.

In Figure 5 we observe delay down to 0.45V and we find that FinFET delay at 0.45V is similar to that of a 0.6V planar device, demonstrating its potential for very low power near-threshold

Figure 5. Device Delay trends of RO for 20nm to 7nm nodes with 10 track wire loading between stages. 32nm and 22nm planar devices show inferior performance with VDD scaling.

Figure 4. Total Transistor Width (NFET+PFET) for a 9-track standard cell assuming 75% fill-ratio. Owing to FinFET 3-D factor and fin-pitch scaling, the effective transistor width in a 10-track standard cell will be higher than planar scaling assumptions.

Figure 3. Normalized delay of Inverter, 2-input NAND and 3-input NAND for 22nm planar and 20nm FinFET technologies. FinFET stacked devices are inherently better gates with lower logical effort.

17

Figure 7. INV RO delay across 10-stages with intrinsic, no-wire load, with 10, 100 and 500 track wire load between stages. 32nm and 22nm planar RO delay with 10 track wire load is plotted for

Figure 8. Energy vs. delay trends for RO with VDD scaling. VDD points are the same as in Figure 5, with 1.0V VDD corresponding to the right-most data points.

Figure 6. Decomposition of RO Delay as a percentage of the total delay consisting of active devices, FEOL RC and 10-track wire RC.

operation. However, practical VDD scaling studies would require quantification of manufactured device variance, which is an example of potential future work.

Figure 8 shows the energy vs. delay across 10-stages of the inverter based ring-oscillator. In spite of improved delay vs. supply voltage scaling trend, switching energy of 22nm planar circuit is lower compared to 20nm FinFET for the same VDD. This is due to the higher effective transistor width within a standard cell, and a slight increase in parasitic capacitance associated with the FinFET structure. Figure 8 then underscores the requirement that sub-20nm FinFETs need utilize their natural ability to operate at reduced VDD in order to realize an energy savings. Alternatively, smaller cells with reduced fin count can be considered, as could device re-targeting to lower leakage set points to below comparable planar device leakage.

In Figure 7 we take the delay information from Figure 5 for the specific VDD values across technology nodes as listed in Table 1. To understand the impact on delay scaling due to interconnect parasitics, we have investigated different transistor loading

scenarios. Intrinsic gate delay means we have removed all of the R and C values associated with the parameterized netlist of Figure 2. We then add only the R values, then also the C values to get the “RC” curves, and then we also add wire loads between stages of 10-, 100-, and 500- tracks (M1 pitches). Given that standard cells are typically 7-12 metal tracks in dimension, these wire lengths are representative of the range of “local” wire lengths that would be seen in a logic block. The ITRS CV/I delay trend normalized to 20nm FinFET intrinsic delay is plotted for reference. It is evident from the deviation between the ITRS CV/I trend and the intrinsic RO delay trend that first order CV/I metric does not adequately capture transient device behavior. Changing CV/I from IDSAT to IEFF would not materially change the divergence between static I metric and AC device simulation [17].

Additionally, the ITRS roadmap does not take into account practical circuit FEOL and BEOL parasitics. Adding contact resistance to the intrinsic devices as shown by the red curve in Figure 7 actually reverses the delay scaling trend beyond the 2016 node. With FEOL RC and 10-track wire-load, the delay penalty increases from 33% to 76% from the 20nm to 7nm node, as compared to intrinsic delay. Additionally, a 10-track wire load adds about 15% delay penalty at the 7nm node.

Figure 6 shows the decomposition of the components from Figure 7 as a percentage of total delay of the ring-oscillator for the case of 10-track wire load between stages. The plot highlights the effect of contact resistance on delay scaling and the importance of continued reduction of contact resistance. Potential improvements include full copper contacts, self-aligned contacts [11], and aggressive contact aspect ratio scaling, with the latter two options representing a trade-off in contact R vs. C scaling.

Figure 11 shows the power-performance trends for the ring-oscillator with 10-track load across technology nodes corresponding to the years 2012-2020. The nominal VDD trajectory shown by the dashed line reiterates the Figure 8 conclusion that scaling reverses beyond 14nm at 2016 due to limits from interconnect and FEOL RC while alternate trajectories with higher VDD would lead to improved performance at the cost of reduced power scaling.

18

Figure 10. Energy per switch per unit wire length for buffers (left axis) and target frequency (right axis) vs. technology node.

Figure 12. Power density vs. technology node comparing PTM-MG INV RO with 10-track wire load, ITRS system driver projections and ITRS PIDS projections.

Figure 9. Maximum wire length that can be driven using buffers (left axis) and the number of buffer stages (right axis) at a target frequency vs. technology node. The buffer stages consist of INV (4X minimum strength) cells driving global wires.

Figure 11. Power vs. Performance of INV RO with 10-track wire load from 2012-2020. The dash-line shows the power performance trajectory with the nominal VDD at that technology node.

When considering conclusions such as in Figure 9, it should be emphasized that this present work considers only silicon-based FinFETs through the 7nm node. Device scaling options such as high mobility channels [16] and/or gate-all-around (GAA) nanowires [18] hold the potential to improve device scaling in this time frame, and are obvious areas for future work as research clarifies these potential device paths.

Several studies have predicted that power scaling will continue to lag area scaling, resulting in increased power density. In many designs, power is already at critical levels, so an increase in power density can only be met by powering down increasing portions of the chip, a trend referred to as “dark silicon” [19]. Figure 12 compares normalized power density scaling to two power density factors derived from the 2011 ITRS. The first ITRS power density factor takes the SoC-level power for Consumer Portable SoC from Figure SYSD6 and assumes a constant die size for the SoC area scaling. The second ITRS power density factor multiplies the PIDS LSPT CV2 values by a normalized clock frequency that is increasing at 4% CAGR as

per the 2011 ORTC chapter to derive power, and then calculates power density by dividing this power number by the logic gate area w/overhead listed in ORTC table 3-C.

Another important design characteristic is the maximum wire length, which is the longest wire that a set of buffers can drive in a given clock period. This metric is important to clock network design and other long distance communications (e.g., core-to-core IO, core-to-cache IO, etc.). Any wire lengths that exceed the maximum value incur additional power overhead, since flip flops have to be introduced to essentially “pipeline” the path. In order to benchmark the scaling of maximum wire length, we again use the 4% CAGR for clock frequency and simulate a number of INV strengths. We found that the rising interconnect parasitics (wire resistance and capacitance) combined with the increased intra-cell parasitics cause the maximum wire length to decrease by ~4.2X on average, whereas the clock frequency only increases by ~1.4X from 2012 to 2020. An example of this trend is shown in Figure 9 for a 4X-minimum-strength INV cell. Normalized to Metal1 track length, the maximum wire length translates to about 21,500 tracks in 2012 down to 15,000 tracks in 2020. The decreased

19

performance scaling seen after the 2016 technology node is also reflected in Figure 9. The ideal number of buffer stages needed to obtain the maximum wire length is shown on the right-hand Y-axis of Figure 9. From 2012 to 2016, it is beneficial to spread the wire resistance and capacitance between a larger number of buffer stages. However, after 2016, inserting more repeaters actually degrades performance because of the increased intrinsic delay of the gates, themselves. In reality, we would optimize buffer strength for each technology node, but in order to do so would require accurate layout parasitic extraction, including stress effects, which is outside the scope of this work.

In the same set of “maximum wire length” experiments, we did observe a ~1.7X average decrease in “Energy-per-wire-length,” as shown in Figure 10. Despite the increasing clock frequency, the repeater experiments showed a ~7% year-on-year scaling in energy/m. This decrease can be attributed to decreasing supply voltage and the ~4.2X total decrease in maximum wire length.

4. CONCLUSIONS

Using new PTM-MG FinFET device models and incorporating the effect of both FEOL parasitic within standard cells and interconnect wire scaling trends from ITRS 2011 roadmap, we have evaluated key performance metrics for scaled CMOS technologies in the 2012-2020 time period. We highlight the difference between ITRS CV/I metric and actual ring oscillator simulations, which include FET geometry-based parasitics. We show the increasing penalty from the contact resistance, ultimately leading an anticipated decrease in local circuit speed after 2016 without further process improvements. Potential FET improvements in beyond 2016 include high mobility channel materials and/or silicon nanowires. Commensurately, contact resistance should be aggressively pursued with R/C tradeoffs from contact aspect ratio. We confirm a trend in power density scaling that highlights increasing dark silicon in future technology nodes, unless (for instance) VDD can be scaled more aggressively than the ITRS roadmap. Investigating the interconnect, we show that the maximum distance serviceable by wire + repeater decreases, even on a per-track basis, although a general trend of reducing energy per switch and increasing clock frequency can be supported through 2020. We have highlighted areas for future work, and look forward to use of these new models by the technology community.

5. REFERENCES [1] X. Li, Y. Cao, Z. Zhu, J. Song, et al. “Pathfinding for 22nm

CMOS Designs using Predictive Technology Models”, IEEE Custom Integrated Circuits Conf. (CICC), 2009, pp, 227-230.

[2] International Technology Roadmap for Semiconductors (ITRS), 2011 Edition, www.itrs.net.

[3] S. Sinha, G. Yeric, V. Chandra, B. Cline, Y. Cao; “Exploring Sub-20nm FinFET design with Predictive Technology Models,” in Design Automation Conference (DAC), 2012 49th ACM/EDA/IEEE, June 2012.

[4] Predictive Technology Models, Arizona State University, Nanoscale Integration and Modeling Group. http://ptm.asu.edu/latest.html.

[5] Lan Wei; Jie Deng; Li-Wen Chang; Keunwoo Kim; Ching-Te Chuang; Wong, H.-S.P.; , "Selective Device Structure

Scaling and Parasitics Engineering: A Way to Extend the Technology Roadmap," Electron Devices, IEEE Transactions on , vol.56, no.2, pp.312-320, Feb. 2009

[6] Tada, M.; Inoue, N.; Hayashi, Y.; , "Performance Modeling of Low- k /Cu Interconnects for 32-nm-Node and Beyond," Electron Devices, IEEE Transactions on , vol.56, no.9, pp.1852-1861, Sept. 2009

[7] M. V. Dunga, C.-H. Lin, D. D. Lu, W. Xiong, C. R. Cleavelin, P. Patruno, J.-R. Hwang, F.-L. Yang, A. M. Niknejad, and C. Hu, “BSIM-MG: A Versatile Multi-Gate FET Model for Mixed-Signal Design,” in 2007 Symposium on VLSI Technology Digest of Technical Papers, 2007, pp. 60–61.

[8] C.-C. Yeh et al., “A low operating power finfet transistor module featuring scaled gate stack and strain engineering for 32/28nm soc technology,” in IEDM, dec. 2010, pp. 34.1.1 –34.1.4.

[9] C.-Y. Chang et al., “A 25-nm gate-length finfet transistor module for 32nm node,” in IEDM, dec. 2009, pp. 1 –4.

[10] Scholze, A.; Furkay, S.; Seong-Dong Kim; Jain, S.; , "Exploring MOL design options for a 20nm CMOS technology using TCAD," Simulation of Semiconductor Processes and Devices (SISPAD), 2011 International Conference on , vol., no., pp.99-102, 8-10 Sept. 2011

[11] S.-C. Seo, L.F. Edge, S. Kanakasabapathy, M. Frank, et al., “Full Metal Gate with Borderless Contact for 14 nm and Beyond”, IEEE Symp. VLSI Technology (VLSIT), 2011, pp. 36-37.

[12] Topol, A., et.al, "Lower Resistance Scaled Metal Contacts to Silicide for Advanced CMOS," VLSI Technology, 2006. Digest of Technical Papers. 2006 Symposium on

[13] M. Jurczak et al., “Review of finfet technology,” in SOI Conference, oct. 2009, pp. 1 –4.

[14] von Arnim, K., et al., "A Low-Power Multi-Gate FET CMOS Technology with 13.9ps Inverter Delay, Large-Scale Integrated High Performance Digital Circuits and SRAM," VLSI Technology, 2007 IEEE Symposium on, vol., no., pp.106-107, 12-14 June 2007.

[15] Venugopal, R.; et. al.; , "Design of CMOS Transistors to Maximize Circuit FOM Using a Coupled Process and Mixed-Mode Simulation Methodology," Electron Device Letters, IEEE , vol.27, no.10, pp.863-865, Oct. 2006.

[16] K. C. Saraswat, C. O. Chui, D. Kim, T. Krishnamohan and A. Pethe, “High Mobility Materials and Novel Device Structures for High Performance Nanoscale MOSFETs”, IEEE Intl. Devices Meeting (IEDM), 2006, pp. 1-4.

[17] G. Yeric, “Technology Roadmaps and Low Power SoC Design”, IEEE Intl. Electron Devices Meeting (IEDM), 2011, pp. 15.4.1- 15.4.4.

[18] C.-H. Park, S.-H. Lee, Y.-R. Kim, C.-K. Baek and Y.-H. Jeong, “Gate-All-Around Silicon Nanowire Field Effect Transistors”, IEEE Intl. Conf. Nanotechnology, 2011, pp. 255-259.

[19] H. Esmaeilzadeh, E. Blem, R. St. Amant, K. Sankaralingam, and D. Burger, “Dark Silicon and the End of Multicore Scaling”, IEEE Intl. Symp. Computer Architecture (ISCA), 2011, pp.365-376.

20