Design and Analysis of a Multidimensional Trellis Coded...

Transcript of Design and Analysis of a Multidimensional Trellis Coded...

Design and Analysis of a Multidimensional Trellis

Coded Demodulator

DAMIEN SERVANT

Master’s Degree ProjectStockholm, Sweden 2004-06-16

IR-SB-EX-0424

Department of Signals, Sensors, Systems

Thesis M.Sc. in Signal Processing

Design and Analysis of a Multidimensional Trellis Coded Demodulator

Damien Servant

Abstract Satellite transmissions of telecom or “remote sensing” data require high bit rates without enlargement of the frequency bandwidth. These transmissions are confronted with a low signal-to-noise ratio channel. To find a suitable solution to this technical problem, new recommendations of the international “Consultative Committee for Space data Systems” (CCSDS) suggest a multidimensional trellis based modulation/demodulation.

This master thesis project will design and analyze a demodulator equipment targeting a

VHDL/FPGA implementation. Algorithms have been first implemented in C++ to analyze the theoretical behavior of the receiver. Then, using this simulation, parameters will be chosen for the best trade-off between performance and complexity. Finally, the receiver has been realized in VHDL for a FPGA logic chip, keeping in mind the speed and size optimizations of the implementation.

The final operational tests demonstrate the efficiency of the multidimensional trellis

based modulation, even if this efficiency requires a much more complex decoding chain.

Acknowledgements This master thesis project has been carried out from January 2004 to June 2004 at the Station department of the French company, IN-SNEC, in Paris.

I would like to thank my supervisor Nicolas Pasternak at IN-SNEC for being supportive and motivating during my thesis project.

I would also like to thank all members of the Station department of IN-SNEC who helped me during my thesis, taking time to answer to all my questions, from stupid ones to more tricky questions. Working with them was really nice.

I also want to express my gratitude to my Swedish advisor at KTH, Patrick Svedman. His support and his feedback have been much appreciated.

Table of Contents

1 INTRODUCTION........................................................................................ 5 1.1 BACKGROUND .............................................................................................................5 1.2 PURPOSE OF THE PROJECT............................................................................................6 1.3 OUTLINE......................................................................................................................6

2 THEORY OF TRELLIS CODED MODULATION................................. 7 2.1 CLASSICAL ERROR CORRECTING CODING SYSTEMS AND MODULATIONS ......................7

2.1.1 Classical modulation and demodulation systems ...............................................7 2.1.2 Traditional error correcting coding and decoding ..............................................7

2.2 TRELLIS CODED MODULATION....................................................................................8 2.2.1 Capacity of multilevel phase modulation channels ............................................8 2.2.2 Simple Trellis Codes ..........................................................................................9 2.2.3 Codes obtained by Ungerboeck........................................................................12

2.3 TRELLIS CODED MULTIDIMENSIONAL PHASE MODULATION.....................................14 2.3.1 Multi-D Signal Set Partitioning........................................................................14 2.3.2 Construction of mapping equations..................................................................15 2.3.3 Effect of a 360°/M phase rotation on a multi-D MPSK signal set ...................16 2.3.4 The general encoder system .............................................................................18

2.4 DECODING ALGORITHM .............................................................................................21 2.4.1 Brute-force approach ........................................................................................21 2.4.2 Simpler approach..............................................................................................22

3 CCSDS NORM: 4-D 8-PSK TRELLIS CODED MODULATION....... 24 3.1 GENERAL PRINCIPLE OF THE 4-D 8-PSK TCM ENCODER ..........................................24 3.2 TRELLIS ENCODER STRUCTURE ..................................................................................25 3.3 CONSTELLATION MAPPERS FOR 4-D 8-PSK TCM.....................................................25 3.4 DIFFERENTIAL ENCODER ...........................................................................................26 3.5 APPLICATION OF THE DECODING ALGORITHM TO THE CCSDS NORM ........................27

4 SIMULATION RESULTS ........................................................................ 30 4.1 SIMULATION RESULTS FOR QPSK AND 8-PSK ..........................................................31 4.2 SIMULATION RESULTS FOR A 4 DIMENSIONAL 8-PSK TCM.......................................32

4.2.1 Comparisons between 4D 8-PSK TCM and QPSK modulations.....................32 4.2.2 Comparisons between hard and soft decisions in decoding .............................33 4.2.3 Influence of quantization parameters on performances....................................35

5 VHDL IMPLEMENTATION OF THE TRANSMISSION CHAIN..... 40 5.1 IMPLEMENTATION OF THE TCM ENCODER.................................................................40

5.1.1 Global architecture ...........................................................................................40 5.1.2 Components of the coding system....................................................................42

5.2 IMPLEMENTATION OF THE TCM DECODER.................................................................44 5.2.1 Transition Metric Calculator: the parallel architecture.....................................45

5.2.2 The Viterbi decoder ..........................................................................................49 5.2.3 Demapper .........................................................................................................54 5.2.4 Differential decoder..........................................................................................55

5.3 CHANNEL SIMULATOR...............................................................................................55 5.4 GLOBAL SIMULATION CHAIN .....................................................................................56

6 OPERATIONAL TESTS..................................................... 57 6.1 DESCRIPTION OF THE TEST BENCH .............................................................................57 6.2 8-PSK DEMODULATOR TESTS ...................................................................................57 6.3 4D 8-PSK TCM DECODER TESTS..............................................................................59 6.4 4D 8-PSK TCM RECEIVER TESTS .............................................................................60

CONCLUSIONS................................................................................................ 62 BIBLIOGRAPHY ............................................................................................. 63 TABLE OF ILLUSTRATIONS....................................................................... 64 APPENDIX A .................................................................................................... 66 APPENDIX B..................................................................................................... 70 APPENDIX C .................................................................................................... 71

1 Introduction 5

1 Introduction 1.1 Background In the early 80s, G. Ungerboeck [1] - [3] introduced the first Trellis Coded Modulation (TCM). He proved that this modulation could achieve good performances and improve the gain over uncoded modulations. By associating a convolutional encoder, a mapper and a modulator, this modulation combines coding and modulation techniques for digital transmission over band-limited channels and allows the achievement of significant coding gains. Moreover this modulation improves the power efficiency of the transmission without compromising the bandwidth efficiency.

This is the idea behind trellis coding. In conventional coding, the coding is separate from modulation. Coding occurs at the digital level, before modulation and generally involves adding bits to the input sequence. The resultant redundancy requires added bandwidth. TCM schemes employ redundant non-binary modulation in combination with a finite-state encoder which governs the selection of modulation signals to generate coded signal sequences. The power gains are obtained without bandwidth expansion or reduction of the effective information rate as required by traditional error-correction schemes. Nowadays, trellis coded modulations are used in several telecommunication systems like in modems or satellite transmissions.

Few years after, G.D. Forney [4] introduced the first theory on multidimensional

constellations. Then this theory had been developed by S.Pietrobon [5] who improved the modulation with the introduction of the multidimensional coding techniques. The trellis code is applied to several parallel constellations of the same size. Signals from a 2-L dimensional signal set space are transmitted over a two-dimensional modulation channel (as M-PSK) by sending L consecutive symbols. This multidimensional modulation provides a number of advantages that usually cannot be found with standard TCM: flexibility in achieving a variety of fractional information rates, codes which are transparent to discrete phase rotations of the signal set and higher decoder speeds resulting from the high rate codes used. The disadvantage is in the increased computational complexity for the encoding and decoding process. The combination of convolutional coding, multiphase modulation and multidimensional techniques offers a substantial power gain together with bandwidth conservation or reduction, in comparison to their classical separate use as it is done frequently with binary or quaternary modulations.

This multidimensional trellis coded modulation is mainly used in bandwidth-constrained communications as for transmission between remote satellites and Earth stations. In this context, it is efficient both in power efficiency and bandwidth efficiency for a given information quantity.

1 Introduction 6

1.2 Purpose of the project The CCSDS (Consultative Committee for Space Data Systems) is an international organization which sets the standards for the space data transmissions. One of their recommendations [6] describes a multidimensional trellis based modulation, 4D 8PSK TCM. It sets all the parameters of the system: rate of transmission, mapping, description of convolutional encoder and differential encoder.

The CCSDS sets the encoder and all parameters of the emitted symbols to

standardize space transmissions. The manufacturer of the receiver can then design its own decoder structure. The objective of this thesis is to design a version of this receiver and implement it on an FPGA.

As this system is used for high data rate transmission, the decoder must work with

a high clock-frequency. It should be able to achieve peak data rates of 460 Mbits/s. Moreover, this decoder has to be the simplest as possible since it will be integrated in a FPGA, which has limited resources. These two constraints are the main points of this project. They will require making many important trade-offs between efficiency and resources at different levels of the receiver. In this aim, the choice of quantization parameters will have to be deeply discussed.

The theoretical structure of the decoder is not particularly complex: a Viterbi

decoder, a demapper and a differential decoder. But the high speed constraint (at least 320 Mbits/s) and the large parameters set by the CCSDS (4 8-PSK symbols transmitted, 64 states of the trellis, differential encoder of constraint length 7) will seriously increase the difficulty of the design. That will require an algorithm structure totally different from a classical C implementation. Moreover this decoder should also be able to decode 4 different modulation rates: 2 bits/symbol, 2.25 bits/symbol, 2.5 bits/symbol and 2.75 bits/symbol which are all defined by the CCSDS. 1.3 Outline This thesis is organized as follows. In chapter 2, the theory of Trellis Coded Modulation is reviewed. Multidimensional techniques are introduced and compared to the standard modulation.

Then chapter 3 presents details of the CCSDS recommendations about 4-D 8-PSK TCM. This description only concerns the encoder part of the transmission chain.

Chapter 4 gives the results of a simulation chain implemented in C++. First, 8 PSK and QPSK are simulated. Then, different quantization configurations are simulated to make the best trade-offs for the receiver.

In chapter 5, the VHDL implementation of the transmission chain is described. It contains encoder and decoder blocks.

Then chapter 6 gives the results of the operational tests realized on a platform. Finally, chapter 7 contains conclusions and some suggestions of possible

improvements to the implementation.

2 Theory of trellis coded modulation 7

2 Theory of trellis coded modulation 2.1 Classical error correcting coding systems and modulations In classical digital communication systems, modulation and error-correcting coding systems are separated. Modulator (and demodulator) converts an analog channel into a discrete channel (and conversely) whereas encoder and decoder can correct errors on a discrete channel. 2.1.1 Classical modulation and demodulation systems Conventional multi-level modulation system (amplitude or phase modulation) maps m bits into one of M m= 2 possible signals, as shown on Figure 2.1. In the receptor, the demodulator makes the inverse operation by making a nearest-neighbor decision.

Figure

2.1.2 Traditional er Information theory suggeshould be designed and thsignals rather than indivconventional coding, thelevel, before modulationresultant redundancy retransmission rate.

If low signal-to-noiperformance of the moduloss caused by sending reby increasing the modulinformation rate from compensation is often no

M 8-PSK

4-A

2.1: Signal sets for phase and amplitude modulations

ror correcting coding and decoding

sts that for optimal communications long sequences of signals at the receiver should perform decision making over such long

idual bits or symbols. This is the main idea behind coding. In coding is separate from modulation. It occurs at the binary and generally involves adding bits to the input sequence. The quires added bandwidth or a decrease of the information

se ratios (SNR) or non-stationary signal disturbance limits the lation system, the ability to correct errors can justify the rate dundant check bits. Besides this rate loss can be compensated

ation level of the coded system or by increasing the effective the source output of the coded system. But this required t possible.

2 Theory of trellis coded modulation 8

A new idea was then introduced: modulation and error correcting coding should occur together and not in an independent manner. This is the principle of the Trellis Coded Modulation (TCM).

2.2 Trellis Coded Modulation

TCM came first from a work on multilevel systems [1], employing the Viterbi algorithm to improve signal detection in the presence of inter-symbol interference. This work revealed the importance of the Euclidean distance between signal sequences. As the first results did not show a large improvement, error correcting coding methods had to be combined. Over the fact that Euclidean distance instead of the Hamming distance should be optimized to find efficient codes, it has also been shown that the necessary coding redundancy would have to come from a signal-set expansion to avoid bandwidth expansion.

To describe the principle of the trellis-coded modulation, we will first study the potential gains obtained by introducing more signal levels or phases in the modulation. Secondly, we will see how to construct, in a heuristic manner, efficient and simple trellis codes for an 8-PSK modulation.

2.2.1 Capacity of multilevel phase modulation channels

Before addressing the code-design problem with expanded channel-signal sets, it is appropriate to examine in terms of channel capacity the limits of performance, which may thereby be achieved.

The output of an AWGN channel can be written r a wn n n= + where an denotes a real- or complex-valued discrete signal transmitted at modulation time nT, and wn is an independent normally distributed noise (AWGN) sample with zero mean and variance σ² per dimension. The average SNR for a two-dimensional modulation is defined by:

SNR

E a

E w

E an

n

n= =

2

2

2

22σ ( 2.1 )

In [3], the channel capacity C* has been evaluated by a Monte Carlo method and

the results are shown in Figure 2.2. In this figure, C* is plotted as a function of SNR. The value of SNR at which in uncoded transmission symbol-error probability P er ( ) = −10 5 is achieved is also indicated. The Shannon’s Theory defines the channel capacity which is the upper bound of the curves.

2 Theory of trellis coded modulation 9

Figure 2.2: Channel capacity C* of band limited AWGN channel.

This figure will be interpreted with the example of a 2 bits/T transmission of an

uncoded 4-PSK modulation where P er ( ) = −10 5 occurs at SNR = 12.9 dB. If the number of channel signals is doubled, e.g. by choosing 8-PSK modulation, error free transmission of 2 bits/T is theoretically possible already at SNR = 5.9 dB (assuming unlimited coding and decoding effort). If the number of signal levels/phases is still increased, transmission can gain only 1.2 dB further. Therefore, the capacity of the channel and the limit of an uncoded modulation are almost reached with an 8 PSK. 2.2.2 Simple Trellis Codes Following the arguments of the previous paragraph, in order to improve error performance, m bits have to be transmitted in redundantly coded form by a set of 2 1m+ channel signals (doubling the number of channel signals). This can be accomplished by a convolutional encoding followed by a mapping of groups of m+1 bits. The general structure of the encoder is shown in Figure 2.3.

Figure 2.3: General Encoder Structure

2 Theory of trellis coded modulation 10

This encoder should be designed in order to maximize the free Euclidean distance between two codewords, which determines the performance of the coding. Thus, if a an nand ' are two codewords, the encoder maximizes the free distance:

( )d Min d a afree

a an n

nn n

=⎡

⎣⎢

⎤

⎦⎥

≠∑'

, '/

21 2

( 2.2 )

In order to maximize this free distance, a method called “mapping by set

partitioning” is developed in [2] and [3] by Ungerboeck. As shown on Figure 2.4, the mapping follows from successive partitioning of a channel signal set into subsets while it increases the minimum squared Euclidean distance.

Figure 2.4: Partitioning of 8-PSK channel signals into subsets.

The encoder is considered as a finite state machine with a given number of states

and specified state transitions. If m bits are to be encoded per modulation interval T there must be 2m possible transitions from each state to a successor state. More than one transition may occur between pairs of states. After selecting a suitable trellis state-transition diagram, the remaining task consists of assigning channel signals from an extended set of 2 1m+ signals to the transitions such as to achieve maximum free Euclidian distance.

To illustrate this method, the heuristic design of 8-PSK codes will be discussed in

more detail for a coded transmission of 2 bits/T. As a reference, uncoded 4-PSK modulation is used. Figure 2.5 shows a one state-trellis with four “parallel” transitions for an uncoded 4-PSK modulation regarded as a coded modulation. Figure 2.6 shows the trellises with 2, 4, 8 and 16 states for a coded 8-PSK modulation.

2 Theory of trellis coded modulation 11

Figure 2.5: Coded 8-PSK modulation, 2 bits/T

Figure 2.6: Coded 8-PSK modulation, 2 bits/T

The construction of the different trellises for coded 8-PSK modulation follows several rules:

1. All 8-PSK signals should occur with equal frequency and with a fair amount of regularity and symmetry,

2. Transitions originating from the same state receive signals either from subset B0 or B1,

3. Transitions joining into the same state receive signals either from subset B0 or B1, 4. Parallel transitions receive signals either from subset C0, C1, C2 or C3.

2 Theory of trellis coded modulation 12

Rule 1 reflects the intuition that good codes should exhibit regular structures, and rules 2, 3 and 4 guarantee that the Euclidian distance associated with all single and multiple signal error-events exceeds the free Euclidian distance of uncoded 4-PSK modulation by at least 3 dB.

For each trellis, two paths are represented: they both originate from the same initial state and merge into the same final state in fewer steps as possible. As an example, the eight-state trellis of the 8-PSK coded modulation, depicted in Figure 2.6, has two paths starting from the same state. These two paths cannot join a similar state in less than 3 steps. Thus, we can calculate the free distance of each trellis and deduce the coding gains over the reference modulation: uncoded 4-PSK modulation. These gains are computed with the following formula:

G

ddPSK PSK

free PSK

free PSK8 4

82

4210− −

−

−

=⎛

⎝⎜⎜

⎞

⎠⎟⎟/ .log

( 2.3 )

where d free PSK8

2− and d free PSK4

2− are the squared free Euclidean distances of coded 8-PSK

and uncoded 4-PSK modulations respectively. 2.2.3 Codes obtained by Ungerboeck Codes represented in Figure 2.6 have been selected among equivalent codes because they can be identified as convolutional codes with rate k/(k+1) generated by systematic convolutional codes with feedback.

Figure 2.7: Realization by means of systematic convolutional encoder with feedback

In [3], Ungerboeck proposed an algorithm to find more powerful codes. These codes are given in table 1 for an 8-PSK modulation. ν is the constraint length and ~k is the number of bits protected by encoding. Indicated gains ( )G dBPSK PSK8 4/ are asymptotic gains and the parity check polynomials h0, h1 and h2 are presented in octal form.

2 Theory of trellis coded modulation 13

ν ~k h0 h1 h2 d free

212/ ∆ ( )G dBPSK PSK8 4/

2 1 5 2 - 2.000 3.0 3 2 11 02 04 2.293 3.6 4 2 23 04 16 2.586 4.1 5 2 45 16 34 2.879 4.6 6 2 105 036 074 3.000 4.8 7 2 203 014 016 3.172 5.0 8 2 405 250 176 3.465 5.4 9 2 1007 0164 0260 3.758 5.7 10 2 2003 0164 0770 3.758 5.7

Table 1: Codes for 8-PSK modulation

Table 1 shows that for the modulation with a constraint lengthν = 7 (used in the

next described CCSDS norm), an asymptotic gain of 5 dB can be achieved by using a coded 8-PSK modulation over uncoded 4-PSK modulation.

Simulation results in [3] are given on Figure 2.8. These simulations have been

made for constraint lengths equal to 2 and a 4-state minimal encoder.

Figure 2.8: Error-event and bit-error performances of coded 8-PSK and uncoded 4-PSK, 2 bits/T

On Figure 2.8, simulations show that for high SNR, asymptotic coding gains can be approached.

2 Theory of trellis coded modulation 14

2.3 Trellis Coded Multidimensional Phase Modulation The use of multidimensional modulations (called LD-MPSK-TCM) has several advantages that usually cannot be found with traditional TC-MPSK:

- Flexibility in achieving a variety of fractional information rates. - Codes which are partially or totally transparent to discrete phase rotations of

the signal set. - Higher decoder speeds resulting from the high rate codes used.

In the following paragraphs, a partitioning method for LD MPSK signal set will be

presented, the mapping and the general encoder structure will be detailed and then research results will be given concerning the optimal codes obtained. 2.3.1 Multi-D Signal Set Partitioning Similarly to 8-PSK modulation, the partitioning can be applied in a same way to a L x 8-PSK. As example, for a 2 x 8-PSK, integer y1 indicates the first 8-PSK point and y2 the second 8-PSK point (Figure 2.9).

Figure 2.9: 2 x 8-PSK signal set

Each point yj can be represented in binary form by the vector [ ]y j = y y yj j j

2 1 0, ,

with y ji ∈ 0 1, where y j = + +4 22 1 0y y yj j j for j = 1 2, .

To represent a 2 x 8-PSK signal point, we form the 2 x 3 binary matrix:

yyy2

=⎡

⎣⎢

⎤

⎦⎥ =

⎡

⎣⎢⎢

⎤

⎦⎥⎥

1 12

11

10

22

21

20

y y yy y y

Then y can be partitioned as for a 8-PSK modulation. Multi-dimensional partitioning has been studied in Appendix A on 2 common modulations: 2 x 8-PSK and 4 x 8-PSK. The method can be further applied to higher dimensions. As the mapping equation proposed in the following paragraph are the main interesting results of the partitioning, the detailed formation of this partitioning and result tables can be found in Appendix A.

2 Theory of trellis coded modulation 15

2.3.2 Construction of mapping equations

After iterations of the partitioning algorithm, beginning from the initial signal set of the modulation, the signal point can be represented by a combination of subsets and their cosets. Without entering into details of the cosets formation, the principal result of this formation (further reading can be found in [5]) is the signal point representation as:

( ) ( )y zy

yz z t

L

IL i i

i

IL

=

⎡

⎣

⎢⎢⎢

⎤

⎦

⎥⎥⎥= =

=

−

∑1

0

1

M Ω ( 2.4 )

where z zi i

i

IL

==

−

∑20

1

, with z for i ILi ∈ ≤ ≤ −0 1 0 1, and t are the generating vectors in

Appendix A.

Equation (2.4) can be used to describe a point in any L x MPSK constellation. The number of bits z j needed to describe each signal point is IL (with I M= log2 the number of required bits to represent an MPSK point and L the dimension of the modulation). If the least significant bit is used for coding, we can form a (IL-1)/IL rate code. A more convenient measure of rate is to use the average number of information bits transmitted during each 2-D signal period T. This is called the effective rate of the

code RIL

Lbit Teff =

−1( / ) .

Other rates can be achieved by setting the q least significant bits of the mapping to

zero. In this case, the mapping (2.4) can be rewritten as:

( )y zy

yz tq

L

j q j

j q

IL

=

⎡

⎣

⎢⎢⎢

⎤

⎦

⎥⎥⎥= −

=

−

∑1 1

M ( 2.5 )

for 0 2 1 0 11≤ ≤ − ≤ ≤ −− −z q LIL q , and where ( )y zq represents a point in an L x MPSK signal set such that the first q bits of (2.4) are zero.

From equation (2.5), the effective rates becomes RIL q

Leff =− −( )1

Example : 2 x 8-PSK mapping equation

After 6 iterations of the partitioning algorithm, beginning from the initial signal set, the equation (2.4) gives a single 2D signal point:

2 Theory of trellis coded modulation 16

( ) ( )y z

yy

z z z z z z z=⎡

⎣⎢

⎤

⎦⎥ = =

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥

1

2

6 5 4 3 2 1 044

04

22

02

11

01

8Ω (mod ) ( 2.6 )

where z zi i

i=

=∑2

0

5

, with z for ii ∈ ≤ ≤0 1 0 5, .

Since y1 and y2 can be described in terms of z, the signal set mapper can be

implemented using simple logic circuits as depicted in Figure 2.10.

Figure 2.10: 2 x 8-PSK signal set mappers with modulo-8 addition

2.3.3 Effect of a 360°/M phase rotation on a multi-D MPSK signal set Removing of phase ambiguity is a critical point for demodulation. After demodulation of the quadrature signals, it still remains a discrete phase ambiguity of k*π/M for a M-PSK. Using modulo-8 arithmetic in equation (2.4), the mapping can be done in a manner such that there are at most I bits affected by a signal set rotationΨ ≡ °360 / M . For 4-PSK, 8-PSK and 16-PSK this corresponds to rotations of 90°, 45° and 22.5°, respectively.

Consider a rotation by Ψ of the 1 x MPSK signal set with q = 0, what corresponds to the natural mapping. Since we use natural mapping, the integer representation of the rotated signal point is y y Mr = +1 (mod ) , where y is the integer representation of the signal point before rotation.

Consider the 2 x 8-PSK signal set, with the mapping given by equation (2.6). The signal outputs can be rewritten in terms of z as

( ) ( )1 5 3 1 4 2 0

2

1 04 2 4 2 (mod 8)

1 1y

z z z z z zy⎡ ⎤ ⎡ ⎤ ⎡ ⎤

= + + + + +⎢ ⎥ ⎢ ⎥ ⎢ ⎥⎣ ⎦ ⎣ ⎦⎣ ⎦ ( 2.7 )

2 Theory of trellis coded modulation 17

After a 45° rotation, we have )8(mod1+= yyr . We then deduce

( ) ( )1, 5 3 1 4 2 0

2,

1 04 2 1 4 2 (mod 8)

1 1r

r

yz z z z z z

y⎡ ⎤ ⎡ ⎤ ⎡ ⎤

= + + + + + +⎢ ⎥ ⎢ ⎥ ⎢ ⎥⎣ ⎦ ⎣ ⎦⎣ ⎦ ( 2.8 )

Note that a 1 is added to the term whose coset is [11]T. Hence this term “absorbs”

the effect of the phase rotation, leaving the remaining term unaffected. As can be seen, only bits z5, z3 and z1 are affected by the phase rotation, thus we can form the phase rotation equations from the modulo 8 addition rules:

z z z z z zz z z z z z z z z

r r r

r r r

0 0 2 2 4 4

1 1 3 3 1 5 5 1 31= = =

= ⊕ = ⊕ = ⊕ . ( 2.9 )

Using general notation, we deduce the following equation:

( )

y

yz z z g g g M

L

I p p p II I

I

11 1

1 02 21

12 21 1 0M K M K

⎡

⎣

⎢⎢⎢

⎤

⎦

⎥⎥⎥= + + +

⎡

⎣

⎢⎢⎢

⎤

⎦

⎥⎥⎥+ + + +− −

−− (mod )

( 2.10 )

where pj, for 0 1≤ ≤ −j I , corresponds to the partition levels

where [ ]t p j j j T= 2 2 2, , ,K . The term gj, for 0 1≤ ≤ −j I , corresponds to the remaining

terms that have at least one (but not all) component in t p with value 2 j . We can now write the rotation equations as:

z z z z z z z z zz z

rp p

rp p p

rp p p p

rp p

0 0 1 1 0 2 2 0 11= ⊕ = ⊕ = ⊕

=

, , . ,Kand for all other partition levels. ( 2.11 )

2 Theory of trellis coded modulation 18

2.3.4 The general encoder system

The general encoder system consists of three principal sections: a differential encoder, a binary convolutional encoder and a multidimensional mapper (Figure 2.11).

Figure 2.11: General encoder system

For the following, we only consider the case of a feedback systematic

convolutional encoder and polynomial notation is used. The parity check equation of an encoder describes the time relationship of the encoded bit streams. By using this notation, we write z j(D) = x j(D) for 1 ≤ j ≤ k where D is the delay operator. For a R = k/(k+1) code, the parity check equation is: ( ) ( ) ( ) ( ) ( ) ( ) ( )H D z D H D z D H D z D Dk k~ ~

⊕ ⊕ ⊕ =K 1 1 0 0 0 ( 2.12 ) where ~, ~ ,k k k1≤ ≤ is the number of input bits checked by the encoder,

( )H D j kj for 0 ≤ ≤ ~ is the parity check polynomial of ( )z Dj and ( )0 D is the all zero sequence. 2.3.4.1 The differential encoder Since the encoder is systematic, the differential encoder codes only the bits, which are affected by a phase rotation. The input bits into the encoder are coded and denoted w w wc c cs0 1 1, , ,K − . Figure 2.12 shows a differential encoder:

Figure 2.12: Differential encoder for general encoder

2 Theory of trellis coded modulation 19

2.3.4.2 Convolutional Encoder : Systematic research for good constraint length codes

An approximate lower bound for the symbol error probability of a multi-D code is given in [5] by

( )P eN

LQ

d R ENS

free free eff b≥

⎛

⎝⎜⎜

⎞

⎠⎟⎟

2

02 ( 2.13 )

where Reff is the effective rate and Eb/N0 is the energy per information bit to single-sided noise density ratio. The division by L normalizes the average number of errors per multi-D signal to that of a 2D signal set.

In [5], Pietrobon proposed a code research algorithm. The criteria used to find the best codes are the free Minimum Squared Euclidean Distance (MSED d free

2 ) and the

average number of nearest neighbors ( N free2 ). The search was limited to codes with

ν + ≤~k 10 whereν corresponds to the constraint length of the code and ~k to the number of bits protected by encoding.

We will not detail this algorithm and the interested reader may find more information in [5]. Tables 4 and 5 resume the results for two interesting cases for us: 4 x 8-PSK with effective rates of 2 bits/T (table 4) and 2.5 bits/T (table 5). ν ~k h4 h3 h2 h1 h0 d free

2 N free dnext2 Nnext γ (dB)

1 1 - - - 1 3 4.0 28 4.686 64 3.01 2 2 - - 2 3 5 4.0 12 4.686 32 3.01 3 3 - 02 04 03 11 4.0 4 4.686 16 3.01 4 4 10 04 02 03 21 4.686 8 - - 3.70 5 4 02 10 04 22 41 6.343 16 - - 5.01 6 4 034 044 016 036 107 6.686 6 - - 5.24 7 4 044 024 014 016 103 7.029 24 - - 5.46

Reff = 2.00 bits/T ; q = 3 ; du2 2 0= . ; ( )N x PSKu = 2 1 4 .

Table 4: Trellis coded 4 x 8-PSK for Reff = 2.00 bits/T

ν ~k h3 h2 h1 h0 d free2 N free dnext

2 Nnext γ (dB) 1 1 - - 1 3 2.0 8 2.343 64 2.32 2 2 - 2 1 5 2.343 40 - - 3.01 3 2 - 04 02 11 2.343 8 3.172 32 3.01 4 3 14 04 02 21 3.172 16 - - 4.33 5 3 24 14 02 41 3.515 64 - - 4.77 6 3 014 024 042 103 4.0 28 4.686 1088 5.33 7 3 034 024 016 103 4.686 12 - - 5.57 γ 4 135= − . dB ; Reff = 2.5 bits/T ; q = 1; du

2 1172= . ; ( )N x PSKu = 4 2 8 .

Table 5: Trellis coded 4 x 8-PSK for Reff = 2.50 bits/T

2 Theory of trellis coded modulation 20

The asymptotic coding gain of each code compared to the uncoded case, as shown in the code tables 4 and 5, is ( )γ = 10 10

2 2.log /d dfree u ( 2.14 ) where du

2 is the smallest MSSD of an equivalent uncoded 2-D or multi-D scheme.

In [5], the best asymptotic coding gain achieved by multidimensional TCM is close to 5.5 dB. The next described CCSDS norm will use a constraint length of 7 which achieves an average asymptotic gain of 5.5 dB over an uncoded 4-PSK (see bold rows of Tables 4 and 5).

2 Theory of trellis coded modulation 21

2.4 Decoding algorithm The decoding algorithm of multidimensional trellis coded modulation is based on the well-known Viterbi algorithm. The convolutional encoding in the modulation implies a decoding by trellis. Nevertheless, there are two methods based on this Viterbi algorithm to decode trellis-coded modulation. The first one can be considered as a “brute-force” method whereas the second one is a simpler approach and will consequently be the main issue of this paragraph. 2.4.1 Brute-force approach The trellis used for decoding has 2 1ν− states and each transition has 2 k k−~

parallel branches where ν is the constraint length of the code, k the number of transmitted bits before encoding and ~k the number of encoded bits by the convolutional encoder.

The Viterbi decoder must determine which one of the 2 k k−~ parallel transitions is

the closest to the received signal, in a maximum likelihood sense. This brute-force method proposes to calculate the metric (Euclidean distance) associated to each of the 2 k k−~

parallel transitions and then find the minimum. This implies at least 2 1k k− −~

comparisons. Moreover, since ~k bits are encoded, there are 2 1~k + transitions merging into a state what leads to a total of 2 21 1k k+ +−

~ comparisons to determine the best

transition merging into a single state. Adding the fact that the trellis has 2 1ν− states and that this operation has to be repeated for each state, this is an unacceptably large number of computations for large values of k and small values of ~k .

As an example, let us determine the number of metrics to be calculated and the number of required comparisons for a transmission of 2 bits/symbol ( k k= =8 3 and ~ ) with a 64-states trellis which correspond to the next described CCSDS norm. The trellis has 64 states, what means that 2 2 2 2 21 4 5 9~ ~k k k+ −× = × = metrics must be computed for each state and a total of 2 64 327689 × = metrics has to be computed per 4-dimensional symbol received. In addition, 2 2 2 2 4961 1 9 4k k+ +− = − =

~ comparisons per state and

496 64 31744× = comparisons per 4-dimensional symbol received have to be computed.

Consequently, this method will not be used due to the complexity. The second

method will show that it is possible to greatly reduce the number of computations using the fact that signals constructed by codes have been optimized for Euclidean distance.

2 Theory of trellis coded modulation 22

2.4.2 Simpler approach The second method comes from [5] and requires a second trellis, called “auxiliary trellis” in the following, to avoid mixing up with the main trellis from the convolutional encoder.

This auxiliary trellis is constructed from the mapping equations. To explain the construction of this trellis, we will study a simple example: the 2 x 8-PSK modulation with ~k = 2 and the transmission of 2.5 bits/symbol. From equations (2.4) and (2.6), we deduce the following partitioning:

( ) ( )z x

zz

x x x x x x x=⎡

⎣⎢

⎤

⎦⎥ = =

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥ +

⎡

⎣⎢⎤

⎦⎥

1

2

6 5 4 3 2 1 044

04

22

02

11

01

8Ω (mod ) ( 2.15 )

where x xi i

i=

=∑2

0

5

, with x for ii ∈ ≤ ≤0 1 0 5, .

The auxiliary trellis has the particularity of being of finite length, while the main

trellis could be infinite with a continuous stream of information. This length corresponds to the number of output symbols of the considered modulation. In our example, this length is L = 2. There are 8 sets of parallel branches corresponding to all the combinations of x2x1x0 and each set has 8 possible paths (Figure 2.13 and Figure 2.14).

Figure 2.13: Full parallel transitions decoding trellis for 2 x 8-PSK signal set

Figure 2.14: Parallel transition decoding trellis for z = 000 and 2 x 8-PSK signal set

0 0 0

1 0 0

0 0 1

1 0 1

0 1 0

1 1 0

0 1 1

1 1 1

x2x1x0

C0

C2

C1

C3

C1

C1

C0 C2 C2 C0 C1 C3 C3

C2

C2 C2 C0 C1 C3 C3

2 Theory of trellis coded modulation 23

In Figure 2.13 and Figure 2.14, the C ii , ...= 1 3 represent the subsets of the 8-PSK

partitioning as seen in Figure 2.4. The algorithm follows these steps (applied to the example of the figures):

- Receiving the first symbol, a hard decision is taken in the first step of the auxiliary trellis. Thus, the decoder chooses which of symbol 0 or 4 is closest to the received symbol, calculates and computes the Euclidean distance between the chosen symbol and the received symbol. The same operation is done to choose between symbols 2 and 6.

- Receiving the second symbol, the first operation is repeated. But this time, the cumulated metric is calculated and computed.

- After these two steps, there are only two parallel branches merging into state 000. Then, only one metric comparison is done: the lowest metric and the associated path are memorized.

- For each step of the principal trellis, an auxiliary trellis is constructed with the closest branch entering one state and its associated metric.

- In the last step we apply the classical Viterbi algorithm with the help of the previously calculated metrics (from the auxiliary trellis).

To illustrate this example, consider Figure 2.14 : At step 1, the decoder makes a hard decision in subset C0 and chooses between

symbols 0 and 4. Suppose that the decoder chooses symbol 0 with metric m. Simultaneously, it chooses the most probable symbol in subset C2. Consider that it chooses symbol 6 with metric m’.

At step 2, the decoder receives the second symbol (from the second dimension) and makes a similar decision. Consider that it chooses respectively symbols 4 and 6 in subsets C0 and C2 with metrics n and n’.

The cumulated metrics are then l = m + n and l’ = m’ + n’. If l < l’, then point 04 gives z5 = 0, z4 = 1 and z3 = 0 from equation (2.6). If l > l’, then point 66 gives z5 = 1, z4 = 0 and z3 = 1 from to the same equation.

The same operations are repeated for the eight final states of the auxiliary trellis. This auxiliary trellis is then used for each transition of the main trellis in order to determine the parallel branch closest to the received symbols.

For each transition of the principal trellis, we know which parallel branch has been retained. The final principal trellis is just like a traditional one without any parallel branch. As the metrics have already been calculated, the Viterbi algorithm can be applied without any difficulty to decode the received symbols.

3 CCSDS Norm: 4-D 8-PSK Trellis Coded Modulation 24

3 CCSDS Norm: 4-D 8-PSK Trellis Coded Modulation

3.1 General principle of the 4-D 8-PSK TCM Encoder As already seen in paragraph 2.3.3., the coding structure of a multidimensional trellis coded modulation combines a serial to parallel converter, a differential encoder, a convolutional encoder, a constellation mapper and an 8-PSK modulator (Figure 3.1).

Figure 3.1: General principle of the 4-D 8-PSK TCM Encoder

The CCSDS norm [6] proposes 4 effective rates: 2 bits/symbol, 2.25 bits/symbol,

2.50 bits/symbol and 2.75 bits/symbol. In the following paragraphs, the 2 bits/symbol transmission is only mentioned. The other rates are really similar to the chosen one, the interested reader can have a look on the CCSDS recommendations [6]. The coding structure is characterized by the following parameters:

- Size of the constellation: M = 8 phase states (8-PSK); - Number of signal set constituent: L = 4; - Number of states for the trellis encoder: 64; - Rate of the convolutional encoder used for the construction of the trellis: R =

¾; - Rate of the modulation: Rm = m / (m+1) selectable to 8/9, 9/10, 10/11, or

11/12; - Efficiency of the modulation (ratio of 8,9,10 or 11 input bits to 4, the number

of successively transmitted 8-PSK symbols): • Reff = 2 bits per channel-symbol (for Rm = 8/9); • Reff = 2.25 bits per channel-symbol (for Rm = 9/10); • Reff = 2.5 bits per channel-symbol (for Rm = 10/11); • Reff = 2.75 bits per channel-symbol (for Rm = 11/12);

3 CCSDS Norm: 4-D 8-PSK Trellis Coded Modulation 25

A differential encoder located prior to the convolutional encoder resolves the

carrier phase ambiguity. Spectral efficiency of 2 bits/s/Hz is achieved with the constellation mapper.

3.2 Trellis encoder structure The convolutional encoder recommended is a systematic feedback encoder and comes from Pietrobon’s works [5]. This encoder must be implemented with the following characteristics:

- Number of states: 64 - Constraint length: ν = 7 - Rate: R = ¾

The same coding structure is used for all effective rates and its representation is

given in Figure 3.2. The corresponding polynomials coefficients (in octal) are:

hhhh

3

2

1

0

050024006103

=

=

=

=

⎧

⎨

⎪⎪

⎩

⎪⎪

Figure 3.2: Convolutional encoder, rate ¾

The advantages of this encoder are its optimized performances in term of coding

gain and its reduced internal rate, which is equal to 1/8 of the information rate for a rate of 2 bits/symbol. 3.3 Constellation Mappers for 4-D 8-PSK TCM To achieve an effective rate of Reff = 2.00 bits/T, from equation (2.5) and table 3, we can deduce the 8 dimensional mapper used:

3 CCSDS Norm: 4-D 8-PSK Trellis Coded Modulation 26

( ) ( ) ( )( )( )

( )

( ) ( ) ( )

( )

( )

( ) ( ) ( )

zzzz

x x xx

x

x x x

x

x

x x x

( )

( )

( )

( )

. . . (mod )

0

1

2

3

8 5 17

6

7 6 4

3

2

3 2 0

4 2

1111

4

0

2

0

8

⎡

⎣

⎢⎢⎢⎢⎢

⎤

⎦

⎥⎥⎥⎥⎥

= + +

⎡

⎣

⎢⎢⎢⎢

⎤

⎦

⎥⎥⎥⎥

+

⊕ ⊕

⎡

⎣

⎢⎢⎢⎢⎢

⎤

⎦

⎥⎥⎥⎥⎥

+

⊕ ⊕

⎡

⎣

⎢⎢⎢⎢⎢

⎤

⎦

⎥⎥⎥⎥⎥

⎧

⎨

⎪⎪

⎩

⎪⎪

⎫

⎬

⎪⎪

⎭

⎪⎪

Symbols ( )z ii , ...= 0 3 , correspond to the four symbols of the 8-PSK modulation.

This representation shows that bits 1, 5 and 8, which are common to each vector set, are sensitive to a phase rotation of π/4 and thus they will be differentially encoded.

The implementation of this mapper is in Figure 3.3.

Figure 3.3: Constellation mapper for a 2 bits/symbol transmission

3.4 Differential encoder The differential encoder depicted in Figure 3.4 is used to eliminate phase ambiguity on carrier synchronization.

3 CCSDS Norm: 4-D 8-PSK Trellis Coded Modulation 27

Figure 3.4: Differential encoder for 2 bits/symbol

3.5 Application of the decoding algorithm to the CCSDS norm The convolutional encoder has 64 states and the corresponding trellis is detailed in the table of Appendix C. In this table, the first column corresponds to the present state, the second column contains the input bits of the convolutional encoder, the third one contains the following state and the last one contains the output encoded bit of the convolutional encoder.

To illustrate the use of the auxiliary trellis, consider the transmission of 2

bits/symbol. The mapping equation given by the norm is:

( ) ( ) ( )( )( )

( )

( ) ( ) ( )

( )

( )

( ) ( ) ( )

zzzz

x x xx

x

x x x

x

x

x x x

( )

( )

( )

( )

. . . (mod )

0

1

2

3

8 5 17

6

7 6 4

3

2

3 2 0

4 2

1111

4

0

2

0

8

⎡

⎣

⎢⎢⎢⎢⎢

⎤

⎦

⎥⎥⎥⎥⎥

= + +

⎡

⎣

⎢⎢⎢⎢

⎤

⎦

⎥⎥⎥⎥

+

⊕ ⊕

⎡

⎣

⎢⎢⎢⎢⎢

⎤

⎦

⎥⎥⎥⎥⎥

+

⊕ ⊕

⎡

⎣

⎢⎢⎢⎢⎢

⎤

⎦

⎥⎥⎥⎥⎥

⎧

⎨

⎪⎪

⎩

⎪⎪

⎫

⎬

⎪⎪

⎭

⎪⎪

This mapping produces 4 symbols since the modulation has 8 dimensions. This means that a final state of the auxiliary trellis is obtained after four steps (this is the reason for the finite length of the trellis). By calculating each symbol z(i), i = 0…3, received for any possible combination of x(8)x(7)x(6)x(5)x(4) we can find all possible paths through the trellis. At each step the signal correspond to a class Ci, i = 0…3, of Figure 2.13. As an example, consider final state x(3)x(2)x(1)x(0) = [0000] in table 6.

( ) ( ) ( ) ( ) ( )x x x x x8 7 6 5 4 z z z z0 1 2 3 Path 00000 0 0 0 0 C0C0C0C0 00001 0 0 0 4 C0C0C0C0

3 CCSDS Norm: 4-D 8-PSK Trellis Coded Modulation 28

00010 2 2 2 2 C2C2C2C2 00011 2 2 2 6 C2C2C2C2 00100 0 0 4 4 C0C0C0C0 00101 0 0 4 0 C0C0C0C0 00110 2 2 6 6 C2C2C2C2 00111 2 2 6 2 C2C2C2C2 01000 0 4 0 4 C0C0C0C0 01001 0 4 0 0 C0C0C0C0 01010 2 6 2 6 C2C2C2C2 01011 2 6 2 2 C2C2C2C2 01100 0 4 4 0 C0C0C0C0 01101 0 4 4 4 C0C0C0C0 01110 2 6 6 2 C2C2C2C2 01111 2 6 6 6 C2C2C2C2 10000 4 4 4 4 C0C0C0C0 10001 4 4 4 0 C0C0C0C0 10010 6 6 6 6 C2C2C2C2 10011 6 6 6 2 C2C2C2C2 10100 4 4 0 0 C0C0C0C0 10101 4 4 0 4 C0C0C0C0 10110 6 6 2 2 C2C2C2C2 10111 6 6 2 6 C2C2C2C2 11000 4 0 4 0 C0C0C0C0 11001 4 0 4 4 C0C0C0C0 11010 6 2 6 2 C2C2C2C2 11011 6 2 6 6 C2C2C2C2 11100 4 0 0 4 C0C0C0C0 11101 4 0 0 0 C0C0C0C0 11110 6 2 2 6 C2C2C2C2 11111 6 2 2 2 C2C2C2C2

Table 6: All possible paths merging into state 0000

Paths C0C0C0C0 and C2C2C2C2 are the only ones to merge into state 0000. The auxiliary trellis is designed by repeating the same operation for each final state. This trellis is depicted for a 2 bits/symbol transmission in Figure 3.5. Auxiliary trellis for the 3 other rates are obtained in a similar way. In fact, there are 8 paths merging into each state for this transmission rate.

3 CCSDS Norm: 4-D 8-PSK Trellis Coded Modulation 29

Figure 3.5: Auxiliary trellis for 2 bits/symbol transmission according to CCSDS norm

4 Simulation results 30

4 Simulation results

In this paragraph, all simulations have been implemented in C language under Visual C++. The simulations are made for the whole transmission chain: emission, channel and reception.

Concerning the channel, it is simulated with an AWGN (Additive White Gaussian Noise). Since no Gaussian variable is directly available in C-language, this AWGN had to be emulated. In [9], two methods are proposed: the Central limit theorem method or the Box-Muller method. The first one is chosen. The Central limit theorem states that the sum of N random numbers will approach normal distribution as N approaches infinity.

4 Simulation results 31

4.1 Simulation results for QPSK and 8-PSK Before giving the results of the Trellis Coded Modulation, the performances of QPSK and 8-PSK modulations will be studied as references. We will then see the coding gains obtained over uncoded modulations by the Trellis Coded Modulation. It will also validate the first part of our transmission chain.

Final results are shown in Figure 4.1. The large lines correspond to the symbol error probability SER: it means that an error is counted if a received symbol is false (at least one out of two bits for a QPSK modulation and at least one out of three bits for an 8-PSK modulation is false). The normal lines correspond to the classical Bit Error Rate (BER) in which each error on a bit is counted.

It can be seen that there is a ratio of 3-4 dB between bit error rate and symbol error rate for the QPSK modulation. Actually, this is due to the fact that the QPSK modulation works with 2 bit-symbols. The energy per bit is then divided by 2 what means a loss of 3 dB.

The same reasons can be involved to explain the difference between the 8-PSK symbol error rate and bit error rate.

To conclude, verification has been made with theoretical results: the references [3] and [10] are similar to these simulations that is why these can be used as references for our following works. It also confirms that the chain is well simulated.

Figure 4.1: QPSK and 8-PSK symbol and bit error rates

4 Simulation results 32

4.2 Simulation results for a 4 dimensional 8-PSK TCM 4.2.1 Comparisons between 4D 8-PSK TCM and QPSK modulations To determine the coding gain achieved by the 4-dimensional trellis coded 8-PSK modulation, a 2.0 bits/symbol transmission is considered to make an easy comparison with QPSK modulation. Bit error and symbol error rates have been simulated. Results are depicted in Figure 4.2 and Figure 4.3.

Figure 4.2: Comparison of TCM, 8PSK and QPSK for a 2.0 bits/symbol transmission

As shown in Figure 4.2 and Figure 4.3, 4D 8-PSK TCM achieves a BER = 10-4 at Eb/N0 = 6.1 dB and at a SER = 10-4 Eb/N0 = 9.1 dB. For a QPSK modulation, the same BER is achieved at Eb/N0 = 8.5 dB and at Eb/N0 = 11.7 dB for the SER.

Moreover, a comparison between the three bit error rates would give, at bit error

probability BER = 10-4, Eb/N0 = 6.1 dB for 4D 8-PSK TCM, Eb/N0 = 10.8 dB for 8PSK modulation and Eb/N0 = 8.5 dB for QPSK modulation. Multidimensional trellis coded modulation implies a gain of 2.4 dB over QPSK modulation at BER = 10-4 and a gain of 4.7 dB over 8-PSK modulation at BER = 10-4

4 Simulation results 33

Figure 4.3: Zoom of Figure 4.2

4.2.2 Comparisons between hard and soft decisions in decoding To show the performance of soft decoding, consider that a demodulator is located before the decoding block. This means that each symbol received is mapped to the closest one (in Euclidean distance) before beginning the decoding algorithm. This method is called “hard decoding”. The results are depicted in Figure 4.4 and Figure 4.5.

These results show that soft decoding is much more efficient than hard decoding, but hard decoding in TCM is still better than a QPSK modulation.

4 Simulation results 34

Figure 4.4: Comparison between soft and hard decoding

Figure 4.5: Zoom of Figure 4.4

4 Simulation results 35

Figure 4.4 and Figure 4.5 show that a BER = 10-5 is achieved at Eb/N0 = 6.7 dB for soft decoding, Eb/N0 = 8.2 dB for hard decoding and Eb/N0 = 9.6 dB for QPSK modulation. Soft decoding implies a gain of 1.5 dB, for the bit error rate at BER = 10-5, over hard decoding and hard decoding implies a gain of 1.4 dB over QPSK modulation at the same BER.

The same comparisons at a lower BER, for example BER = 10-4, give the

following results: soft decoding in TCM implies a gain of 1.5 dB, for the bit error rate, over hard decoding and hard decoding implies a gain of 1.0 dB over QPSK modulation. 4.2.3 Influence of quantization parameters on performances Using the C++ simulation chain, the effects of quantization are studied in different parts of the receiver chain. Quantization effects of the signals can be simulated at three different stages of the receiver: I-Q signals, branch metrics and state metrics. 4.2.3.1 Influence of quadrature and in-phase signals quantization Results are shown in Figure 4.6 and Figure 4.7. They represent the effects of this quantization on the bit error probability. The metric is quantized on 7 bits. Simulations with 3, 4, 5, 6 and 8 bits are represented and compared to the reference curve of the unquantized signals.

Figure 4.6: Influence of signal quantization on the bit error probability

4 Simulation results 36

Figure 4.7: Zoom of Figure 4.6

Quantization on 5 or 6 bits does not affect the performances, in terms of bit error

probability of the system. With a quantization on 4 bits, at BER = 10-4, there is a loss of 0.7 dB and with 3 bits a loss of 2.5 dB is achieved and the performances are similar to the QPSK modulation! The 8 bits curve strangely seems to be better than the unquantized curve: This is probably due to a lack of computation time in the last point.

The best solution in terms of signal quantization would certainly be to quantize on 5 or 6 bits. The simultaneous simulation of metric quantization and signal quantization will give the best trade-off between cost and performances. 4.2.3.2 Influence of metrics quantization To see the influence of the metric’s quantization, let the signals received be floats. As already said in paragraph 2.5, the metrics are calculated using the auxiliary trellis. It means that a metric is calculated at each received symbol and the metric transmitted to the Viterbi algorithm corresponds to a four-symbol metric.

This quantization is more critical for the FPGA implementation. Each bit saved will largely decrease the size of the chain and increase the speed of the receiver.

In the simulation, the maximum Euclidean distance between a received symbol and an 8-PSK symbol is set to 3. This implies a large margin due to noise and could have been lowered. To quantize a metric, we then consider the interval [0;3] and share

4 Simulation results 37

it into 2quant_param parts in a linear manner. Simulation results are given in Figure 4.8 and Figure 4.9 for 3, 4, 5 and 7 quantization bits. The others signals are quantized on 8 bits since we just want to study the effect of the metric quantization.

Figure 4.8: Influence of metric quantization on the bit error rate

4 Simulation results 38

Figure 4.9: Zoom of Figure 4.8

In Figure 4.8 and Figure 4.9, the bit error rate is the only one concerned. We can make a comparison of several metric quantizations. In fact, we see that a metric calculated on 7, 5 or 4 bits does not affect the performances so much. There is a difference of 0.2 dB maximum (at BER = 10-4) with an unquantized metric. On the opposite, a metric calculated on 3 bits implies a loss of approximately 0.8 dB (at same BER) on unquantized metric.

As a conclusion, a good trade-off between performance and cost would be to

calculate a metric on 4 bits. This choice will be really interesting for FPGA implementation. 4.2.3.3 Influence of simultaneous quantizations In this paragraph, the best solution to implement the CCSDS multidimensional trellis coded modulation on a FPGA will be analyzed. Contrary to paragraph 4.2.3.2, the maximal metric is considered equal to the Euclidean distance “2” and this will show better results. Simulation results are depicted for 3 cases:

Channel signals on 7 bits and metrics on 3 bits, Channel signals on 6 bits and metrics on 4 bits, Channel signals on 6 bits and metrics on 3 bits.

4 Simulation results 39

As shown in Figure 4.10, a good trade-off to quantize both signals and metrics is to represent the signals on 7 bits and the metrics on 3 bits or the signals on 6 bits and the metrics on 4 bits. The results seem to be the same at high SNR.

The final choice for the implementation is: 6 bits for the I-Q signals and 4 bits for

the metrics.

Figure 4.10: Influence of quantization on the bit error rate

5 VHDL implementation of the transmission chain 40

5 VHDL implementation of the transmission chain

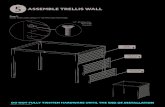

In this paragraph, the chosen architecture for the transmission chain will be described. The chain is divided in 3 blocks: encoder, channel simulator and decoder. Only the last block is interesting for the final use but the 2 others will be very useful to test the implementation. 5.1 Implementation of the TCM encoder 5.1.1 Global architecture The TCM encoder had been implemented as mentioned in the CCSDS norm (§ 3). This block is for test only; therefore it will not be optimized in resource. The encoder will encode the input word of 8 bits (for a 2 bits/s modulation rate) into 4 symbols which are coded with 4 I-Q couples.

Figure 5.1: Encoder structure

Input_word 8

6I1

Q1

6I0

Q0

6I3

Q3

6I2

Q2

Encoder

en_in en_out

CLK

5 VHDL implementation of the transmission chain 41

Figure 5.2: CCSDS global encoder's architecture

Figure 5.2 reminds the CCSDS global architecture of this encoder. A differential

encoder, a convolutional encoder, a constellation mapper and a ROM, used as a table, to quantize the signals constitute it. The ROM contains the quantization values of parameters I-Q for the 8 possible symbols of the 8 PSK constellation. The I Q signals are quantized on 6 bits. Thus, the unsigned values for these signals are between 0 and 63. The following quantization function will be used for the symbols:

Quantified symbol EIQ_ =⎛⎝⎜

⎞⎠⎟ +

⎡

⎣⎢

⎤

⎦⎥

24

22

6 6

where 6 is the numbers of bits used in the quantization, 4 the width of the interval in which I and Q signals can be. This method gives the following quantization values of each symbol:

Symbol I Q

0 47 38

1 38 47

2 25 47

3 16 38

4 16 25

5 25 16

6 38 16

7 47 25

5 VHDL implementation of the transmission chain 42

The extreme values for I and Q without noise are 47 and 16, which give a margin of 16 for the noise. 5.1.2 Components of the coding system These blocks are easy to implement, they are only the translation of the CCSDS description (paragraphs 3.2, 3.3 and 3.4). They use only mod-2 adders and logic gates.

Figure 5.3: Structure of the differential encoder

Figure 5.4: Structure of the convolutional encoder

input_word 8

DifferentialEncoder

CLK

en_in en_out

8diff coded word

input_word 8

ConvolutionalEncoder

CLK

en_in en_out

9conv_coded_word

5 VHDL implementation of the transmission chain 43

Figure 5.5: Structure of the constellation mapper

The quantization table, described in Figure 5.6, converts an 8-PSK symbol in an in-phase I and a quadrature Q signals on 6 bits each.

Figure 5.6: Structure of the quantization table

Constellation mapper

CLK

en_in en_out

input_map 9

3Symb0

3Symb1

3Symb2

3Symb3

Symb0 3

Quantization table

(ROM)

CLK

en_in en_out

6I1

Q1

6I0

Q0

6I3

Q3

6I2

Q2

Symb1 3

Symb2 3

Symb3 3

5 VHDL implementation of the transmission chain 44

5.2 Implementation of the TCM decoder The TCM decoder can be divided into 3 parts: the transition metric calculator, the Viterbi decoder and the demapper + differential decoder. The transition metric calculator computes the metric values of 16 possible metric transitions for the trellis. The Viterbi decoder will find the most probable transition for each step of the trellis. The last part will demap the selected transition and the path characteristics to find the output word of 8 bits.

For the transition metric calculator and the Viterbi decoder, two architectures are

possible: serial or parallel architecture. The serial architecture will decrease the number of occupied resources whereas the parallel architecture will increase the decoding speed. As we want the highest achievable data rate, we will use a parallelized architecture when it's possible.

Contrary to the encoding part, the decoder will be the final product in the receiver

system. Therefore it becomes really important to optimize the speed and the occupied size of the decoding part. For each block, a large effort will be made to improve both constraints. And finally a reasonable trade-off will be made between speed and size.

The general decoding system is depicted in Figure 5.7.

Figure 5.7: General architecture of the decoding system

16x6

Branch_met0…15

Path memory

2*16 bits

out word

8

selected_transition

4

Transition Metric

Calculator

CLK

6I3

6Q3

6Q0

6I0

CLK

Differential

Decoder

CLK

Demapper

CLK

Viterbi Decoder

5 VHDL implementation of the transmission chain 45

5.2.1 Transition Metric Calculator: the parallel architecture 5.2.1.1 Architecture This block implements the algorithm, called “simpler approach” in paragraph 2.4.2. As high data rate is targeted, it will be parallelized as much as possible. This decoder is implemented in three blocks:

- A table (RAMs or ROMs) which delivers the symbol chosen in a class for each symbol received and the corresponding metric between the symbol received and the chosen symbol in a class,

- An “Add - Compare - Select” operation, delivering 4 symbols and the associated metric for each final state of the auxiliary trellis: 4 symbols and one metric for each surviving branch of the auxiliary trellis.

The inputs of the hard decoder (see Figure 5.8) are the quantized (6 bits) in-phase

and quadrature signals of the 4 symbols and the outputs are 16 words (9 bits) and 16 corresponding metrics (12 bits).

Figure 5.8: Transition metric calculator bloc

Transition

Metric

Calculator

CLK

enable_in

I0

Q0

6 5 Branch_metric0

Branch_metric15

I1

Q1

6

I2

Q2

6

I3

Q3

6

vect_decm

166 vect_dec

1k

enable_out

5 VHDL implementation of the transmission chain 46

5.2.1.2 Detailed architecture of the transition metric calculator As already said, the branch metric calculator can be implemented in two successive blocks (see Figure 5.9): “RAM metric” and “Decod_acs”. The further paragraphs will detail the implementation and the behavior of these blocks.

Figure 5.9: Detailed architecture of the branch metric calculator

5.2.1.2.1 “RAM metric” block

RAMs of 16 kbits will be used since these components are already included in the FPGA. Several architectures are possible: as we use an addressing on 12 bits (if the received symbols are represented on 6 bits), the selected RAMs will be 4 4k × output bits. 5 RAMs of this type are then necessary per received symbol: one for each of the 4 classes (concerning the metrics) and one for the symbol decision inside a class.

One table delivers the choices between 8-PSK signals of a same class (this means

that a choice is made between 0 and 4, 1 and 5, 2 and 6, 3 and 7) and the corresponding metric (Euclidean distance between the received signal and an 8-PSK signal). For each received symbol, a table then delivers 4 symbols and 4 metrics. Since there are 4 symbols in parallel, the global block delivers 16 symbols (only one bit) and 16 associated metrics (on 4 bits). The following Figure 5.10 describes the architecture of one of the four RAMs table.

With dual port RAMs, which can be accessed by two independent addresses, this

implementation occupies (4*5)/2 = 10 RAMs.

en_in

16

distance0,0

distance0,1

distance3,3

distance0,3

distance1,0

en in

RAM metric

CLK en_out

I0

Q0

6

I3

Q3

vect_dec

3

16

3

CLK

Decod_acs

5 metric0

metric15

16 vect_decm

16 vect_dec

en_out

5 VHDL implementation of the transmission chain 47

Figure 5.10: One parallel RAM table

As an example, let us take I and Q represented each one on 6 bits. The RAMs

have addresses on 12 bits constituted by the concatenation [I Q], where the most significant bit is at left (MSB: I and LSB: Q). The RAM then delivers “metric0”: the 4 MSBs represent the metric between the received symbol and the nearest symbol of class 0 (symbol 0 or 4)…the 4 LSB represent the metric between the received symbol and the nearest symbol of class 3 (symbol 3 or 7). The 4 MSBs of “dec” (decision vector) correspond to the choice between the symbols of a class: the MSB corresponds to class 0, the second MSB corresponds to class 1 and so on… A decision bit at 0 corresponds to symbols 0, 1, 2 or 3 whereas a bit set to 1 corresponds to symbols 4, 5, 6 or 7. 5.2.1.2.2 “Decod_ACS” block

Figure 5.11: Architecture of "decod_acs"

1

enable in

CLK

enable_out

3distance0,0

distance0,1

distance0,3

distance0,2

dec0,0

dec0,1

dec0,2

dec0,3

I 6

Q

5 RAMs of 4k x 4 bits

enable_in

distance0,0

distance0,1

distance3,3

distance0,3

distance1,0

5 metric0

metric15

3

CLK

enable_out

Decod_acs 16 vect_decm

5 VHDL implementation of the transmission chain 48

The Add – Compare – Select (ACS) decoder block (Figure 5.11) has been

parallelized by 16 ACS blocks. Each block is dedicated to one of the possible final state in the auxiliary trellis previously mentioned. 3 successive operations are made in these blocks. The first one consists of adding 4 distances in a particular way: the auxiliary trellis, determines the input combination of each adder of this block. This means that the adders have 4 inputs on 4 bits and an output on 6 bits. The inputs are the metrics associated to a class signal.

The second part of the “ACS” block is a comparator: since two parallel paths are

merging into each final state of the auxiliary trellis (for the 2 bits/symbol transmission), this comparator determines which path is the survivor among two: it is the one with the highest metric.

The last part consists in a selection between the two compared paths. The path

with the highest metric is the survivor: the selection is delivered on one bit in “vect_decm”.

This block has 16 metrics on 4 bits as inputs. The outputs of the ACS block are the surviving metrics and a decision bit per path (described by a 16-bit vector), corresponding to the entering upper or lower path (0 corresponds to the upper path in auxiliary trellis and 1 corresponds to the lower one).

One of the 16 “ACS unit” blocks can be represented like in following Figure 5.12:

Figure 5.12: One small ACS unit block

5metric

ACS_a

CLK

enable_out enable_in

1 decm

3 distance0,a

distance3,b

5 VHDL implementation of the transmission chain 49

5.2.2 The Viterbi decoder 5.2.2.1 General architecture The Viterbi decoder receives 16 branch metrics (on 5 bits) and outputs the selected transition in the trellis on 4 bits (16 possible transitions). This Viterbi decoder is implemented with the 'trace-back' method, which consists to choose the survivor form the first node of the trellis only, assuming a sufficient truncation length. The Viterbi algorithm is applied to the 64 states with 8 branches per state.

Figure 5.13: Viterbi Decoder block

This second main block is itself constituted by 4 blocks linked together as

specified in Figure 5.14. There is one 'Add-Compare-Select' (ACS) block, which determines the surviving path, among 8, entering each state of the trellis. A metric scaler is also used to avoid metrics overflow and to limit the representation of state metrics on 12 bits. A traceback block decodes the correct word by reading the path through the trellis. Finally, a LIFO reverses the data from traceback, as trellis is decoded in reverse order.

5

CLK

Viterbi decoder

4 selected_transition

enable_in

in_metric15

in_metric0

enable_out

5 VHDL implementation of the transmission chain 50

Figure 5.14: Description of the Viterbi decoder

Metric scaler

CLK

ACS Viterbi

CLK

Trace back

4

out_data

enable_in

in_metric15

in_metric0 5

CLK

LIFO

selected_transitions

64x3

64x8

scaled_metrics

64x8 state_metrics

selected_transition

4

5 VHDL implementation of the transmission chain 51

5.2.2.2 Components of the Viterbi decoder 5.2.2.2.1 “ACS Viterbi” block

Figure 5.15: ACS Viterbi bloc

Given the branch metrics, the ACS Viterbi block

states according to the trellis. The inputs of the ACtransition metrics and 64 8-bit state metrics. The output64 3-bit transition indexes. As the even transitions are oand odd transitions for states between 32 and 63, we output by coding on only 3 bits instead of 4.

Since this block (Figure 5.15) is the only recu

achievable data rate of the implementation is determirecursion. Therefore, this block is the bottleneck of all ththe main optimization effort. The speed of the global ACthe reference clock divided by the number of flip-flopAfter many optimizations, the optimal configuration reaAs a 120 Mhz clock is used, delivered by the reference cglobal speed of the ACS Viterbi block is 40 Mhz for a fu

Depending on the speed/size trade-off, this blo

parallelized with 64 ACS 'processing elements' (PE), eatrade-off configurations will be implemented: totally par40 Mhz) and serialized on 2 levels (32 PEs, 4 flip-flops –

CLK

ACS Viterbi

enable_in

state_metrics

64x8

state_metrics

branch_metric15

branch_metric0 5

64x3

64x8

k

calculates the metrics of the 64 S Viterbi block are 16 5-bits s are 64 7-bit state metrics and nly for states between 0 and 31 can save one bit for the ACS

rsive part of the decoder, the ned by the speed of this ACS e system and it will concentrate S Viterbi block will be equal to s between the recursion loop. ched a number of 3 flip-flops. lock of the receiver system, the lly parallelized architecture.

ck can be partially or totally ch one processing one state. 2 allelized (64 PEs, 3 flip-flops – 30 Mhz).

enable_out

out_transitions

5 VHDL implementation of the transmission chain 52

5.2.2.2.2 “Metric scaler” block

Due to the repeated accumulation of transition metrics to state metrics, the magnitude of these metrics is potentially unbounded. Hence, metric normalization schemes are necessary to avoid overflow. Several methods for state metric normalization are known, which are based on two facts: • The differences between all state metrics at any trellis step are bounded in

magnitude by a fixed quantity independent of the number of ACS operations already performed in the trellis.

• A common value may be subtracted from all state metrics for any trellis step, since the subtraction of a common value does not have any impact on the differences for metric comparisons.

Due to speed constraint, the fastest method is used. Instead of computing the

minimum metric for each step, we will use the lower bound of the difference between two states metrics. When one of the 64 state metrics is above a fixed threshold, we normalize all state metrics.

Figure 5.16: Metric scaler block

The rule chosen to scale the metrics explains why the state metrics have to be

represented on 8 bits: since a metric is represented on 3 bits, a transition metric (represented by 4 added metrics from the 4 received symbols) can achieve the maximal value 4*(23-1) = 28. Since the convolutional encoder has a length of K = 6, after 6 trellis steps from a given state, all other states can be reached. Hence the interval 6 ensures complete connectivity for all trellis states. An upper bound on the state metric difference can be found assuming that for one of these paths of length 6, all transition metrics are maximum and for an other one, all transition metrics are minimum: delta = K * (max(trans) – min(trans)) = 6*4*(23-1)=168.

The scaling rule adopted consists of subtracting a constant value (2048) to all

metrics each time one or several metrics overtake a threshold value (3840).

Metric scaler

64x8 metrics_to_scale

64x8scaled_metrics

5 VHDL implementation of the transmission chain 53

5.2.2.2.3 « Traceback » block

Figure 5.17: Traceback block

If the trellis is terminated, a final decision on the overall best path is possible only

at the very end of the trellis. However, in broadcasting applications a continuous sequence of information bits has to be decoded rather than a terminated sequence, i.e. we have no known start and end states. Fortunately, certain asymptotic properties allow approximate maximum likelihood sequence estimation with negligible performance losses and limited implementation effort. The paths trajectories of the trellis merge, when traced back over time, into a single path as shown in Figure 5.18. This path is called the final survivor path. For trellis steps smaller than k-D, the paths have merged into the final survivor with very high probability. The survivor depth D, which guarantees this behavior, depends strongly on the used code. For our case it can be shown that a D = 6*(Encoder constraint length) is optimal. Thus, D is chosen equal to 42.

Figure 5.18: Path trajectories for the Viterbi algorithm

The traceback block (Figure 5.17) must find the transition in the trellis, 42 steps

before this state. The difficulty in this block is to memorize, for each of the 64 states, the most probable path on 42 steps. And this path has to be reconstructed at each step.

Traceback_RAM

CLK

4selected_transition

enable_in

enable_out

selected_transitions 64x3

5 VHDL implementation of the transmission chain 54

At a given time, the traceback receives 64 states (on 3 bits) preceding each present state in the trellis: this corresponds to the transitions in the trellis. The output of this block then delivers the selected transition 42 steps before. « LIFO » block

Figure 5.19: LIFO block

Trellis is decoded in reverse order during the data traceback stage, thus a last-in

first-out (LIFO) memory of the length of the traceback depth is required for reversing the order before outputting the codewords. This will be implemented with a RAM and an address counter from 0 to the traceback depth. 5.2.3 Demapper

Figure 67 depicts the general structure of the “demapping” block. The output of the block delivers a 9-bit word as shown in figure 68. First the “auxiliary trellis”, from paragraph 3.5, will be used to demap the selected transition and then it will resolve the mapping equation of paragraph 3.3 to recover the output word.

16

selected_transition

vect_dec

vect_decm

enable_out enable_in

16

out_word 8

CLK

Demapper

4

4

selected_transition_in

4

selected_transition_out

LIFO

5 VHDL implementation of the transmission chain 55

5.2.4 Differential decoder The differential decoder (Figure 5.20) presents no particular difficulty: it simply does the inverse operation of the differential encoder. Only bits 1, 5 and 8 (see paragraph 3.4) are affected by this operation.

Figure 5.20: Structure of the differential decoder

5.3 Channel Simulator

Channel simulator simulates an AWGN channel in the transmission chain. As FPGA can not generate a random number, this block is a large RAM table containing noise values. These values are previously computed with matlab for the requested variance and then load into the RAM.

in_diff_dec 8

CLK

enable_in enable_out

8out_diff_dec

Diff_decoder

I0 - Q0 2*6

I3 – Q3 2*6

I0 - Q0 2*6

I3 – Q3 2*6

Channel

Simulator

enable_out

CLK

enable_in

enable_noise

5 VHDL implementation of the transmission chain 56

5.4 Global simulation chain